# An Automated OpenCL FPGA Compilation Framework Targeting a Configurable, VLIW Chip Multiprocessor

by Samuel Jon Parker

## A Doctoral Thesis

Submitted in partial fulfilment of the requirements for the award of Doctor of Philosophy of Loughborough University

$\bigodot$  Samuel Jon Parker 2015

August 2015

# Abstract

Modern system-on-chips augment their baseline CPU with coprocessors and accelerators to increase overall computational capacity and power efficiency, and thus have evolved into heterogeneous systems. Several languages have been developed to enable this paradigm shift, including CUDA and OpenCL. This thesis discusses a unified compilation environment to enable heterogeneous system design through the use of OpenCL and a customised VLIW chip multiprocessor (CMP) architecture, known as the LE1. An LLVM compilation framework was researched and a prototype developed to enable the execution of OpenCL applications on the LE1 CPU. The framework fully automates the compilation flow and supports work-item coalescing to better utilise the CPU cores and alleviate the effects of thread divergence. This thesis discusses in detail both the software stack and target hardware architecture and evaluates the scalability of the proposed framework on a highly precise cycle-accurate simulator. This is achieved through the execution of 12 benchmarks across 240 different machine configurations, as well as further results utilising an incomplete development branch of the compiler. It is shown that the problems generally scale well with the LE1 architecture, up to eight cores, when the memory system becomes a serious bottleneck. Results demonstrate superlinear performance on certain benchmarks (x9 for the bitonic sort benchmark with 8 dual-issue cores) with further improvements from compiler optimisations (x14 for bitonic with the same configuration).

# Acknowledgements

Firstly I would like to thank my parents and grandparents for all their love and support (mentally, physically and financially) as I would have achieved nothing without you. You always nurtured my will to *'vestigate* and this has definitely been my biggest investigation to date!

My thanks also goes to my supervisors Dr. Vassilios Chouliaras and Dr. David Mulvaney for their guidance through my PhD and tuition during my undergraduate studies. Especially to Dr. Chouliaras whose undergradute project on his VLIW architecture gave me the opportunity to begin my adventures into compiler technology which continued into this research, and for his continued encouragement, guidance and patience. My gratitude also goes to Dr. Stevens who developed, and promptly provided bug fixes for, the simulator and assembler that I used to collect experimental data; and for his help and advice, particularly at the start of this research.

I would also like to thank the School of Electronic, Electrical and Systems Engineering at Loughborough for the opportunity and funding which made my PhD possible.

Finally I would like to thank the hundreds of developers that have worked on open source tools that I have used throughout this PhD, particularly to those who have contributed to the linux kernel, Debian, Ubuntu, Vim, Git, GDB and Clang/LLVM. Special thanks for anyone who has offered help and suggestions on the cfe-dev and llvm-dev mailing lists.

## CONTENTS

# Contents

| Ab             | ostra | ict i                                   |

|----------------|-------|-----------------------------------------|

| Ac             | kno   | wledgements i                           |

| $\mathbf{Lis}$ | st of | Figures vi                              |

| $\mathbf{Lis}$ | st of | Tables xii                              |

| Gl             | ossa  | ry xiii                                 |

| 1              | Intr  | roduction 1                             |

|                | 1.1   | Problem Formulation                     |

|                | 1.2   | Aims and Objectives                     |

|                | 1.3   | Outline of Areas of Research            |

|                |       | 1.3.1 Parallelism                       |

|                |       | 1.3.2 Compilers                         |

|                |       | 1.3.3 Heterogeneous Computing           |

|                | 1.4   | Contributions of Thesis                 |

|                | 1.5   | Thesis Outline                          |

| <b>2</b>       | Par   | allel Computer Architectures 8          |

|                | 2.1   | Chapter Objectives                      |

|                | 2.2   | Architecture Styles and Features        |

|                |       | 2.2.1 Memory Hierachy                   |

|                |       | 2.2.2 Superscalar Execution             |

|                |       | 2.2.3 Vector Processing 11              |

|                |       | 2.2.4 Multiple Threads                  |

|                | 2.3   | Very Long Instruction Word Architecture |

|                |       | 2.3.1 Philosophy 18                     |

|   |      | 2.3.2    | History and Evolution                                                                                                                       | 19         |

|---|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   |      | 2.3.3    | Modern Implementations and Applications                                                                                                     | 23         |

|   | 2.4  | Hetero   | geneous Computing Architectures                                                                                                             | 27         |

|   |      | 2.4.1    | Graphics Processing Units                                                                                                                   | 28         |

|   |      | 2.4.2    | Many-core Accelerators                                                                                                                      | 30         |

|   |      | 2.4.3    | Field Programmable Gate Arrays                                                                                                              | 32         |

|   | 2.5  | Hardw    | are / Software Codesign                                                                                                                     | 35         |

|   |      | 2.5.1    | ASICs and FPGAs                                                                                                                             | 35         |

|   |      | 2.5.2    | Application-Specific Instruction-set Processors                                                                                             | 36         |

|   |      | 2.5.3    | Codesign for Supercomputers                                                                                                                 | 37         |

|   | 2.6  | Discus   | $sion \ldots \ldots$ | 38         |

|   | 2.7  | Summ     | ary $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                            | 40         |

| 3 | Dar  | allal D  | rogramming                                                                                                                                  | 41         |

| U | 3.1  |          |                                                                                                                                             | <b>4</b> 1 |

|   | 3.2  | -        | •                                                                                                                                           | 41         |

|   | 0.2  | 3.2.1    |                                                                                                                                             | 42         |

|   |      | 3.2.2    | -                                                                                                                                           | 43         |

|   |      | 3.2.3    | Types of Compilation                                                                                                                        | 45         |

|   | 3.3  | Compi    | ling for VLIWs                                                                                                                              | 47         |

|   |      | 3.3.1    | Region Formation                                                                                                                            | 47         |

|   |      | 3.3.2    | Scheduling                                                                                                                                  | 52         |

|   | 3.4  | Langu    | ages and Platforms                                                                                                                          | 56         |

|   |      | 3.4.1    | Traditional Methods                                                                                                                         | 56         |

|   |      | 3.4.2    | Programming for Heterogeneous Systems                                                                                                       | 58         |

|   |      | 3.4.3    | OpenCL Compilation                                                                                                                          | 63         |

|   | 3.5  | Discus   | $\operatorname{sion}$                                                                                                                       | 68         |

|   | 3.6  | Summ     | ary                                                                                                                                         | 69         |

| 4 | Ideı | ntificat | ion of Research Area                                                                                                                        | 70         |

|   | 4.1  |          |                                                                                                                                             | 70         |

|   | 4.2  |          |                                                                                                                                             | 70         |

|   | 4.3  |          |                                                                                                                                             | 71         |

|   | 4.4  | Summ     | ary                                                                                                                                         | 72         |

| 5 | The  | LE1 C    | Compiler                                                                                                                                    | 74         |

| - | 5.1  |          | -                                                                                                                                           | 74         |

|   | 5.2  | -        | •                                                                                                                                           | 74         |

|   | 0.2  | muu      |                                                                                                                                             | • •        |

|   |                                                                             | 5.2.1 Program Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                             | 5.2.2 TableGen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 5.3                                                                         | Instruction Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                                                                             | 5.3.1 Instruction Legalisation and Lowering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                             | 5.3.2 Instruction Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 5.4                                                                         | Instruction Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |                                                                             | 5.4.1 Stable Branch $\ldots \ldots $ 91                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                                                                             | 5.4.2 Development Branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 5.5                                                                         | Register Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                             | 5.5.1 Register Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 5.6                                                                         | Instruction Packing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                             | 5.6.1 Stable Branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                             | 5.6.2 Development Branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 5.7                                                                         | Code Emission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 5.8                                                                         | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 5.9                                                                         | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6 | The                                                                         | e LE1 OpenCL Driver 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0 | 6.1                                                                         | Chapter Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 0.1                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 62                                                                          | Client Driver 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 6.2                                                                         | Client Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 6.2                                                                         | 6.2.1 API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 6.2                                                                         | 6.2.1       API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | -                                                                           | 6.2.1       API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 6.3                                                                         | 6.2.1       API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | -                                                                           | 6.2.1       API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 6.3                                                                         | 6.2.1       API       103         6.2.2       Core       103         6.2.3       Device       103         Source-to-Source Transformation       104         Runtime Support       111         6.4.1       Builtin Functions       111                                                                                                                                                                                                                                                                                                          |

|   | 6.3                                                                         | 6.2.1       API       103         6.2.2       Core       103         6.2.3       Device       103         Source-to-Source Transformation       103         Runtime Support       104         6.4.1       Builtin Functions       111         6.4.2       Softfloat       111                                                                                                                                                                                                                                                                  |

|   | 6.3                                                                         | 6.2.1       API       103         6.2.2       Core       103         6.2.3       Device       103         Source-to-Source Transformation       104         Runtime Support       111         6.4.1       Builtin Functions       111         6.4.2       Softfloat       111         6.4.3       Kernel Launching       112                                                                                                                                                                                                                   |

|   | 6.3                                                                         | 6.2.1       API       103         6.2.2       Core       103         6.2.3       Device       103         Source-to-Source Transformation       104         Runtime Support       104         6.4.1       Builtin Functions       111         6.4.2       Softfloat       111         6.4.3       Kernel Launching       112         6.4.4       Data Transfer       113                                                                                                                                                                       |

|   | 6.3<br>6.4                                                                  | 6.2.1       API       103         6.2.2       Core       103         6.2.3       Device       103         Source-to-Source Transformation       104         Runtime Support       104         6.4.1       Builtin Functions       111         6.4.2       Softfloat       111         6.4.3       Kernel Launching       115         6.4.4       Data Transfer       115         6.4.5       Simulation       115                                                                                                                              |

|   | <ul><li>6.3</li><li>6.4</li><li>6.5</li></ul>                               | 6.2.1       API       103         6.2.2       Core       103         6.2.3       Device       103         Source-to-Source Transformation       106         Runtime Support       111         6.4.1       Builtin Functions       111         6.4.2       Softfloat       111         6.4.3       Kernel Launching       111         6.4.4       Data Transfer       113         6.4.5       Simulation       114         Contributions       114                                                                                              |

|   | 6.3<br>6.4                                                                  | 6.2.1       API       103         6.2.2       Core       103         6.2.3       Device       103         Source-to-Source Transformation       104         Runtime Support       104         6.4.1       Builtin Functions       111         6.4.2       Softfloat       111         6.4.3       Kernel Launching       115         6.4.4       Data Transfer       115         6.4.5       Simulation       115                                                                                                                              |

| 7 | <ul> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul>              | 6.2.1       API       103         6.2.2       Core       103         6.2.3       Device       103         Source-to-Source Transformation       106         Runtime Support       111         6.4.1       Builtin Functions       111         6.4.2       Softfloat       111         6.4.3       Kernel Launching       111         6.4.4       Data Transfer       113         6.4.5       Simulation       114         Contributions       114                                                                                              |

| 7 | <ul> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul>              | 6.2.1       API       103         6.2.2       Core       103         6.2.3       Device       103         Source-to-Source Transformation       106         Runtime Support       111         6.4.1       Builtin Functions       111         6.4.2       Softfloat       111         6.4.3       Kernel Launching       112         6.4.4       Data Transfer       113         6.4.5       Simulation       113         Summary       114                                                                                                    |

| 7 | <ul> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>Exp</li> </ul> | 6.2.1       API       103         6.2.2       Core       103         6.2.3       Device       103         Source-to-Source Transformation       106         Runtime Support       106         Runtime Support       111         6.4.1       Builtin Functions       111         6.4.2       Softfloat       111         6.4.3       Kernel Launching       111         6.4.4       Data Transfer       113         6.4.5       Simulation       113         Summary       116       116         Periments       117                            |

| 7 | <ul> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>Exp</li> </ul> | 6.2.1       API       103         6.2.2       Core       103         6.2.3       Device       103         Source-to-Source Transformation       104         Runtime Support       106         Runtime Support       111         6.4.1       Builtin Functions       111         6.4.2       Softfloat       111         6.4.3       Kernel Launching       111         6.4.4       Data Transfer       113         6.4.5       Simulation       114         Summary       116         veriments       117         Chapter Objectives       117 |

|              | 7.2            | Benchmarks                                                                                                    | 118 |

|--------------|----------------|---------------------------------------------------------------------------------------------------------------|-----|

|              | 7.3            | Machine Configurations                                                                                        | 120 |

|              | 7.4            | Results                                                                                                       | 121 |

|              |                | 7.4.1 ILP Performance                                                                                         | 121 |

|              |                | 7.4.2 TLP Performance                                                                                         | 132 |

|              |                | 7.4.3 Development Branch                                                                                      | 141 |

|              | 7.5            | Summary                                                                                                       | 154 |

| 8            | Con            | clusion                                                                                                       | 157 |

|              | 8.1            | Chapter Objectives                                                                                            | 157 |

|              | 8.2            | Summary of Thesis Objectives                                                                                  | 157 |

|              | 8.3            | Contributions                                                                                                 | 158 |

|              | 8.4            | Findings                                                                                                      | 160 |

|              |                | 8.4.1 Single Program, Multiple Data                                                                           | 160 |

|              |                | 8.4.2 Very Long Instruction Word Processor                                                                    | 160 |

|              |                | 8.4.3 Towards Heterogeneous Computing                                                                         | 161 |

|              | 8.5            | ${\rm Limitations \ of \ Research}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 161 |

|              | 8.6            | Further Research                                                                                              | 162 |

| Re           | efere          | nces                                                                                                          | 164 |

| Pι           | ıblica         | ations                                                                                                        | 181 |

| A            | Sou            | rce Code Repository                                                                                           | 183 |

| в            | Con            | npiler and Simulator Target Generator Script                                                                  | 184 |

| $\mathbf{C}$ | $\mathbf{Res}$ | ults                                                                                                          | 190 |

| D            | Con            | nplete Results from Experiments                                                                               | 204 |

# List of Figures

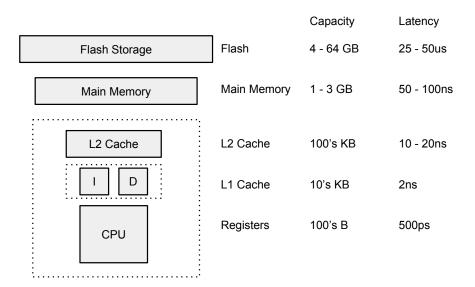

| 2.1  | Memory hierachy in a modern smartphone                                                   | 9  |

|------|------------------------------------------------------------------------------------------|----|

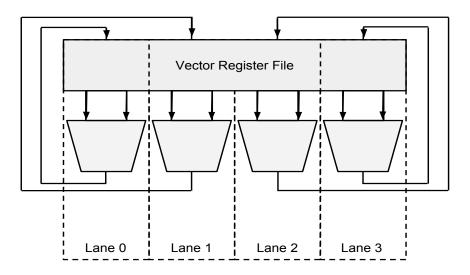

| 2.2  | Vector pipeline and register file with four lanes                                        | 12 |

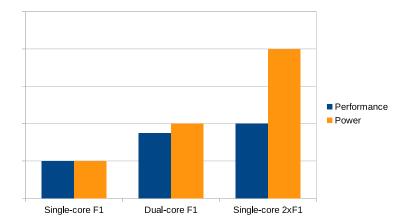

| 2.3  | Power and performance ratio between doubling the cores and doubling the                  |    |

|      | frequency                                                                                | 13 |

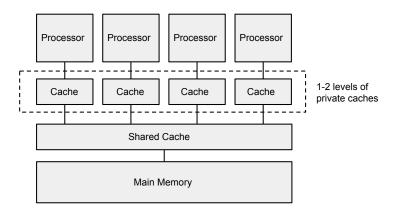

| 2.4  | Cache Hierachy in a chip-multiprocessor                                                  | 15 |

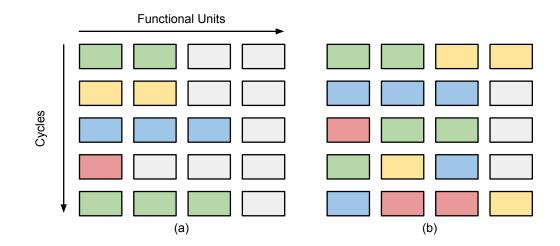

| 2.5  | Processor utilisation with 4-way (a) fine-grained ( <i>vertical</i> ) multithreading and |    |

|      | (b) simultaneous multithreading ( <i>horizontal</i> ), with the four threads in differ-  |    |

|      | ent colours                                                                              | 16 |

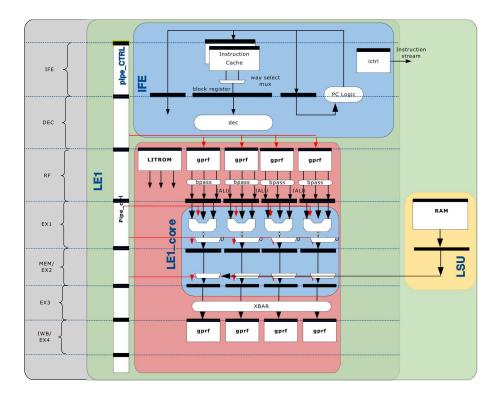

| 2.6  | Components and pipeline of a 4-wide, single-core LE1                                     | 26 |

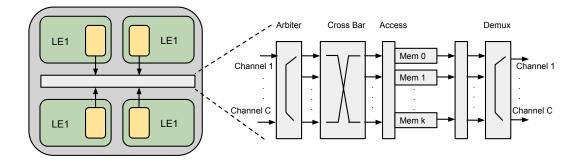

| 2.7  | Quad-core LE1 with connecting memory system.                                             | 27 |

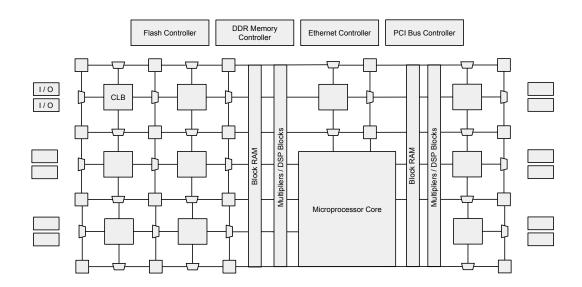

| 2.8  | Internal components of an FPGA.                                                          | 33 |

| ~ .  |                                                                                          |    |

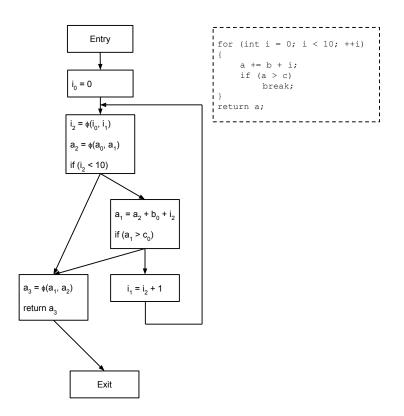

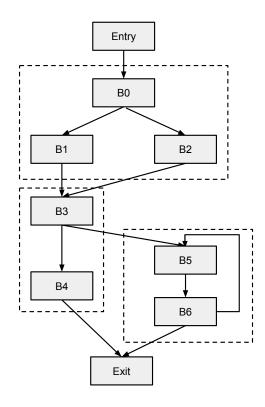

| 3.1  | Example of <i>Single Static Assignment</i> (SSA) form                                    | 43 |

| 3.2  | Extended Basic Block Formation with the EBBs shown within the dashed lines.              |    |

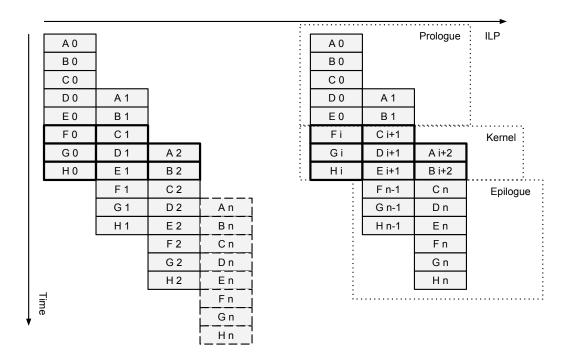

| 3.3  | Illustrated concept of software pipelining                                               | 54 |

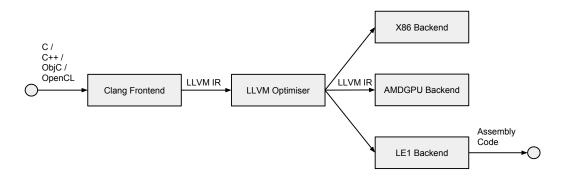

| 5.1  | Three phase compilation with Clang and LLVM.                                             | 75 |

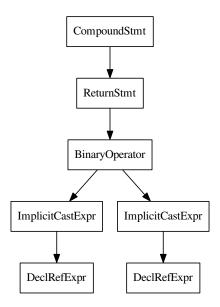

| 5.2  | Graphical example of an AST produced by Clang                                            | 76 |

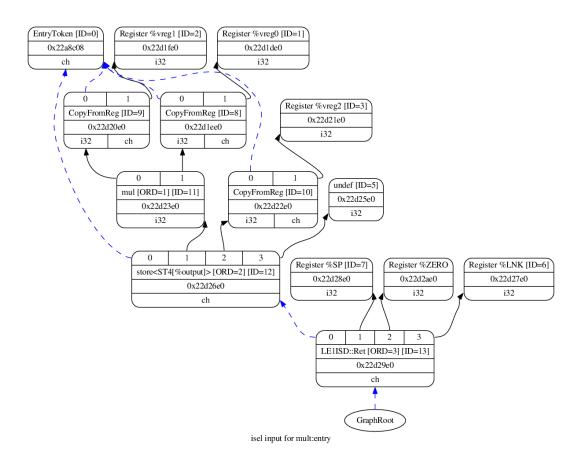

| 5.3  | Example of a SelectionDAG after target lowering and legalisation                         | 81 |

| 5.4  | Code that informs the legalisation process which types are supported by each             |    |

|      | operation and in which registers the types can reside                                    | 83 |

| 5.5  | Calling convention definitions for the LE1                                               | 84 |

| 5.6  | SDNode definition for ADDCG and DIVS instructions                                        | 85 |

| 5.7  | Base class for instruction formats with arithmetic and logic operations defi-            |    |

|      | nitions                                                                                  | 87 |

| 5.8  | Instruction class and definition used for compare operations                             | 88 |

| 5.9  | Pattern matching of conditional branch instructions                                      | 88 |

| 5.10 | Example of pattern matching for an unsigned value.                                       | 88 |

| 5.11 | Multiplication instruction definitions and pattern matchers                          |

|------|--------------------------------------------------------------------------------------|

| 5.12 | Processor itineraries which describe pipeline usage for each type of instruction. 92 |

| 5.13 | Microarchitecture resource description and assignment to instruction types           |

|      | for use by the scheduler, in the updated compiler based on LLVM 3.4 93               |

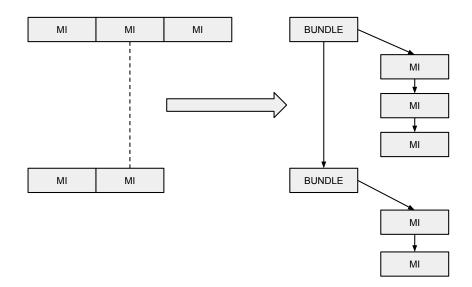

| 5.14 | Internal representation of LLVM MachineInstr with Bundles                            |

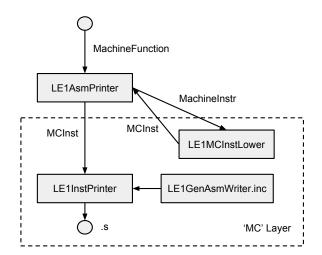

| 5.15 | Class interactive for LE1 code emission                                              |

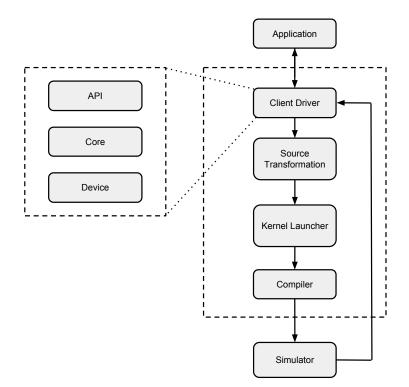

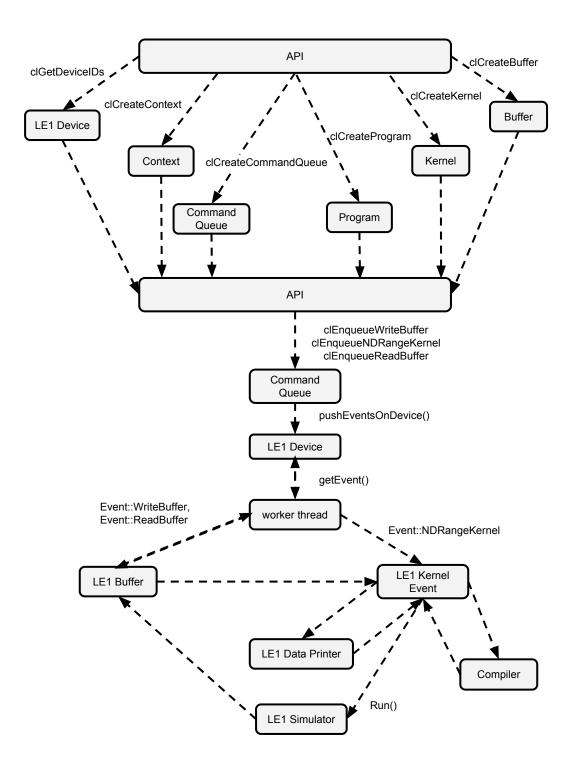

| 6.1  | Software system overview                                                             |

| 6.2  | Driver target instantiation example                                                  |

| 6.3  | Simplified relationship between the API and the objects in the 'core' and the        |

|      | 'device'                                                                             |

| 6.4  | Simple kernel coarsening algorithm                                                   |

| 6.5  | Algorithm outline for the second, and final, stage of kernel coarsening 109 $$       |

| 6.6  | Permute source code after complete transformation                                    |

| 6.7  | Kernel launcher source code for Binary Search                                        |

| 6.8  | Workgroup execution model on a 4 core system, with the workgroups num-               |

|      | bered and the different varying colours representing the separate cores 114          |

| 7.1  | Loop header for target machine generator script                                      |

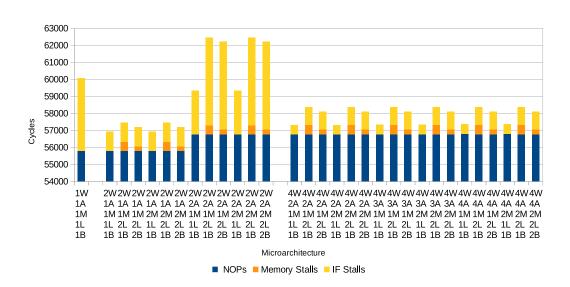

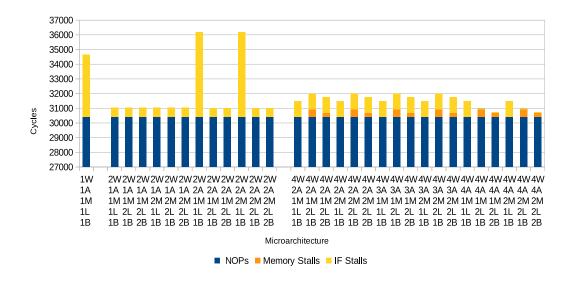

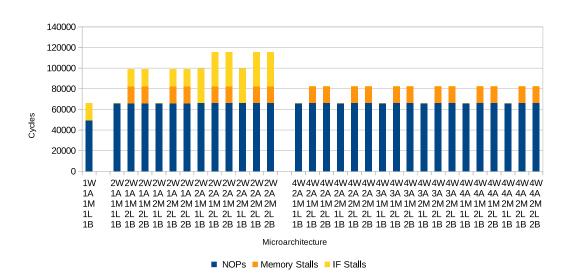

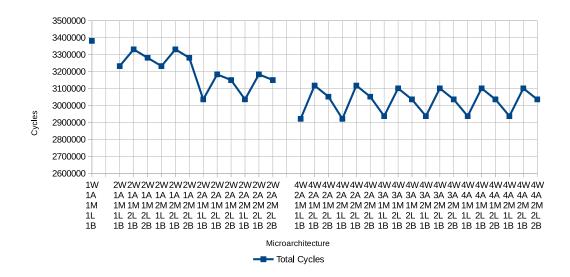

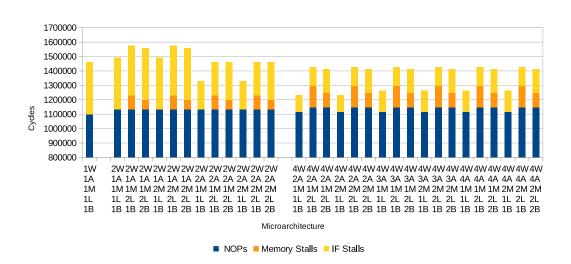

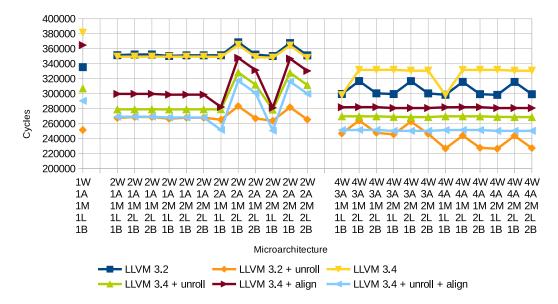

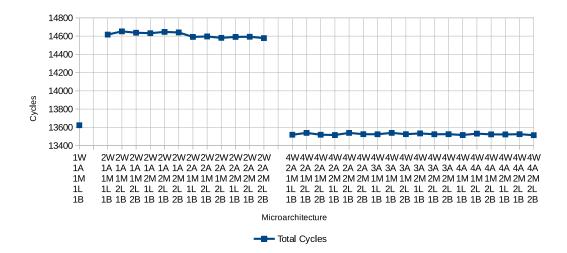

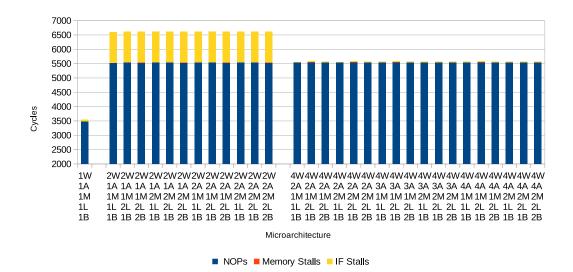

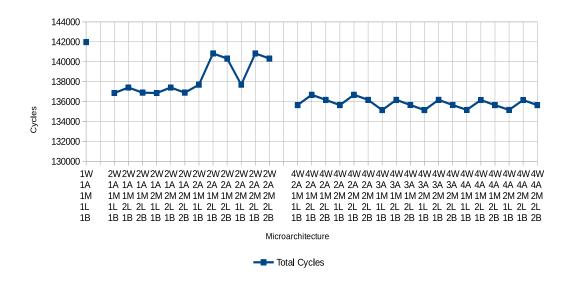

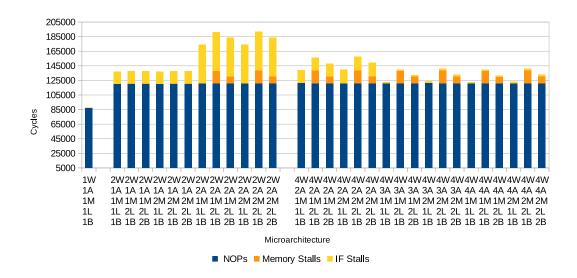

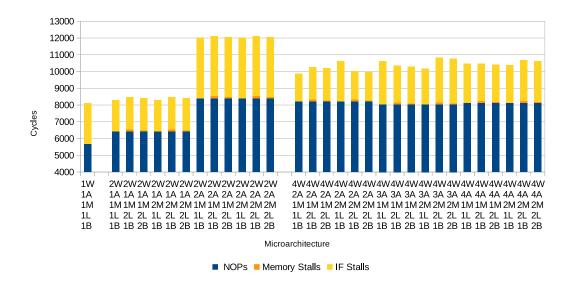

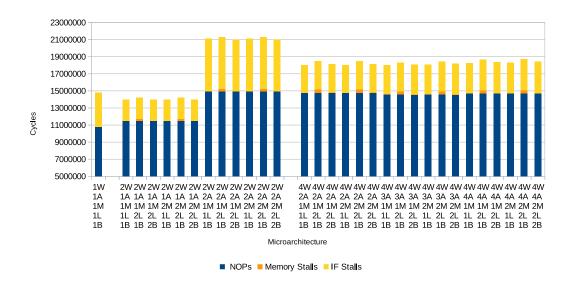

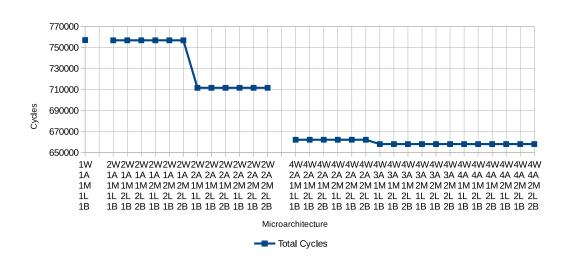

| 7.2  | Total average stalls and NOP cycles for BFS_1 using 1 context across varying         |

|      | microarchitecture configurations                                                     |

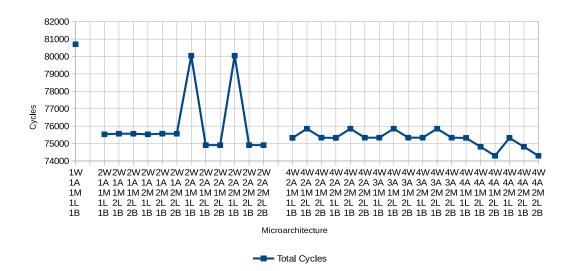

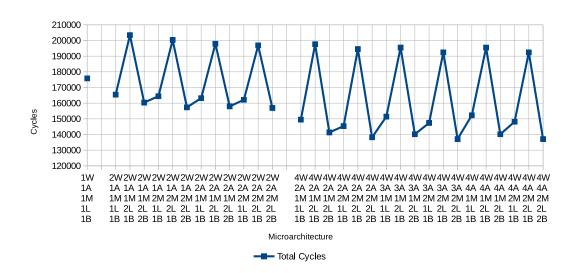

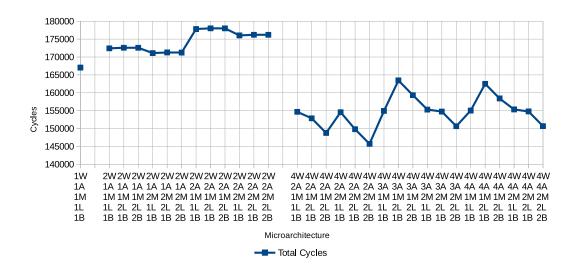

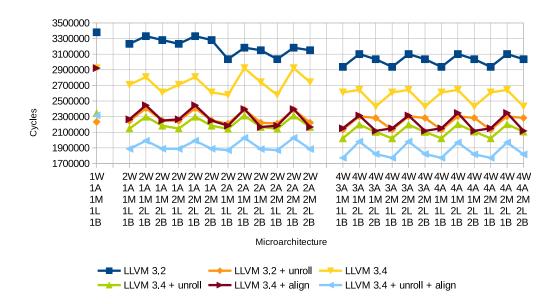

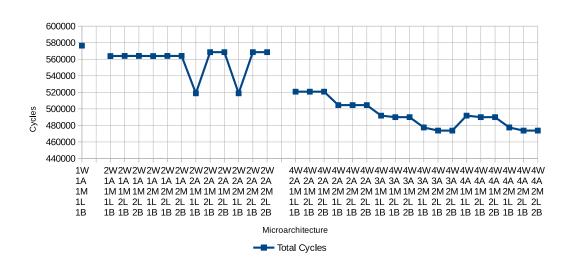

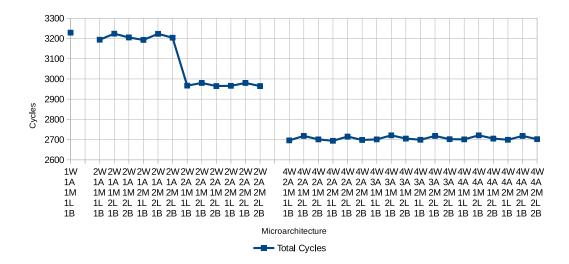

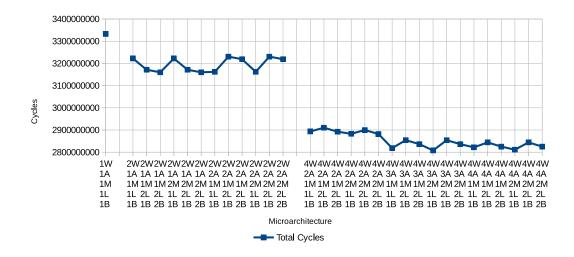

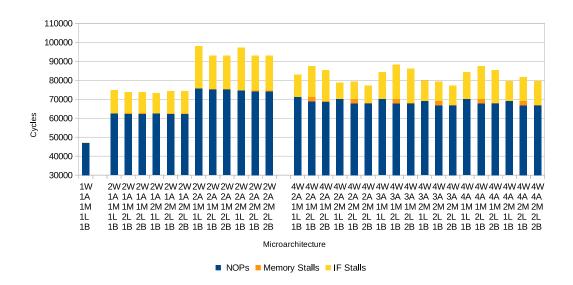

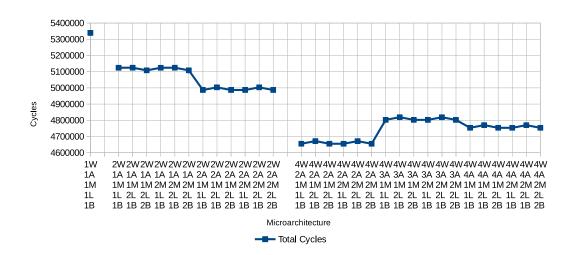

| 7.3  | Total average cycle count for BFS_2 using 1 context across varying microar-          |

|      | chitecture configurations                                                            |

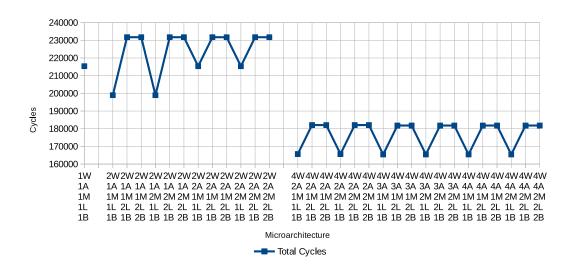

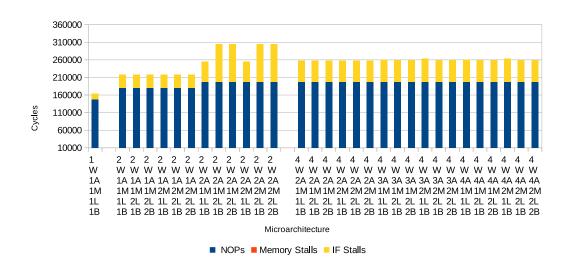

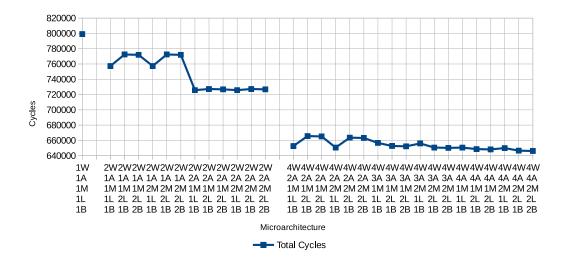

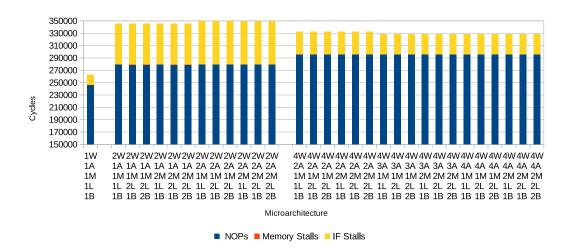

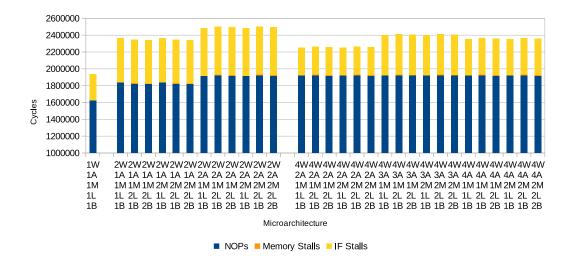

| 7.4  | Total average stalls and NOP cycles for BFS_2 using 1 context across varying         |

|      | microarchitecture configurations                                                     |

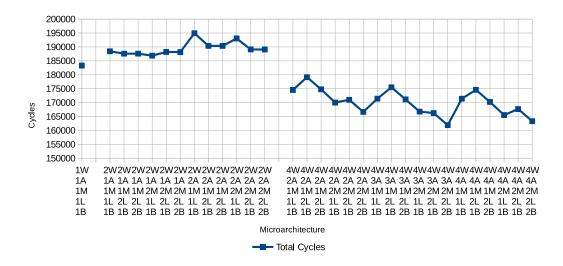

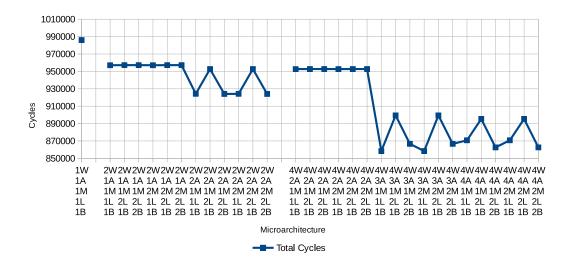

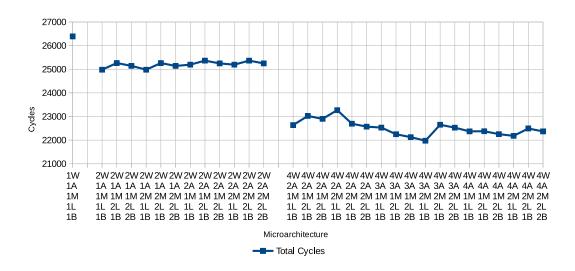

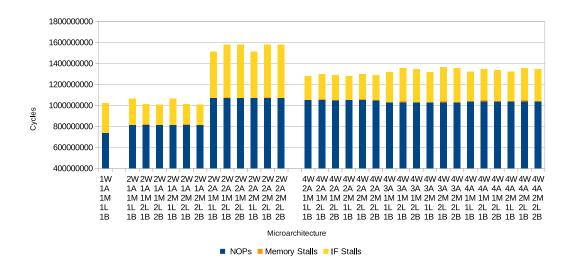

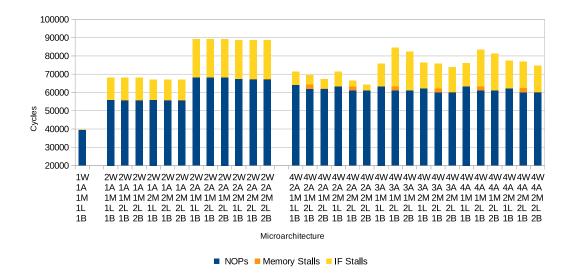

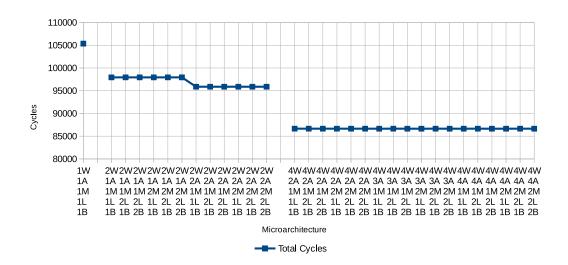

| 7.5  | Total cycle count for MatrixTranspose using 1 context across varying microar-        |

|      | chitecture configurations.                                                           |

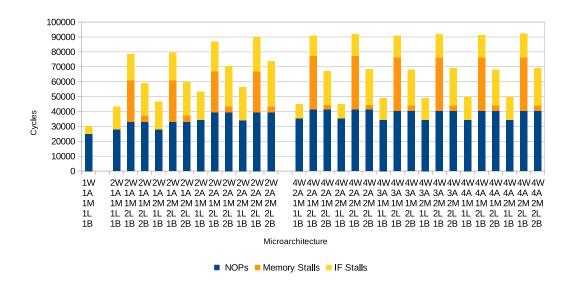

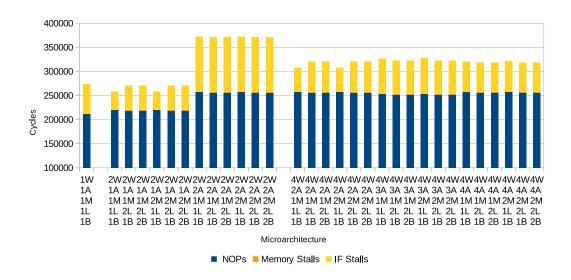

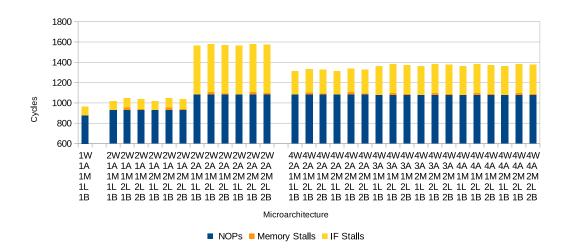

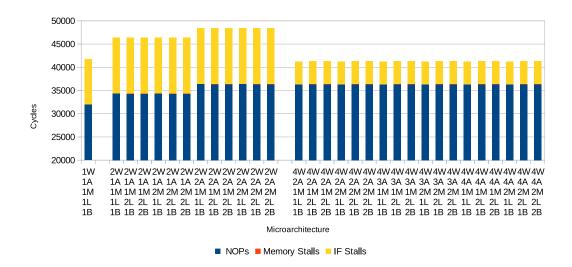

| 7.6  | Total stall and NOP cycle count for MatrixTranspose using 1 context across           |

|      | varying microarchitecture configurations                                             |

| 7.7  | Total average cycle count for nw_kernel1 from Needleman-Wunsch using 1               |

|      | context across varying microarchitecture configurations                              |

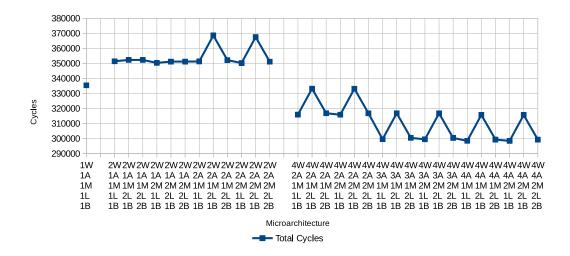

| 7.8  | Total average cycle count for nw_kernel2 from Needleman-Wunsch using $1$             |

|      | context across varying microarchitecture configurations                              |

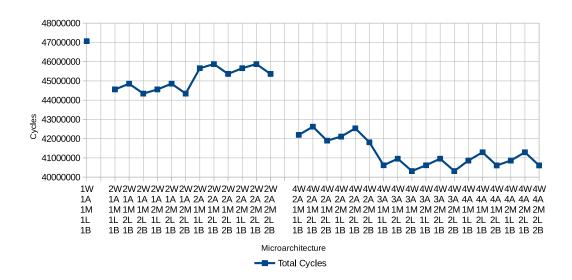

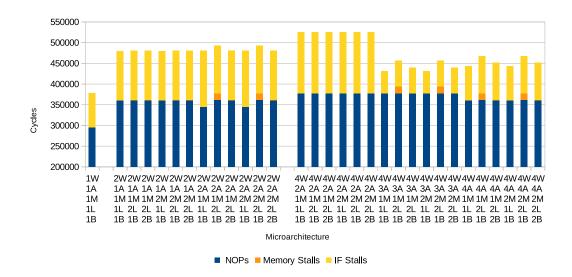

| 7.9  | Total average cycle count for FixOffset from Radix Sort using 1 context across       |

|      | varying microarchitecture configurations                                             |

| 7.10 | Total average stalls and NOP cycle count for FixOffset from Radix Sort using         |

|      | 1 context across varying microarchitecture configurations                            |

| 7.11 | Total average cycle count for histogram from Radix Sort using 1 context             |

|------|-------------------------------------------------------------------------------------|

|      | across varying microarchitecture configurations                                     |

| 7.12 | Total cycles for Reduction using 1 context across varying microarchitecture         |

|      | configurations                                                                      |

| 7.13 | Total average stalls and NOP cycle count for Reduction using 1 context across       |

|      | varying microarchitecture configurations                                            |

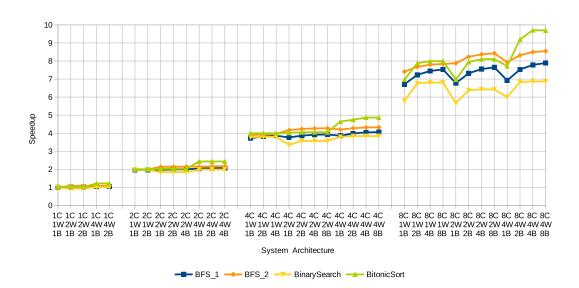

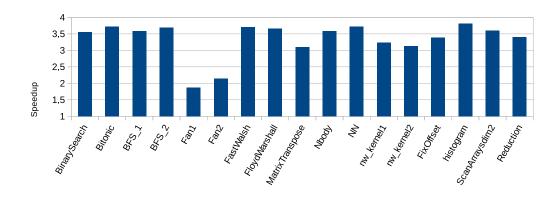

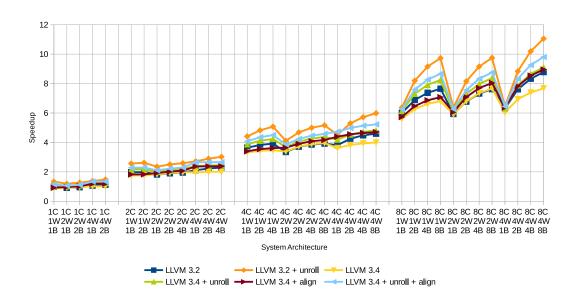

| 7.14 | Speedup of Breadth-First Search, Binary Search and Bitonic Sort across a            |

|      | selection of multi-context, maximal microarchitecture, configurations 133           |

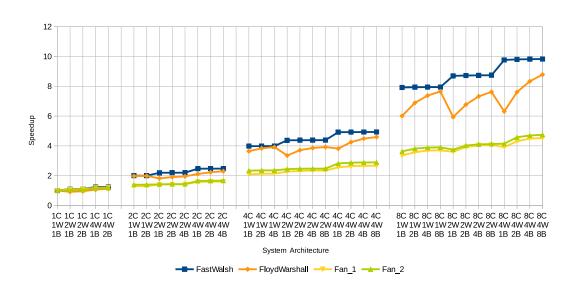

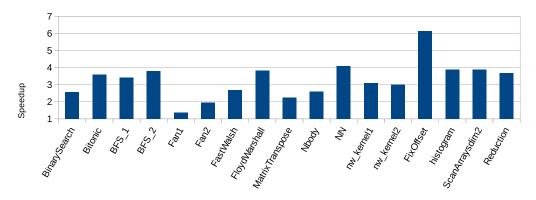

| 7.15 | Speedup of Fast Walsh Transform, Floyd Warshall and Gaussian Elimination            |

|      | across a selection of multi-context, maximal microarchitecture, configurations. 134 |

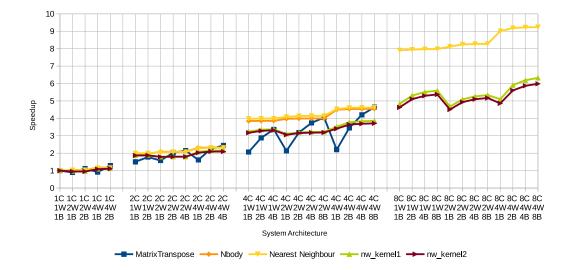

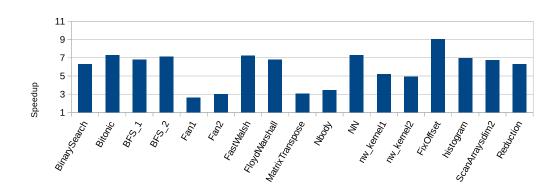

| 7.16 | Speedup of Matrix Transpose, NBody Simulation, Nearest Neighbour and                |

|      | Needleman-Wunsch across a selection of multi-context, maximal microarchi-           |

|      | tecture, configurations                                                             |

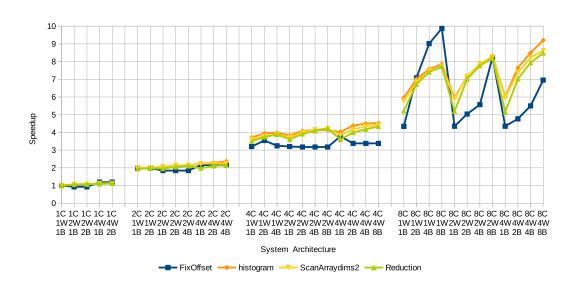

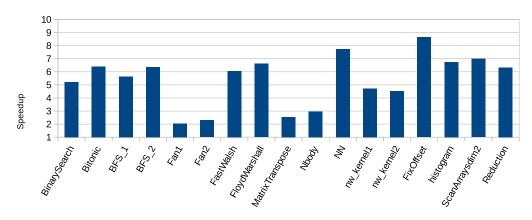

| 7.17 | Speedup of the kernels of Radix Sort and Reduction across a selection of            |

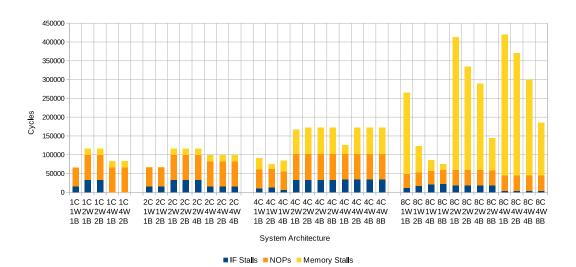

|      | multi-context, maximal microarchitecture, configurations                            |

| 7.18 | Total stalls and NOPs of FixOffset, from Radix Sort, across maximal mi-             |

|      | croarchitecture systems                                                             |

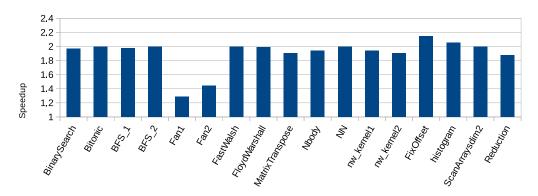

| 7.19 | Speedup of a 2W-2A-1M-1L-4B LE1 system with two contexts using silicon              |

|      | data                                                                                |

| 7.20 | Speedup of a 2W-2A-1M-1L-4B LE1 system with four contexts using silicon             |

|      | data                                                                                |

| 7.21 | Speedup of a 2W-2A-1M-1L-4B LE1 system with six contexts using silicon              |

|      | data                                                                                |

| 7.22 | Speedup of a 2W-2A-1M-1L-4B LE1 system with eight contexts using silicon            |

|      | data                                                                                |

| 7.23 | Speedup of a 2W-2A-1M-1L-4B LE1 system with ten contexts using silicon              |

|      | data                                                                                |

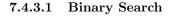

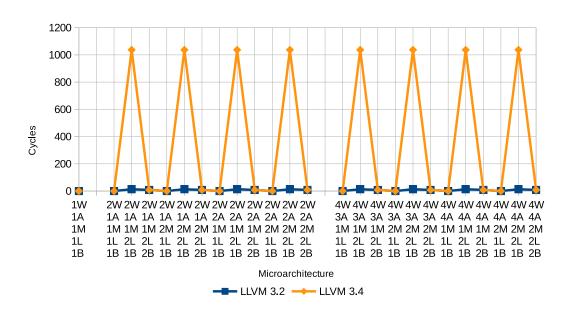

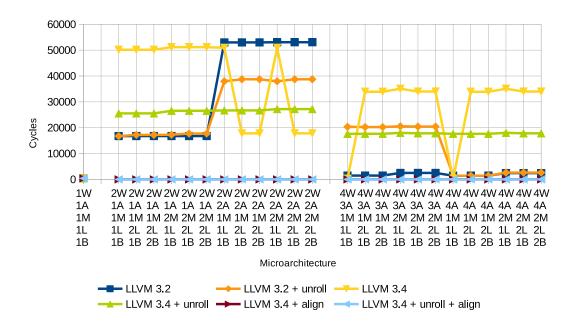

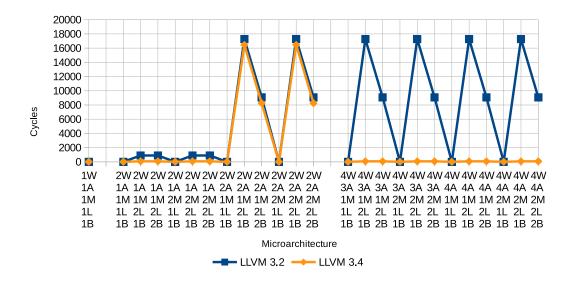

| 7.24 | Total cycles of BinarySearch, on the single CU devices, using both compilers        |

|      | and optimisations                                                                   |

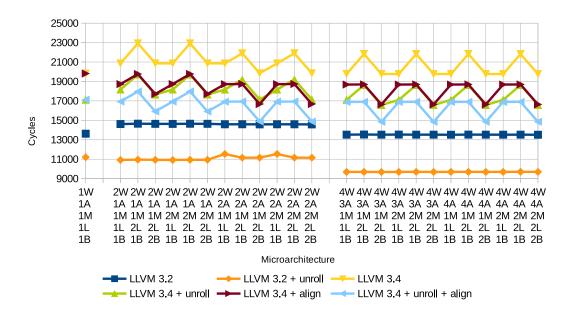

| 7.25 | Total IF stall cycles of BinarySearch, on the single CU devices, using both         |

|      | compilers and optimisations                                                         |

| 7.26 | Total memory stall cycles of BinarySearch, on the single CU devices, using          |

|      | both compilers                                                                      |

| 7.27 | Total NOP cycles of BinarySearch, on the single CU devices, using both              |

|      | compilers                                                                           |

| 7.28 | Speedup of BinarySearch, relative to a single CU ,scalar device, and LLVM           |

|      | 3.2, across the maximal microarchitecture configurations. $\ldots$                  |

### LIST OF FIGURES

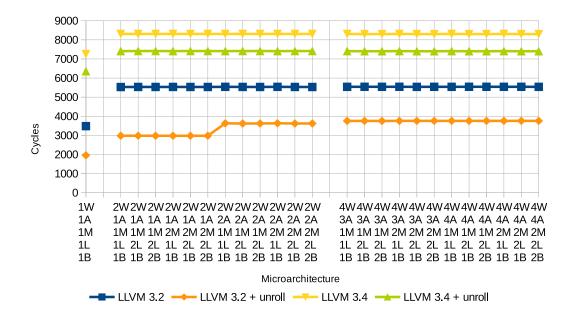

| 7.29 | Total average cycles of Bitonic Sort, on the single CU devices, using both      |

|------|---------------------------------------------------------------------------------|

|      | compilers and varying optimisations                                             |

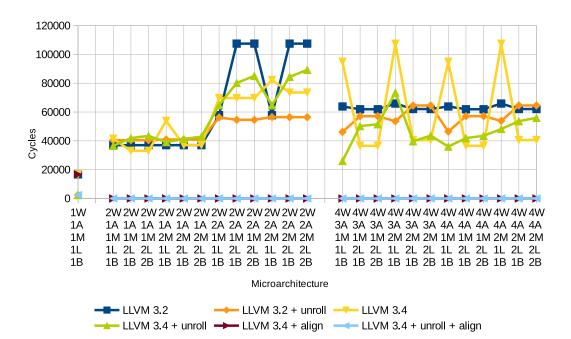

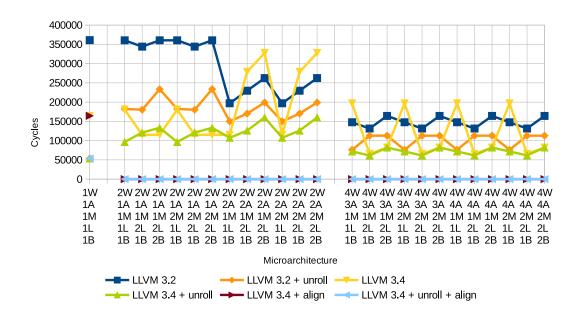

| 7.30 | IF stalls of Bitonic Sort                                                       |

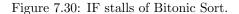

| 7.31 | Memory stalls of Bitonic Sort across maximal microarchictectures with dif-      |

|      | ferent compiler backends                                                        |

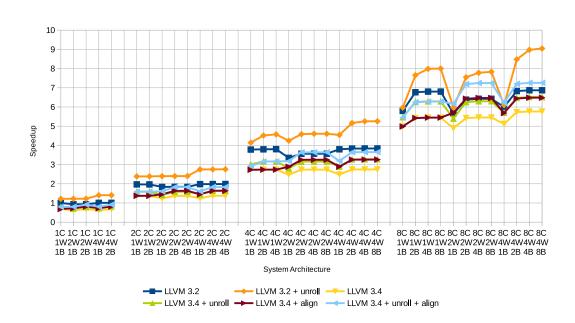

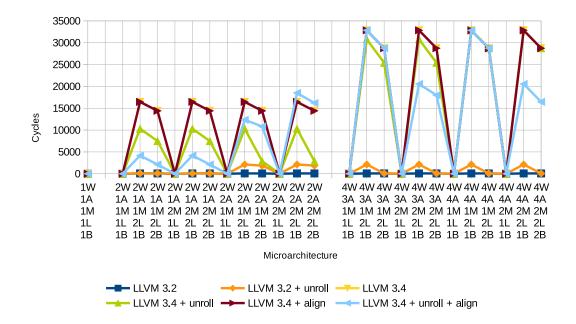

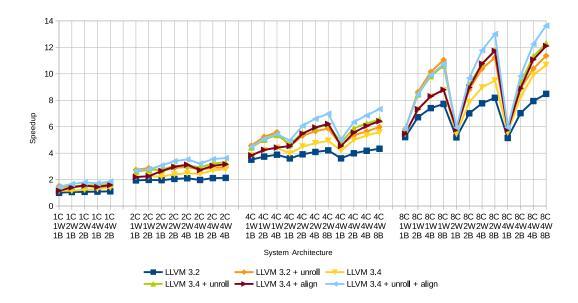

| 7.32 | Speedup of Bitonic Sort, relative to a scalar device with LLVM 3.2, across      |

|      | multi-context, maximal microarchitecture, devices, using both compilers and     |

|      | varying optimisations                                                           |

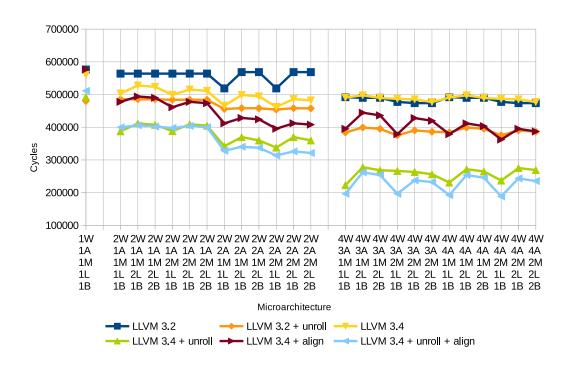

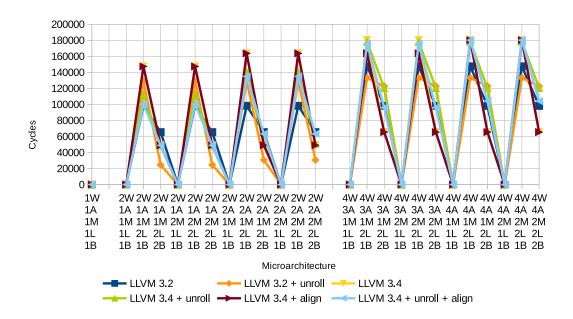

| 7.33 | Total average cycles for FloydWarshall using the different compilers and op-    |

|      | timisations, for the single CU devices                                          |

| 7.34 | Total average IF stalls of FloydWarshall for the single CU devices, using both  |

|      | the compiler backends                                                           |

| 7.35 | Total average memory stalls of FloydWarshall for the single CU devices, using   |

|      | both the compiler backends                                                      |

| 7.36 | Speedup, with respect to a scalar device and LLVM 3.2, for FloydWarshall us-    |

|      | ing different compilers and optimisations across multi-CU systems of maximal    |

|      | microarchitecture configurations                                                |

| 7.37 | Total average cycles for Reduction using LLVM 3.2 and loop unrolling 152        |

| 7.38 | Total average IF stall cycles for Reduction on the single CU devices using      |

|      | both compilers and optimisations                                                |

| 7.39 | Total average memory stall cycles for Reduction on the single CU devices        |

|      | using both compilers and optimisations                                          |

| 7.40 | Speedup, relative to a scalar device with LLVM 3.2, of Reduction on the         |

|      | single CU devices with maximal microarchitectures using both compilers and      |

|      | optimisations                                                                   |

| C.1  | Total cycles for BinarySearch using 1 context across varying microarchitecture  |

|      | configurations                                                                  |

| C.2  | Total IF stall cycles for BinarySearch using 1 context across varying microar-  |

|      | chitecture configurations                                                       |

| C.3  | Total average cycle count for BitonicSort using 1 context across varying mi-    |

|      | croarchitecture configurations                                                  |

| C.4  | Total average IF stall cycle count for BitonicSort using 1 context across vary- |

|      | ing microarchitecture configurations                                            |

| C.5  | Total average cycle count for $BFS_1$ using 1 context across varying microar-   |

|      | chitecture configurations                                                       |

х

### LIST OF FIGURES

| C.6  | Total cycles for FastWalshTransform using 1 context across varying microar-                                          |     |

|------|----------------------------------------------------------------------------------------------------------------------|-----|

|      | chitecture configurations.                                                                                           | 193 |

| C.7  | Total stalls and NOP cycles for FastWalshTransform using 1 context across                                            |     |

|      | varying microarchitecture configurations.                                                                            | 193 |

| C.8  | Total cycles for FloydWarshall using 1 context across varying microarchitec-                                         |     |

|      | ture configurations.                                                                                                 | 194 |

| C.9  | Total stall and NOP cycles for FloydWarshall using 1 context across varying                                          |     |

|      | microarchitecture configurations.                                                                                    | 194 |

| C.10 | Total average cycles for Fan1 of Gaussian Elimination using 1 context across                                         |     |

|      | varying microarchitecture configurations                                                                             | 195 |

| C.11 | Total average stalls and NOP cycles for Fan1 of Gaussian Elimination using                                           |     |

|      | 1 context across varying microarchitecture configurations                                                            | 195 |

| C.12 | Total average cycles for Fan2 of Gaussian Elimination using 1 context across                                         |     |

|      | varying microarchitecture configurations                                                                             | 196 |

| C.13 | Total average stalls and NOP cycles for Fan2 of Gaussian Elimination using                                           |     |

|      | 1 context across varying microarchitecture configurations                                                            | 196 |

| C.14 | Total cycle count for NBody using 1 context across varying microarchitecture                                         |     |

|      | configurations.                                                                                                      | 197 |

| C.15 | Total stall and NOP count for NBody using 1 context across varying microar-                                          |     |

|      | chitecture configurations. $\ldots$ | 197 |

| C.16 | Total cycle count for Nearest Neighbour using 1 context across varying mi-                                           |     |

|      | croarchitecture configurations                                                                                       | 198 |

| C.17 | Total stall and NOP cycle count for Nearest Neighbour using 1 context across                                         |     |

|      | varying microarchitecture configurations                                                                             | 198 |

| C.18 | Total average stall and NOP cycle count for nw_kernel1 from Needleman-                                               |     |

|      | Wunsch using 1 context across varying microarchitecture configurations                                               | 199 |

| C.19 | Total average stall and NOP cycle count for nw_kernel2 from Needleman-                                               |     |

|      | Wunsch using 1 context across varying microarchitecture configurations                                               | 199 |

| C.20 | Total average stalls and NOP cycle count for histogram from Radix Sort using                                         |     |

|      | 1 context across varying microarchitecture configurations                                                            | 200 |

| C.21 | Total average cycle count for permute from Radix Sort using 1 context across                                         |     |

|      | varying microarchitecture configurations                                                                             | 200 |

| C.22 | Total average stalls and NOP cycle count for permute from Radix Sort using                                           |     |

|      | 1 context across varying microarchitecture configurations                                                            | 201 |

| C.23 | Total average cycle count for ScanArraysdim1 from Radix Sort using 1 context                                         |     |

|      | across varying microarchitecture configurations.                                                                     | 201 |

# List of Tables

| 2.1 | Architecture Comparison between NVIDIA Kepler and Maxwell 29                         |

|-----|--------------------------------------------------------------------------------------|

| 2.2 | Feature Set of Xilinx Virtex UltraScale Product Series                               |

| 3.1 | Modulo scheduling example                                                            |

| 3.2 | CUDA and OpenCL naming conventions                                                   |

| 5.1 | LE1 Arithmetic Operations                                                            |

| 5.2 | LE1 Control Operations                                                               |

| 5.3 | LE1 Memory Operations                                                                |

| 5.4 | LE1 Multiplication Operations                                                        |

| 5.5 | LE1 Logical Operations                                                               |

| 5.6 | LE1 register usage                                                                   |

| 7.1 | Kernel work dimensions, sizes and execution iterations from AMD AMP. $$ . 119 $$     |

| 7.2 | Kernel work dimensions, sizes and execution iterations from Rodinia. $\ . \ . \ 119$ |

| 7.3 | LE1 silicon data                                                                     |

| 7.4 | Average IRAM sizes across all configurations and compilers                           |

# Chapter 1

# Introduction

## 1.1 Problem Formulation

For several decades, since the inception of integrated circuits, transistors continued to shrink exponentially while maintaining the same power density [1][2]. This enabled reductions in power requirements, as the voltage and current demands both decreased with area, and also enabled higher clock frequencies. These two characteristics of shrinking transistors and maintained power density are respectively known as Moore's Law and Dennard scaling. Power in a digital circuit is composed of both its *static* and *dynamic* power. Static power is the energy that is wasted while trying to maintain state between switching states, and is caused by leakage current due to thermal excitations and quantum tunnelling. Where C is capacitance,  $V_{dd}$  is the the supply voltage and f being operating frequency, dynamic power  $(P_d)$  is given by [3]:

$$P_d = C V_{dd}^2 f \tag{1.1}$$

As transistors shrank, capacitance also diminished along with the supply voltage; allowing faster operating frequencies. With higher clock frequencies and more integrated functionality, processing capacity also increased exponentially with the reducing transistor size. For the software engineer, performance increase for their codes came for free, as microprocessors starting executing more simultaneous operations and at an increased rate. This type of parallelism is called *instruction-level parallelism* (ILP) and is utilised by having multiple functional units and usually some complex scheduling hardware. Segmenting the functional units into stages, called *pipelining*, allows for further ILP as multiple instructions can occupy different stages of the pipeline. This also allows for higher clock frequencies. However, shrinking transistor size also led to an increase in static power as more leakage current was induced; as such Dennard scaling stopped around 2005 [4]. It has been suggested that high-performance scaling for double-gate FinFET designs would cease between 12 and 15nm, and both IBM and Intel are now releasing tri-gate FinFET microprocessors at 14nm [5].

With the possible physical properties of silicon being realised, computer architectures have had to scale up performance in different ways, rather than relying on faster operating frequencies and ILP exploitation of uniprocessors. The initial solution was to instantiate multiple processing cores on the silicon and/or have the cores running multiple threads of execution; today this is the ubiquitous paradigm of computing. The exploitation of this type of *thread-level parallelism* (TLP), does however require effort from the software developer and requires new languages, or extentions to traditional ones. As power densities have risen, new techniques have been required to keep microprocessors cool enough to operate. This power requirement can be maintained by using different power states, where the microprocessor operates at different frequencies and voltages as well as powering down parts of the device when unneeded. This allows a device to reduce operating power when less work is required, but also to use short bursts of higher power to meet performance requirements while staying within the power envelope, termed *thermal dynamic power* (TDP). Switching off parts of the device leads to '*dark silicon*' because though the device has the silicon capacity, it doesn't have the capacity to dissipate the heat, which utimately limits the capabilities [6].

The latest paradigm shift to emerge is the use of coprocessors to offload computation away from the host CPU. This type of execution has been developed because most common programs are still dependent on single-threaded performance, and so common CPUs are designed to support those applications. However, some computationally intensive codes are highly parallel and these types of applications are becoming more popular; as the world generates and processes more data. So modern computers need to accelerate in both single- and multi-threaded workloads. Coprocessors are generally comprised of many, simple, cores and are designed as throughput devices, but this has required algorithms to be re-implemented for the vastly different architectures. The algorithms generally use *divide-and-conquer* techniques to split the work across those cores and explicitly identify both thread- and data-level parallelism. A key problem with this paradigm is that data has to be transferred between the host and the accelerator, but this is being addressed through modifications to language standards and the inception of the Heterogeneous System Architecture (HSA) [7].

### **1.2** Aims and Objectives

The aims of the research conducted are:

• Enable OpenCL compilation for custom VLIW Chip-Multiprocessor (CMP).

- Enable execution of OpenCL kernels on a FPGA platform.

- Extensively benchmark the CPU as this has not been previously performed.

Objectives:

- Implement C compiler backend for unique VLIW CMP.

- Investigate parallel computing techniques.

- Develop an OpenCL library to support parallel computing on the VLIW CMP.

- Investigate compiler performance across varying microarchitecture configurations of the configurable VLIW CMP.

- Investigate whole system performance of the VLIW CMP.

The objectives are based around creating a toolchain to enable the execution of explicitly parallel programs upon a unique, and configurable, VLIW CMP. The majority of parallel languages can be accessed using the C programming language and they also generally require some form of runtime support. This requires that not only does the high-level language need to be compiled for the target, but an execution framework also needs to be developed to fully enable the programs to run.

### 1.3 Outline of Areas of Research

This section aims to give the reader an overview of the main areas of research where work was conducted through this thesis.

### 1.3.1 Parallelism

Exploiting parallelism in code is the fundamental technique for modern microprocessors to achieve their required performance. The three types of parallelism are instruction-level, data-level and thread-level and most modern microprocessors will address all these levels of parallelism. In the 1960s, Flynn coarsely categorised computer architectures, which still helps describe the type of parallelism that they exploit [8]. The three key categories are:

- SISD *single instruction stream, single data stream* which are capable of extracting instruction-level parallelism from independent instructions within a single stream.

- SIMD *single instruction stream, multiple data stream* where a single instruction will operate on multiple data elements simultaneously as the data elements are parallel.

• MIMD - *multiple instruction stream, multiple data stream* computers describe the execution of multiple programs, processes or threads that operate on independent data.

Another important execution model that has become particularly popular recently is single program, multiple data (SPMD) which utilises a single instruction stream but operates on multiple data elements from different threads. This type of execution model is commonly used in graphic processing units (GPUs) and will be discussed in Section 2.4.1. The use of GPUs for general purpose programming has also resulted in the introduction of new programming languages and application programmable interfaces (APIs); the next subsection will discuss both traditional and more recent methods of parallel programming.

Instruction-Level Parallelism (ILP) describes that some instructions will be independent of one another and so can execute in parallel. This can be achieved in hardware by including multiple functional units for the instructions to occupy concurrently and by also pipelining the microprocessor to have multiple instructions in-flight, but at different stages. This type of parallelism is implicit, the exploitation is the task of the compiler and/or the microprocessor, so no effort from the programmer is needed. Microprocessors that rely on the ILP discovery at compile-time are termed *Very Long Instruction Word* (VLIWs), and are discussed in Section 2.3. Dynamically scheduled ILP processors are called *superscalars*, which are discussed in Section 2.2.2.

Data-Level Parallelism (DLP) arises when multiple data elements can be operated independently on at the same time. Vector supercomputers exploit DLP, as do microprocessors that have SIMD instructions in their ISA and these will be discussed in Section 2.2.3. This type of parallelism often needs to be identified by the programmer and they also usually have to design their program for the underlying architecture. DLP can be found via the compiler, although auto-vectorisation techniques are an ongoing research topic [9].

Thread-Level Parallelism (TLP) has become particularly important in the last decade, as uniprocessor clock rates plateaued and the limits of ILP had also been discovered. TLP allows programs to be split into independent parts, to be operated on by multiple processors. TLP could also describe task-level parallelism in which multiple independent programs, or processes, can operate simultaneously on different data streams. This type of parallelism is also explicitly identified by the programmer, and a key role of an operating system is to handle multiple processes. Multiprocessors and multithreading will be discussed in Section 2.2.4.

### 1.3.2 Compilers

Computer programs can be written in three forms: machine code (binary), the architecture's assembly language, or a higher level language such as C or Java. Writing machine code is only necessary in the absence of an assembler, which is very uncommon. High-performance, target specific codes and libraries, are often still written in assembly language [10][11]. However, most programs are written in higher level languages since they are more portable, quicker to write and easier to debug. It is the job of the compiler to translate higher level languages, via a series of stages or phases, into object code or machine language. Any basic compiler needs to have at least four phases [12]:

- lexical analysis which analyses the character strings presented to it and checks whether they are valid for the language,

- syntactic parsing which produces an intermediate-level representation and a symbol table of identifiers,

- static-semantic validity which checks that the intermediate code satisfies source language properties,

- the code generator which transforms the intermediate code into machine language.

Another phase that is essential to any modern compiler is the optimisation phase, and so a compiler can be logically split into three parts: the front-end, the high-level optimiser and the back-end. The front-end is language specific and organises the human-readable form into an intermediate representation (IR) and performs some language-specific optimisations. The high-level optimiser is responsible for machine-independent code transformations, including loop-level transformations, constant propagation and dead code elimination. The back-end is machine-specific and translates the IR into machine code and can perform machine-specific optimisations.

### **1.3.3** Heterogeneous Computing

Heterogeneous computing describes computer systems that comprise of two or more different computer architectures. These have been introduced as single-threaded performance improvements have slowed dramatically, with the failing of Dennard scaling. As well as the failing of Dennard scaling, another recent change in the microprocessor ecosystem is the kind of computation commonly being performed, as well as the amount of data being processed. In the consumer domain, the greatest growth is in smart mobile devices where graphics and camera performance are key. The business and server segments are heavily biased towards Big Data [13] whereas supercomputers are used for evermore complex simulations [14][15]. These three market segments, consumer (embedded), server and supercomputing, target not only processing system raw performance but, equally importantly, power consumption. In that respect, HPC vendors had already moved away from bespoke vector computers to commodity x86 parts, as these were cheaper and more efficient [16]. With the introduction of General-Purpose Graphics Programming Units GPGPUs and the release of the proprietary API CUDA from NVIDIA, a trend towards the universal use of Graphic Processing Units (GPUs) in all these market segments is emerging.

The Open Compute Language (OpenCL [17]) was proposed as an open standard API for general-purpose computing across CPUs, GPUs and other accelerators in response to CUDA's performance advantage on NVIDIA-only hardware. This was standardized by the Khronos Group and nowadays, OpenCL drivers are offered by all the major graphic processor designers such as AMD, Intel, and Qualcomm [18]. Unlike CUDA, OpenCL is target agnostic which has enabled the emergence of an OpenCL implementation ecosystem around not only GPUs but also CPUs and Field-Programmable Gate Arrays (FPGAs). Heterogeneous computing is used to create some of the most powerful and efficient supercomputers [19][20], but is also utilised in low-power devices, such as smartphones, through the use of OpenCL, CUDA and RenderScript [21].

### **1.4** Contributions of Thesis

The work presented in this thesis focuses on OpenCL compilation for a configurable VLIW. This has been achieved through the use of fully programmable, FPGA-based, configurable VLIW CMP as the target hardware platform. The developed toolchain implements a runtime driver that enables the programmer to compile and execute OpenCL kernels using the VLIW CMP as an accelerator. The main contributions made within this thesis are as follows:

Automatic Compilation Methodologies: A compiler backend for our in-house VLIW CMP has been implemented and incorporated into an OpenCL driver which has also been developed. This enables the programmer to select a target, from a multitude of system configurations, to execute the OpenCL kernels upon.

**SPMD Methodologies:** The compiler has been developed to contain unique intrinsics, accessed via a custom runtime library, to enable the execution of OpenCL kernels on the target. A method of statically scheduling work across multiple cores has also been developed.

**Source Transformer:** To enable execution of OpenCL programs on the VLIW CMP, it has been necessary to transform the kernel code. The source-to-source transformer has been implemented to perform this automatically and produces code that is generic, so could be used on other shared memory multiprocessors.

# 1.5 Thesis Outline

The remainder of this thesis is organised as follows:

- Chapter 2 is a detailed survey into how computer architectures exploit various forms of parallelism to increase single threaded execution speed, throughput and efficiency.

- Chapter 3 reviews the programming languages and software required to develop parallel applications on modern CPUs, accelerators and FPGAs.

- Chapter 4 summarises the background review and identifies the area of research that this thesis focuses on.

- Chapter 5 provides an indepth description of the compiler for the LE1.

- Chapter 6 describes the OpenCL driver for the LE1, for which the compiler is an essential component.

- Chapter 7 presents results and analysis from executing industry standard benchmarks, using the researched driver, on a cycle accurate simulator.

- Chapter 8 concludes this research and proposes possible extensions to the work.

# Chapter 2

# Parallel Computer Architectures

### 2.1 Chapter Objectives

The objective of this chapter is to give an overview of existing computer architectures and styles and how they exploit different types of parallelism to improve throughput and efficiency. The chapter also contains an in-depth history of the development of the VLIW architecture and how they are used today, with some modern architecture examples including the configurable VLIW CMP that the research in this thesis is based upon. The focus of modern architectures is still to continue improving throughput and execution, but also with a keen focus on power consumption and heat dissipation. Heterogenous computer architectures and hardware/software codesign are also introduced as these modern approaches aim to target both criteria.

### 2.2 Architecture Styles and Features

Modern CPUs still predominantly focus on improving single threaded performance and this is achieved through concurrently executing multiple instructions and reducing the number of stalls when accessing memory. Originally microprocessor designers aimed to achieve higher performance through the use of multiple, pipelined, functional units to better utilise the hardware to have multiple instructions in-flight. This section will introduce numerous methods, and implementations, for exploiting the various levels of parallelism identified in Section 1.3.1: with dynamic scheduling of multiple instructions, extensions to instruction sets to exploit DLP and the execution of multiple concurrent tasks.

### 2.2.1 Memory Hierachy

Figure 2.1: Memory hierachy in a modern smartphone.

As shrinking transistor sizes improved CPU performance exponentially, through faster clocks and more functional units, memory capacity also increased, however memory latency did not improve at the same rate as CPU frequency. This led to a significant performance bottleneck and so memory hierarchies were introduced into computer systems to help minimise the effect of slower memories. Figure 2.1 shows a typical, simplified, memory hierarchy of a modern smartphone, the added complexities of caches in multi-core systems will be further discussed in Section 2.2.4.1. The diagram shows that there are several levels, each getting larger, slower and cheaper the further away it is from the processor. CPU caches are implemented in SRAM as these are faster and require less power while DRAM is used as main memory because it is much more dense and cheap, but at the cost of speed and power requirements [22]. These characteristics lead to the tiered heirachy.

The purpose of the caches are to exploit spatial and temporal locality so that data that are likely to be needed by the processor, are closer to it. The latencies of the higher levels of memory can be hidden by keeping the required data in the nearest cache, and by keeping the lower caches small, the faster they can operate.

### 2.2.2 Superscalar Execution

In Sections 2.3 and 3.3, an in-depth introduction will be given into the methods used by VLIW architectures, and their compilers, to statically exploit ILP at compile time. ILP can also also be identified at runtime by the hardware and this type of processor is termed a dynamically scheduled superscalar. They too have multiple functional units, but also include additional hardware to resolve dependencies at runtime. Though this makes the hardware more complex, superscalars have the advantage of being able to react, and predict, runtime hazards such as branches and cache misses. There are two execution models for superscalars: in-order, where instructions are issued and executed in program order, and out-of-order in which instructions are fetched in-order but can execute and finish out of program order.