This item was submitted to Loughborough's Research Repository by the author. Items in Figshare are protected by copyright, with all rights reserved, unless otherwise indicated.

# Systolic arrays for the matrix iterative methods

PLEASE CITE THE PUBLISHED VERSION

**PUBLISHER**

© Shahid Abbas Haider

PUBLISHER STATEMENT

This work is made available according to the conditions of the Creative Commons Attribution-NonCommercial-NoDerivatives 2.5 Generic (CC BY-NC-ND 2.5) licence. Full details of this licence are available at: http://creativecommons.org/licenses/by-nc-nd/2.5/

LICENCE

CC BY-NC-ND 2.5

REPOSITORY RECORD

Haider, Shahid A.. 2019. "Systolic Arrays for the Matrix Iterative Methods". figshare. https://hdl.handle.net/2134/28173.

This item was submitted to Loughborough University as a PhD thesis by the author and is made available in the Institutional Repository (<a href="https://dspace.lboro.ac.uk/">https://dspace.lboro.ac.uk/</a>) under the following Creative Commons Licence conditions.

C O M M O N S D E E D

#### Attribution-NonCommercial-NoDerivs 2.5

#### You are free:

· to copy, distribute, display, and perform the work

#### Under the following conditions:

Attribution. You must attribute the work in the manner specified by the author or licensor.

Noncommercial. You may not use this work for commercial purposes.

No Derivative Works. You may not alter, transform, or build upon this work.

- For any reuse or distribution, you must make clear to others the license terms of this work.

- Any of these conditions can be waived if you get permission from the copyright holder.

Your fair use and other rights are in no way affected by the above.

This is a human-readable summary of the Legal Code (the full license).

Disclaimer 🗖

For the full text of this licence, please go to: <a href="http://creativecommons.org/licenses/by-nc-nd/2.5/">http://creativecommons.org/licenses/by-nc-nd/2.5/</a>

# LOUGHBOROUGH UNIVERSITY OF TECHNOLOGY LIBRARY

|                 |            | <del></del>                                  |

|-----------------|------------|----------------------------------------------|

| AUTHOR/FILING 1 | TITLE      |                                              |

| 14              | AIDER, S.A |                                              |

|                 |            |                                              |

|                 |            |                                              |

| ACCESSION/COPY  | γ˙ NO.     |                                              |

| ·               | 040,21862  |                                              |

| VOL. NO.        | CLASS MARK |                                              |

|                 |            |                                              |

|                 |            | <u>.                                    </u> |

|                 | LOAM COPY  |                                              |

|                 | ·          |                                              |

|                 |            |                                              |

|                 |            |                                              |

|                 |            |                                              |

|                 | ·          |                                              |

|                 |            | •                                            |

|                 |            |                                              |

| •               |            |                                              |

|                 |            |                                              |

|                 |            |                                              |

|                 | ì          |                                              |

|                 |            |                                              |

|                 |            | ,                                            |

0401218027

|   |   |  |   | 1 |

|---|---|--|---|---|

|   |   |  |   | 1 |

|   |   |  |   |   |

|   |   |  |   | 1 |

|   | • |  |   | 1 |

|   |   |  |   | 1 |

|   |   |  |   | 1 |

|   |   |  |   | 1 |

|   |   |  |   |   |

|   |   |  |   | · |

|   |   |  |   |   |

|   |   |  |   |   |

|   |   |  |   |   |

| · | • |  | • |   |

|   |   |  |   |   |

|   |   |  |   |   |

|   |   |  |   |   |

|   |   |  |   |   |

|   |   |  |   |   |

# SYSTOLIC ARRAYS FOR THE MATRIX ITERATIVE METHODS

$\mathbf{B}\mathbf{y}$

Shahid Abbas Haider, BEng., MSc.

A Doctoral Thesis submitted in partial fulfillment

of the requirements for the

Award of the Degree of

Doctor of Philosophy

of Loughborough University of Technology

**April 1993**

©Shahid Abbas Haider

|             | ughbarasah Uriversiy<br>filisabasa - 11 may                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Mar 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Class       | THE THE TAX I SEE A SEE AS A SECOND OF THE TAX I SEE AS A SECOND OF THE TAX I SEE AS A SECOND OF THE TAX I |

| Acc.<br>No. | 040121862                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Loughbornsich UN of Fection 11 | Andrig<br>Tay                                 |

|--------------------------------|-----------------------------------------------|

| Date Mar 96                    | ga, ana'yan ke <b>isas</b> a <b>dis</b> hiran |

| Class                          | ·                                             |

| Acc.<br>No. 040121862          | بالزوادي د عرويف                              |

# SYSTOLIC ARRAYS FOR THE MATRIX ITERATIVE METHODS

By

Shahid Abbas Haider, BEng., MSc.

A Doctoral Thesis submitted in partial fulfillment

of the requirements for the

Award of the Degree of

Doctor of Philosophy

of Loughborough University of Technology

**April** 1993

©Shahid Abbas Haider

# **CERTIFICATE OF ORIGINALITY**

This is to certify that I am responsible for the work submitted in this thesis, that the original work is my own except as specified in acknowledgements or in footnotes, and that neither the thesis nor the original work contained therein has been submitted to this or any other institution for a higher degree.

Shahid Abbas Haider

## **ACKNOWLEDGEMENTS**

I wish to express my sincere thanks, gratitude and appreciation to my supervisor, Professor D. J. Evans, Director, Parallel Algorithm Research Centre (PARC), for his constant advice, guidance, interest and above all, encouragement throughout my research, as well as his endeavor in reading the manuscript of this thesis.

I express my thanks to Professor J. L. Alty, Head of the Computer Studies Department, for his advice and interest; to the staff of the Computer Studies Department and especially PARC; and to the research students at PARC.

I would also like to convey my deep gratitude to the Ministry of Science and Technology, Government of Pakistan, for their financial support without which this thesis would have never been completed.

Eternal thanks to my parents, brothers and sisters, for their immense love, encouragement and their sound belief in my success, without which this work would have been inconceivable.

### Abstract

The systolic array research was pioneered by H. T. Kung and C. E. Leiserson. Systolic arrays are special purpose synchronous architectures consisting of simple, regular and modular processors which are regularly interconnected to form an array.

Systolic arrays are well suited for computational bound problems in Linear Algebra. In this thesis, the numerical problems, especially iterative algorithms are chosen and implemented on the linear systolic array.

Iterative methods perform a sequence of repetitive steps to obtain a new approximation which converge to a solution. The accuracy of the method depends on the number of iterations performed. The iterative process is terminated when the difference between the successive approximation satisfies some tolerance.

Several iterative methods like the Jacobi, Gauss-Seidel, S.O.R., S.S.O.R., A.O.R., M.S.O.R. etc. are mapped on to a linear systolic array. The systolic designs are simulated in OCCAM.

Problems involving rates of change of two or more independent variables representing some physical quantity leads to a partial differential equation. These equations can be discretised and then solved by applying the iterative methods. The 2-dimensional and 3-dimensional problems are taken as example and are discretised. The discretised problems generate sparse matrix systems. The concept of a Virtual IPS cell is introduced to cope with wide sparse matrix systems. Using these cells, a linear systolic array is simulated and several iterative algorithms are used to solve PDE's by the second order Richardson iterative method, S.O.R., Steepest Descent, Conjugate Gradient and Preconditioned Conjugate Gradient methods. The concept of Virtual IPS cell reduces the area requirements of the array but the computational time remains the same.

# Contents

| 1 | Intr | duction and Fundamentals of Parallel Computer Archi- |

|---|------|------------------------------------------------------|

|   | tect | ires 1                                               |

|   | 1.1  | Introduction                                         |

|   | 1.2  | Architectural configuration of parallel computers    |

|   |      | 1.2.1 Pipelined computers                            |

|   |      | 1.2.2 Array processors                               |

|   |      | 1.2.3 Multiprocessor systems                         |

|   |      | 1.2.4 Data flow computers                            |

|   |      | 1.2.5 VLSI systems                                   |

|   | 1.3  | Classification of computer systems                   |

|   |      | 1.3.1 SIMD computers                                 |

|   |      | 1.3.2 MIMD computers                                 |

|   | 1.4  | Loosely-Coupled Systems (LCS)                        |

|   | 1.5  | Fightly-Coupled Systems (TCS)                        |

|   |      | 1.5.1 The Sequent Balance and Symmetry systems       |

|   | 1.6  | The Hypercube systems $$                             |

|   | 1.7  | Transputer systems                                   |

| 2 | Bas  | Mathematics and Computational Concepts 42            |

|   | 2.1 | Introd | uction                                 | 43         |

|---|-----|--------|----------------------------------------|------------|

|   | 2.2 | Vector | s and Matrices                         | <b>4</b> 3 |

|   |     | 2.2.1  | Vector and Matrix Norms                | 48         |

|   | •   | 2.2.2  | Eigenvalues and Eigenvectors           | 49         |

|   | 2.3 | Comp   | utational linear algebra               | 51         |

|   |     | 2.3.1  | Direct methods                         | 52         |

|   |     | 2.3.2  | Indirect methods                       | 53         |

|   |     | 2.3.3  | Simultaneous Displacement (SI) methods | 58         |

|   |     | 2.3.4  | Successive Displacement (SD) methods   | 59         |

|   | 2.4 | Conve  | rgence of iterative methods            | 61         |

|   | 2.5 | Partia | l differential equations               | 65         |

| 3 | Des | ign of | Systolic Arrays                        | 70         |

| _ |     | J      | •                                      | 71         |

|   | 3.1 |        | uction                                 |            |

|   | 3.2 | Systol | ic array                               | 72         |

|   |     | 3.2.1  | Semi systolic designs                  | 75         |

|   |     | 3.2.2  | Pure systolic designs                  | 77         |

|   |     | 3.2.3  | Hybrid systolic designs                | 78         |

|   | 3.3 | Systol | ic architectures and VLSI              | 78         |

|   | 3.4 | Perfor | mance issues                           | 81         |

|   | 3.5 | WARI   | Parchitecture                          | 83         |

|   | 3.6 | CHiP   | architecture                           | 84         |

|   | 3.7 | Design | improvements                           | 84         |

|   |     | 3.7.1  | Kung's design                          | 86         |

|   |     | 3.7.2  | The Evans and Bekakos design           | 89         |

|   |     | 3.7.3  | The Evans and Gusev design             | 90         |

|   |     | 3.7.4   | The Suros and Montagne design                            | . 91  |

|---|-----|---------|----------------------------------------------------------|-------|

|   |     | 3.7.5   | Comparison of different mvm designs                      | . 92  |

|   | 3.8 | Applie  | cation of systolic designs to the iterative solvers      | . 98  |

|   |     | 3.8.1   | Systolic designs for the Jacobi iterative method         | . 98  |

|   |     | 3.8.2   | Systolic designs for the Gauss-Seidel iterative method . | . 104 |

| 4 | Sys | tolic A | rrays for the Symmetric S.O.R. and Related Meth          | 1-    |

|   | ods |         |                                                          | 109   |

|   | 4.1 | Introd  | luction                                                  | . 110 |

|   | 4.2 | Basic   | iterative methods                                        | . 111 |

|   |     | 4.2.1   | The Jacobi Overrelaxation method                         | . 112 |

|   |     | 4.2.2   | The Successive Overrelaxation method                     | . 113 |

|   |     | 4.2.3   | The Modified Successive Overrelaxation method            | . 114 |

|   |     | 4.2.4   | The Symmetric Successive Overrelaxation method           | . 116 |

|   |     | 4.2.5   | The U.S.S.O.R. iterative method                          | . 118 |

|   | 4.3 | Systol  | ic designs for the iterative solvers                     | . 119 |

|   |     | 4.3.1   | The S.O.R. systolic design                               | . 119 |

|   |     | 4.3.2   | The J.O.R. systolic design                               | . 123 |

|   |     | 4.3.3   | The M.S.O.R. systolic design                             | . 125 |

|   |     | 4.3.4   | The S.S.O.R. systolic design                             | . 131 |

|   |     | 4.3.5   | The U.S.S.O.R. systolic design                           | . 134 |

|   | 4.4 | Furth   | er design improvements                                   | . 134 |

|   |     | 4.4.1   | Pipelining                                               | . 134 |

|   |     | 4.4.2   | Systolic design for pumping data                         | . 135 |

|   | 4.5 | Concl   | usions                                                   | . 136 |

| 5 | Fur | ther N  | Aatrix Iterative Methods                                 | 138   |

| 5.1 | Introd | uction                                                       |

|-----|--------|--------------------------------------------------------------|

|     | 5.1.1  | The first order Richardson iterative method 139              |

|     | 5.1.2  | The first order Richardson iterative method with Cheby-      |

|     |        | shev acceleration                                            |

|     | 5.1.3  | The second order Richardson iterative method 148             |

|     | 5.1.4  | The Chebyshev acceleration of the second order Richard-      |

|     |        | son iterative method                                         |

|     | 5.1.5  | The Accelerated Overrelaxation (A.O.R.) iterative method 154 |

|     | 5.1.6  | The Symmetric A.O.R. iterative method 156                    |

|     | 5.1.7  | The Unsymmetric A.O.R. iterative method 157                  |

| 5.2 | Systol | ic designs                                                   |

|     | 5.2.1  | Systolic design for the second order Richardson iterative    |

|     |        | method with Chebyshev acceleration                           |

|     | 5.2.2  | Design improvements                                          |

|     | 5.2.3  | Systolic design for the stationary second order Richard-     |

|     |        | son iterative method                                         |

|     | 5.2.4  | Systolic design for the A.O.R. iterative method 168          |

|     | 5.2.5  | Systolic design for the S.A.O.R. iterative method 175        |

|     | 5.2.6  | Systolic design for the U.S.A.O.R. iterative method 179      |

| 5.3 | Concl  | usions                                                       |

| 5.4 | Exam   | ple                                                          |

| 2D- | Design | n of Systolic Arrays 182                                     |

|     | _      | luction                                                      |

| 6.1 |        |                                                              |

| 6.2 |        | verrelaxation iterative methods                              |

|     | 621    | The J.O.R. iterative method                                  |

6

|   |      | 6.2.2    | The S.O.R. iterative method                            | . 187 |

|---|------|----------|--------------------------------------------------------|-------|

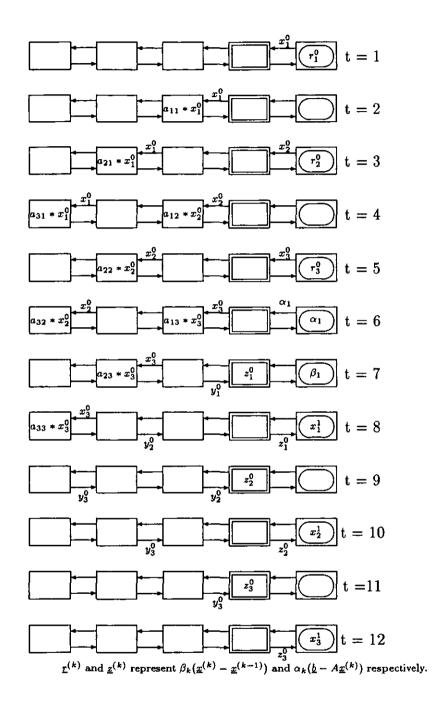

|   | 6.3  | Virtua   | al IPS cell                                            | . 188 |

|   | 6.4  | Systoli  | ic designs for the overrelaxation iterative methods    | . 190 |

|   |      | 6.4.1    | Systolic Sparse Array Design (SSAD) for the J.O.R. it- |       |

|   |      |          | erative method                                         | . 190 |

|   |      | 6.4.2    | Systolic design for the S.O.R. iterative method        | . 194 |

|   |      | 6.4.3    | Systolic designs for the S.S.O.R., A.O.R. and S.A.O.R. |       |

|   |      |          | iterative methods                                      | . 196 |

|   | 6.5  | 3D Pr    | oblems                                                 | . 196 |

|   | 6.6  | The G    | radient method                                         | . 198 |

|   | 6.7  | The C    | onjugate Direction method                              | . 200 |

|   | 6.8  | The C    | onjugate Gradient method                               | . 202 |

|   |      | 6.8.1    | Systolic design for the C.G. iterative method          | . 203 |

|   | 6.9  | The P    | reconditioned Conjugate Gradient method                | . 211 |

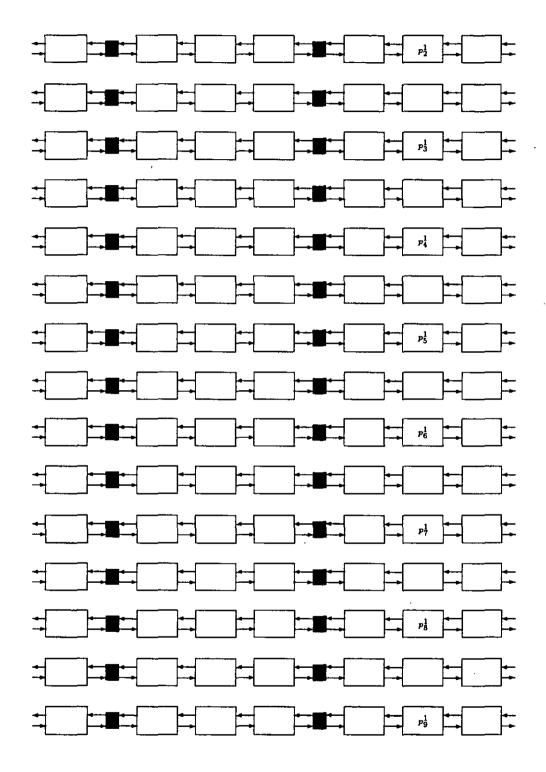

|   |      | 6.9.1    | Systolic design for the P.C.G. iterative method        | . 214 |

|   | 6.10 | The M    | Iodel problem                                          | . 214 |

|   |      | 6.10.1   | Model problem 1                                        | . 216 |

|   |      | 6.10.2   | Model problem 2                                        | . 216 |

|   | 6.11 | Conclu   | ısions                                                 | . 217 |

| 7 | Con  | alusia   | ns and suggestions for further work                    | 219   |

| • | Con  | ciusioi  | is and suggestions for further work                    | 219   |

|   | Refe | erence   | S                                                      | 225   |

| A | Syst | tolic si | mulator for the S.A.O.R. iterative method              | 234   |

|   | A.1  | Main I   | program                                                | . 234 |

|   | Δ 2  | Cell ar  | rchitectura                                            | 943   |

| A.3 | Get data routine .  | • | • | • | • | • | • | • | • | ٠ | ٠ | • | ٠ | • | • | ٠ | • | • | • | • | ٠ | • | ٠ | • | • | • | <b>24</b> 5 |

|-----|---------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-------------|

| A.4 | Convergence test .  |   |   |   |   |   | • |   | • | • |   |   |   |   |   |   |   |   |   | • |   |   |   |   |   |   | 247         |

| A.5 | Reverse the system  |   |   |   | • |   |   |   |   |   |   |   |   |   |   |   | • |   |   |   |   |   |   |   |   |   | 248         |

| A.6 | Display the results |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 249         |

# List of Figures

| 1.1  | Von Neumann computer model                                     | 5  |

|------|----------------------------------------------------------------|----|

| 1.2  | n-stage pipelined computer                                     | 6  |

| 1.3  | Non-pipelined execution                                        | 7  |

| 1.4  | Pipelined execution                                            | 7  |

| 1.5  | ICL DAP architecture                                           | 10 |

| 1.6  | Multiprocessor architecture                                    | 12 |

| 1.7  | Time-shared bus (single bus) multiprocessor                    | 13 |

| 1.8  | Crossbar switch network multiprocessor                         | 14 |

| 1.9  | Multiport memories multiprocessor organisation                 | 15 |

| 1.10 | Data flow graph for calculating mean and standard deviation    | 17 |

| 1.11 | Achieving parallelism by using a special-purpose parallel pro- |    |

|      | cessor                                                         | 20 |

| 1.12 | Computer system with several VLSI processor arrays             | 21 |

| 1.13 | Systolic processor array.                                      | 22 |

| 1.14 | Flynn's classification of computer systems                     | 25 |

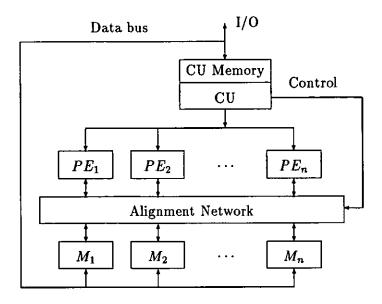

| 1.15 | The SIMD computer organisation                                 | 27 |

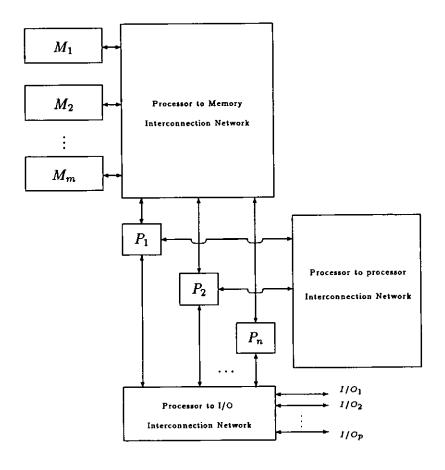

| 1.16 | MIMD computer organisation                                     | 29 |

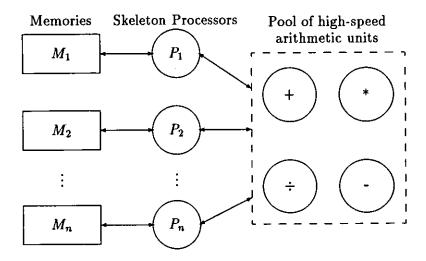

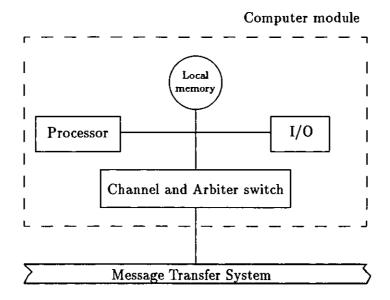

| 1.17 | MIMD systems with skeleton processors                          | 29 |

| 1.18 | Loosely-coupled (LCS) multiprocessor module                    | 32 |

| 1.19 | Communications between tasks in a LCS multiprocessor 33          |

|------|------------------------------------------------------------------|

| 1.20 | Sequent Balance 8000 architecture                                |

| 1.21 | Hardware structures for memory-shared and message-passing        |

|      | systems                                                          |

| 1.22 | The Transputer chip                                              |

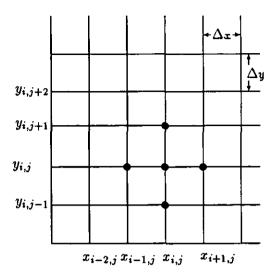

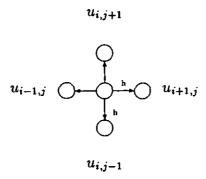

| 2.1  | Grid                                                             |

| 2.2  | Laplace computational molecule                                   |

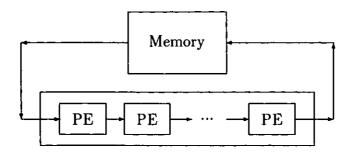

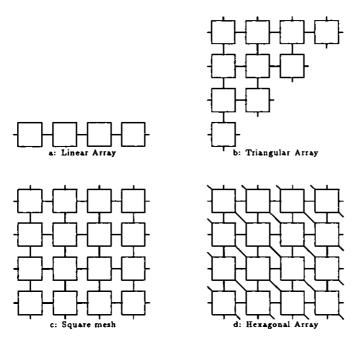

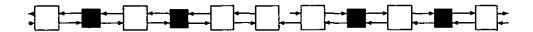

| 3.1  | Linear systolic array                                            |

| 3.2  | Systolic structures                                              |

| 3.3  | Uni-directional systolic array                                   |

| 3.4  | Bi-directional systolic array                                    |

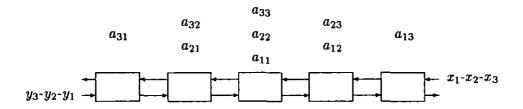

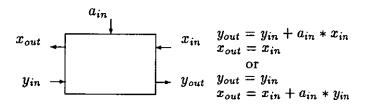

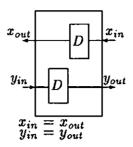

| 3.5  | IPS processor                                                    |

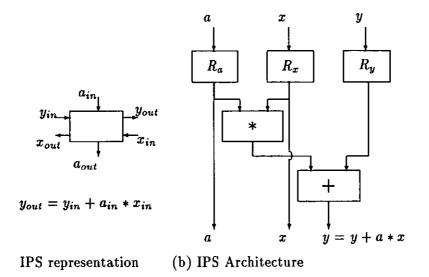

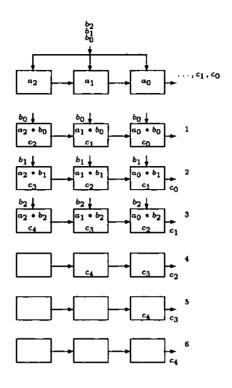

| 3.6  | Polynomial multiplication on a Semi systolic array               |

| 3.7  | Polynomial multiplication on a Pure systolic array               |

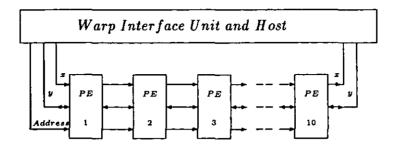

| 3.8  | The Warp programmable, one dimensional systolic array 83         |

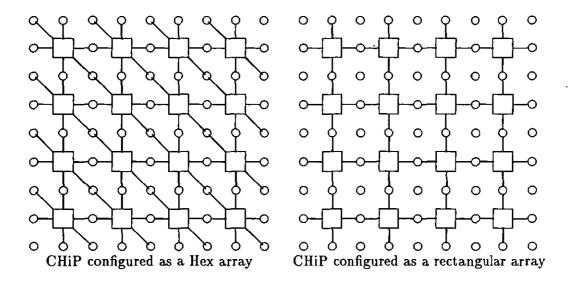

| 3.9  | CHiP lattice of intermixed switch and processing elements 85     |

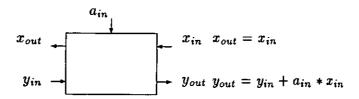

| 3.10 | The inner product step cell                                      |

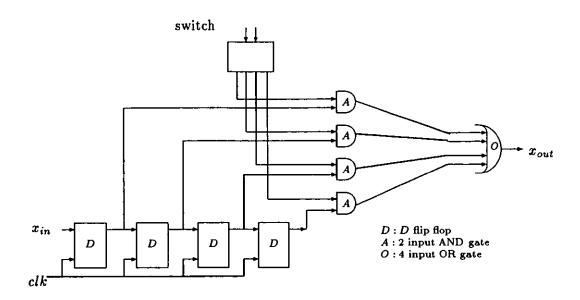

| 3.11 | Switch inner product step cell                                   |

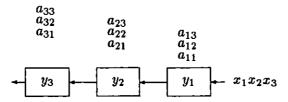

| 3.12 | The matrix vector multiply design proposed by H. T. Kung 94      |

| 3.13 | The matrix vector multiply design proposed by Evans and          |

|      | Bekakos                                                          |

| 3.14 | Matrix vector multiply design proposed by Evans and Gusev 96     |

| 3.15 | Matrix vector multiply design proposed by Suros and Montagne. 97 |

| 3.16 | The Jacobi iterative method on Kung's array                      |

| 3 17 | The Jacobi iterative method on Evans and Bekakos array 101       |

| 3.18 | The Jacobi iterative method on Evans and Gusev array 102                       |

|------|--------------------------------------------------------------------------------|

| 3.19 | The Jacobi iterative method on Suros and Montagne array 103                    |

| 3.20 | The Gauss-Seidel iterative method on Kung's array 107                          |

| 3.21 | The Gauss-Seidel iterative method Evans and Gusev array 108                    |

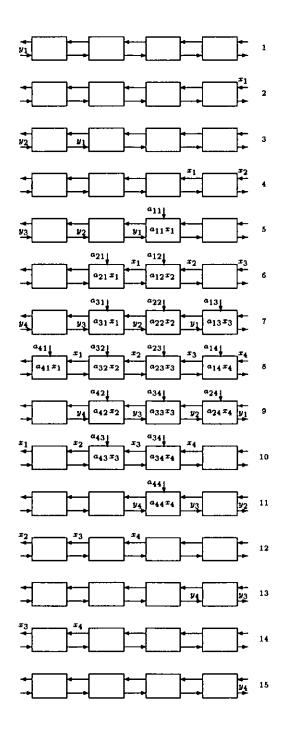

| 4.1  | Systolic design for the Jacobi iterative method                                |

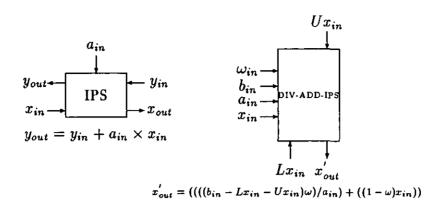

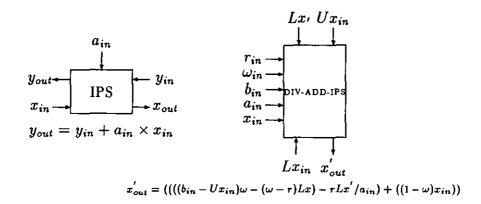

| 4.2  | IPS and DIV ADD IPS cells                                                      |

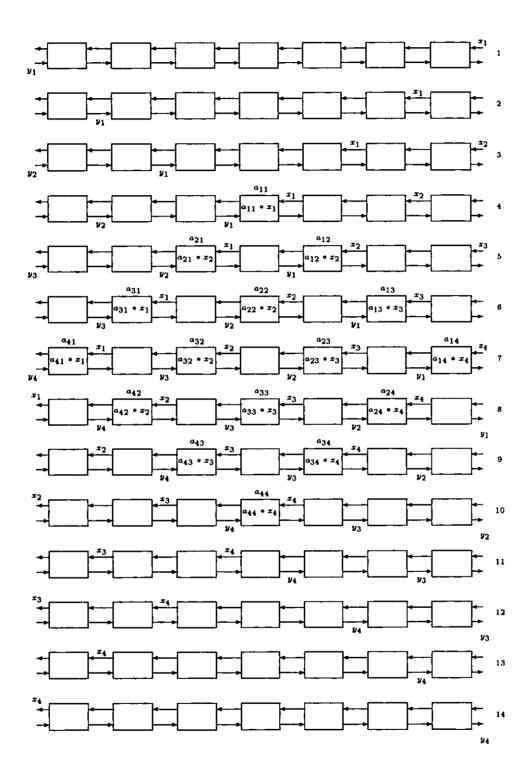

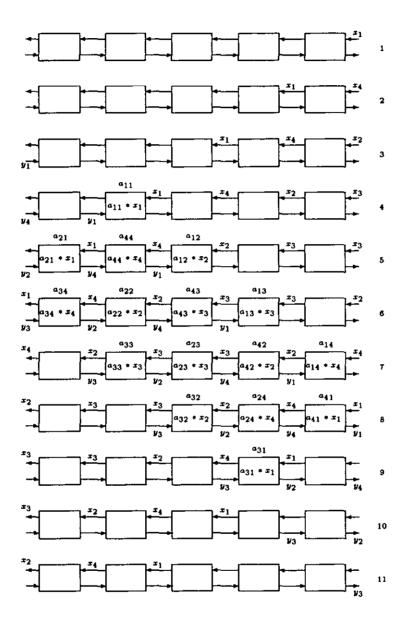

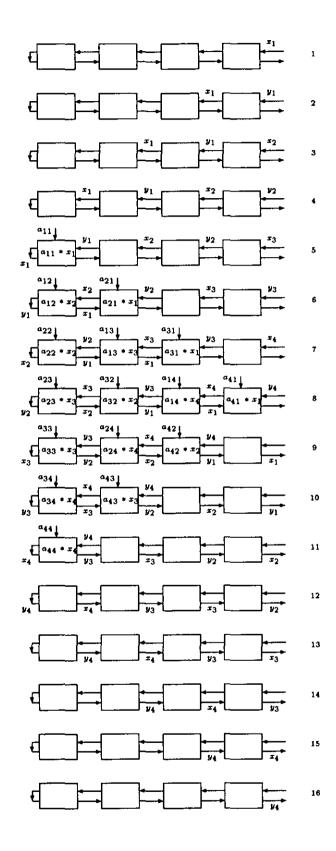

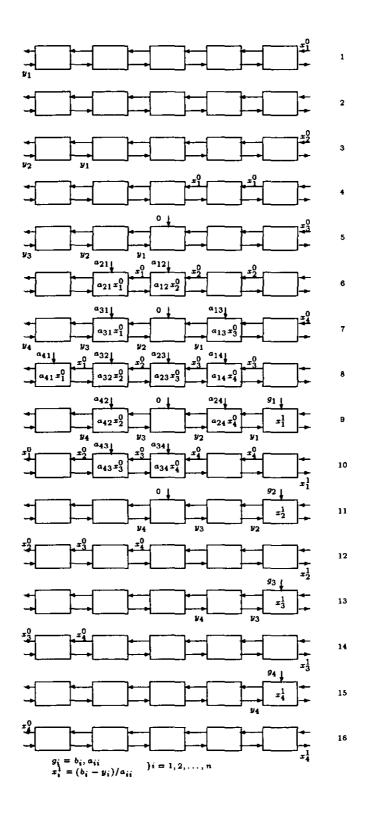

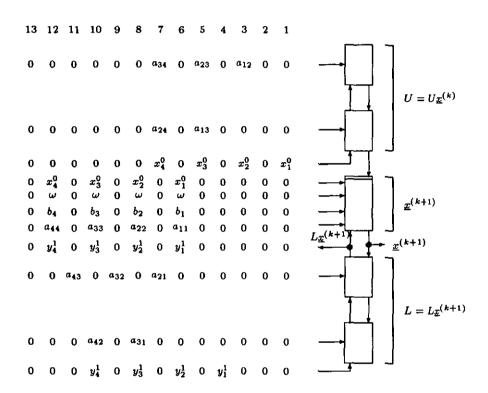

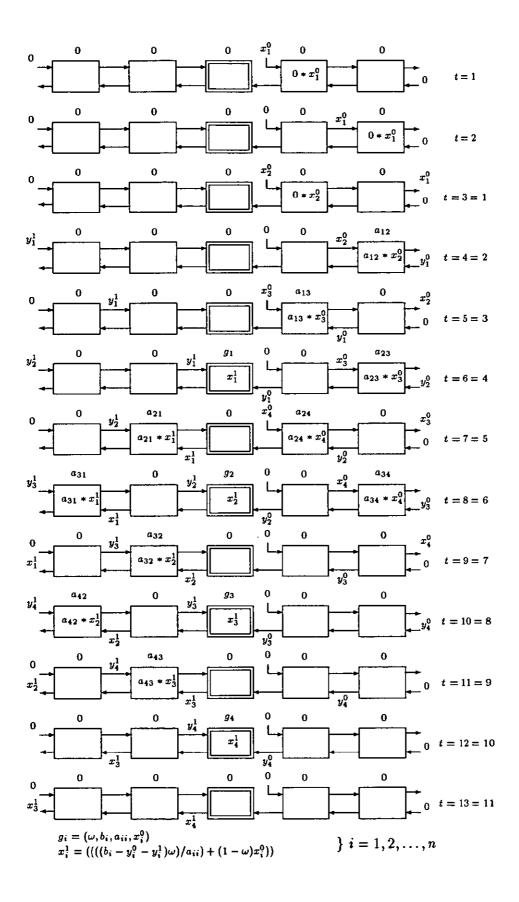

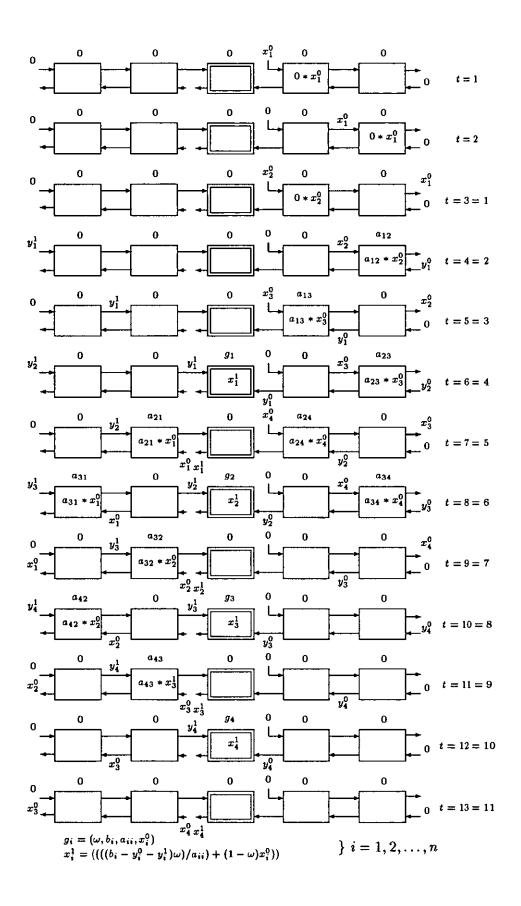

| 4.3  | Systolic design for the $1^{st}$ iteration of the S.O.R. iterative method.121  |

| 4.4  | Snap shots of the $1^{st}$ iteration for the S.O.R. iterative method 122       |

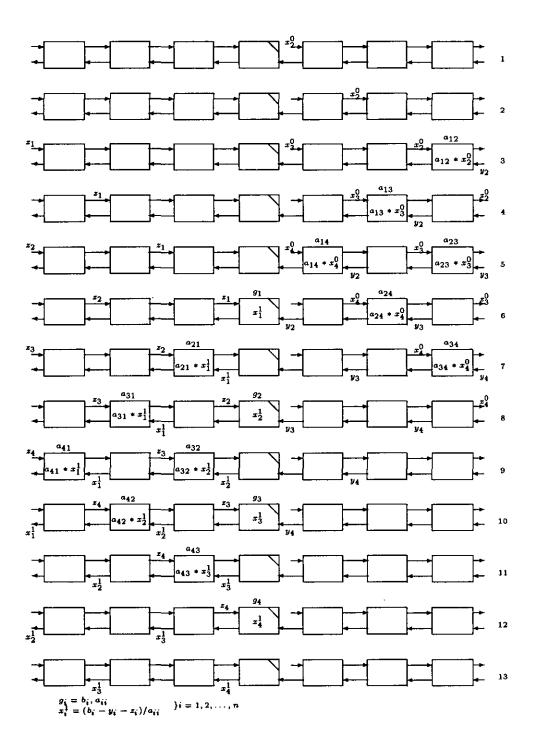

| 4.5  | Snap shots of the $1^{st}$ iteration for the J.O.R. iterative method 124       |

| 4.6  | Systolic design for the M.S.O.R. iterative method                              |

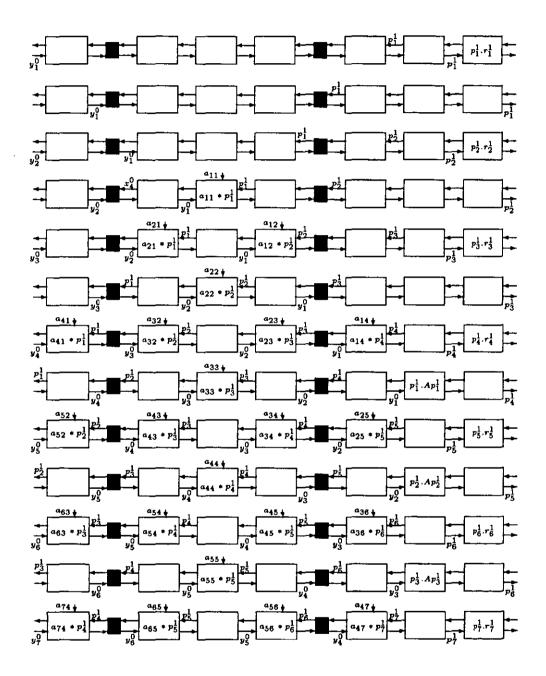

| 4.7  | Snap shots of the M.S.O.R. systolic design 1                                   |

| 4.8  | Snap shots of the M.S.O.R. systolic design 2                                   |

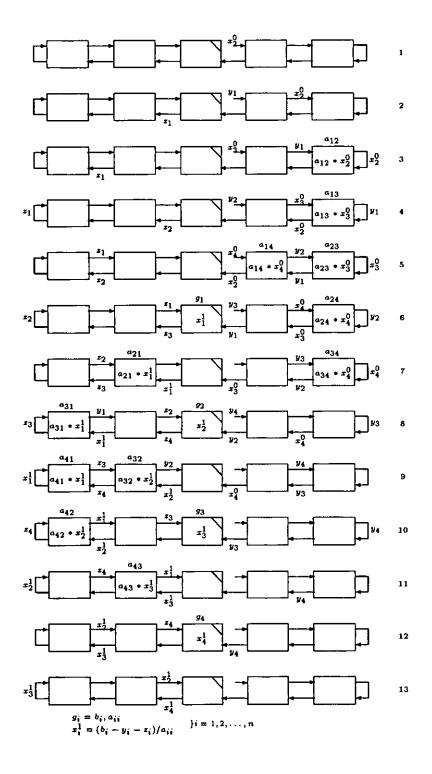

| 4.9  | Systolic design for the $2^{nd}$ iteration of S.S.O.R. iterative method. 132   |

| 4.10 | Snap shots for the $2^{nd}$ iteration of the S.S.O.R. iterative method. 133    |

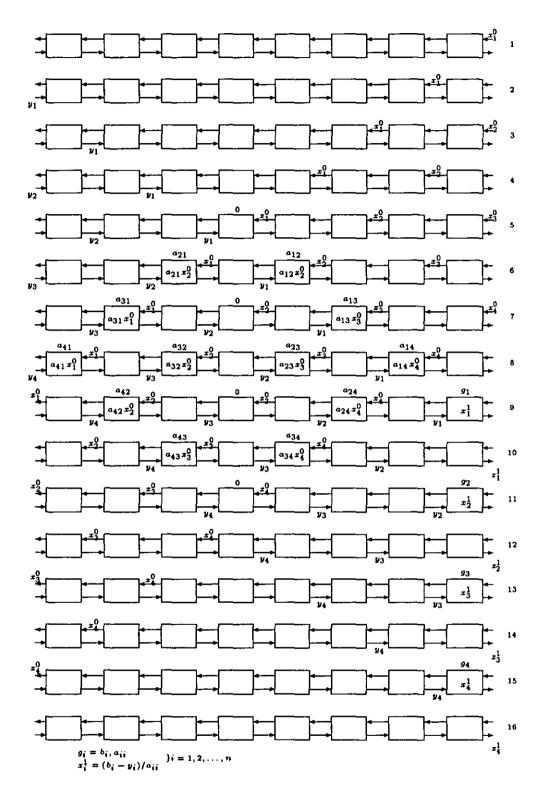

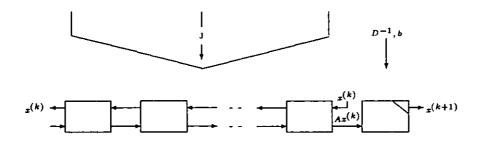

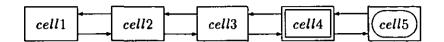

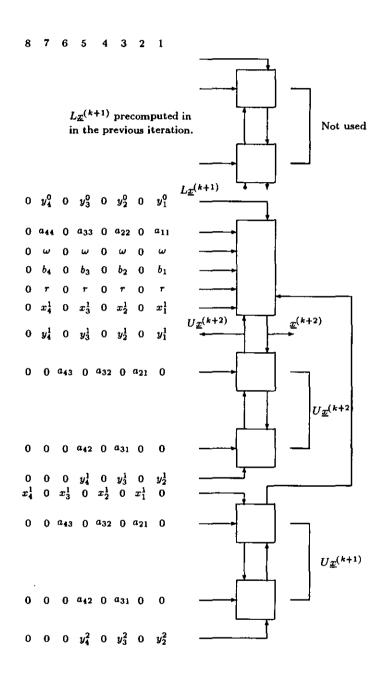

| 5.1  | Linear systolic array for the second order Richardson iterative                |

|      | method                                                                         |

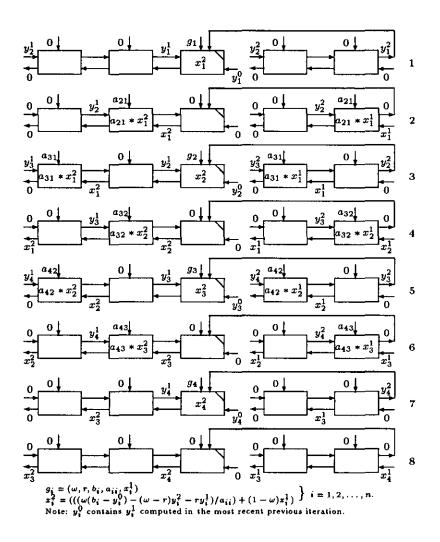

| 5.2  | Cell operations for the nonstationary second order Richardson iterative method |

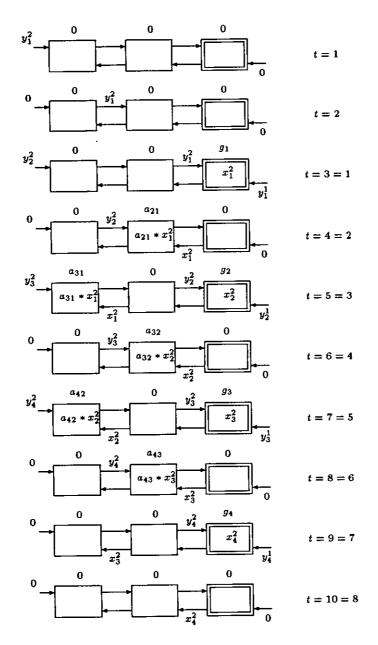

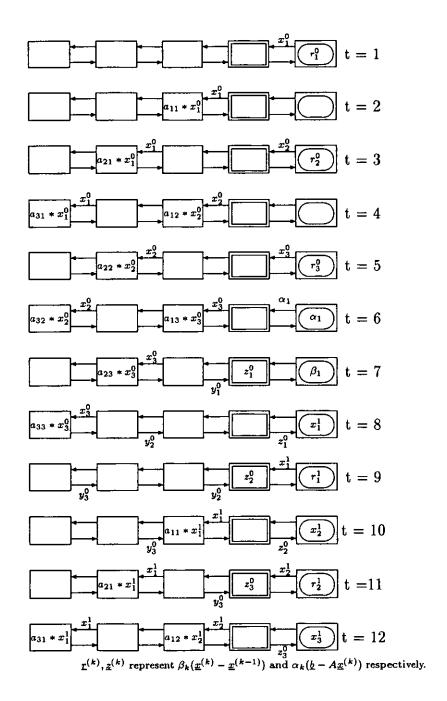

| 5.3  | Snap shots for the nonstationary second order Richardson iter-                 |

|      | ative method                                                                   |

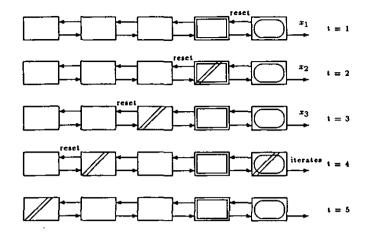

| 5.4  | Termination process for a $(3 \times 3)$ system                                |

| 5.5  | Snap shots for the pipelined design of the 1st iteration of the                |

|      | nonstationary second order Richardson iterative method 166                     |

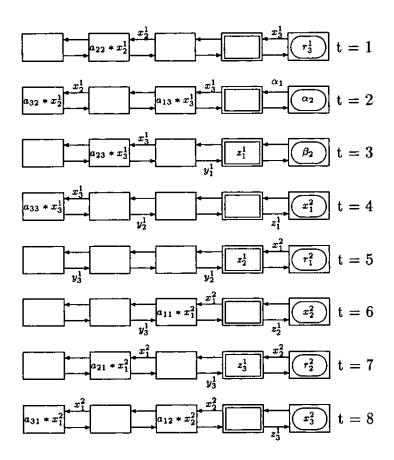

| 5.6  | Snap shots for the pipelined design of the $2^{nd}$ iteration of the           |

|      | nonstationary second order Richardson iterative method 167                     |

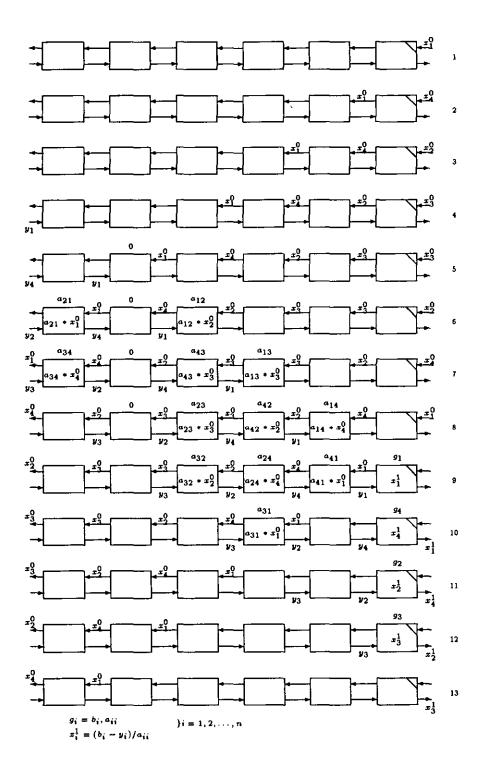

| 5.7  | Systolic design for the 1 <sup>st</sup> iteration of the A.O.R. iterative method.171 |

|------|--------------------------------------------------------------------------------------|

| 5.8  | Systolic design for the $2^{nd}$ iteration of the A.O.R. iterative method. 172       |

| 5.9  | Snap shots for the $1^{st}$ iteration of the A.O.R. iterative method 173             |

| 5.10 | Snap shots for the $2^{nd}$ iteration of the A.O.R. iterative method. 174            |

| 5.11 | Cells for the A.O.R. and S.A.O.R. iterative methods 176                              |

| 5.12 | Systolic design for the $2^{nd}$ iteration of the S.A.O.R. iterative method          |

| 5.13 | Snap shots for the $2^{nd}$ iteration of the S.A.O.R. iterative method.178           |

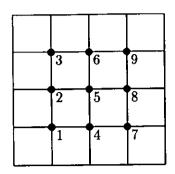

| 6.1  | Unit square with 9 internal mesh points                                              |

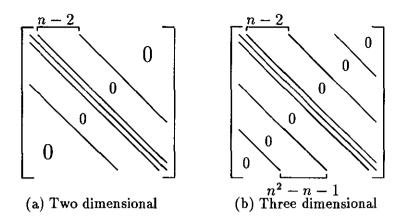

| 6.2  | Two and three dimensional forms of sparse matrices 188                               |

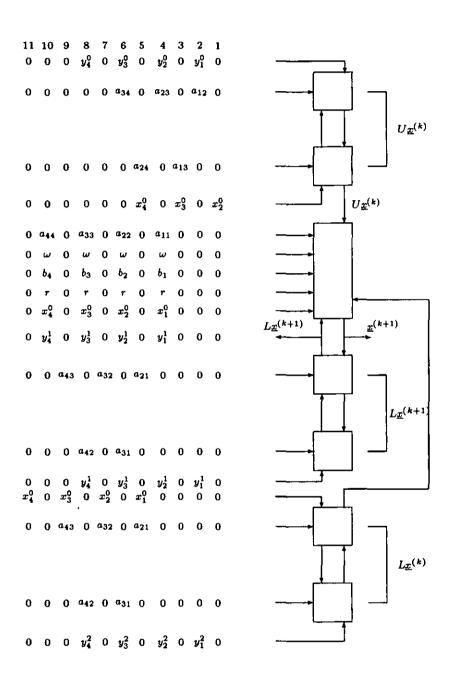

| 6.3  | Virtual IPS cell                                                                     |

| 6.4  | Section of a Programmable Virtual IPS cell                                           |

| 6.5  | Sparse matrix A                                                                      |

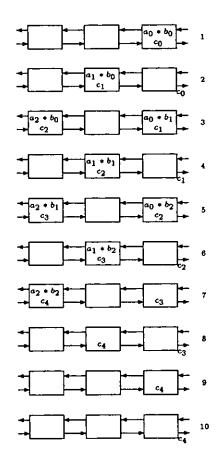

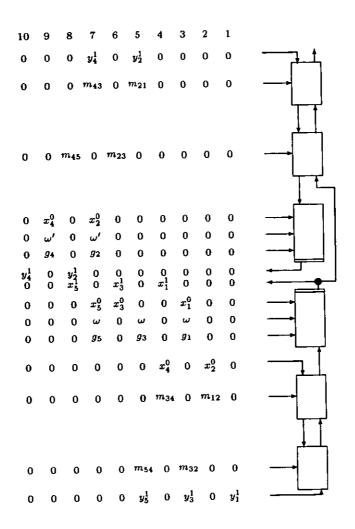

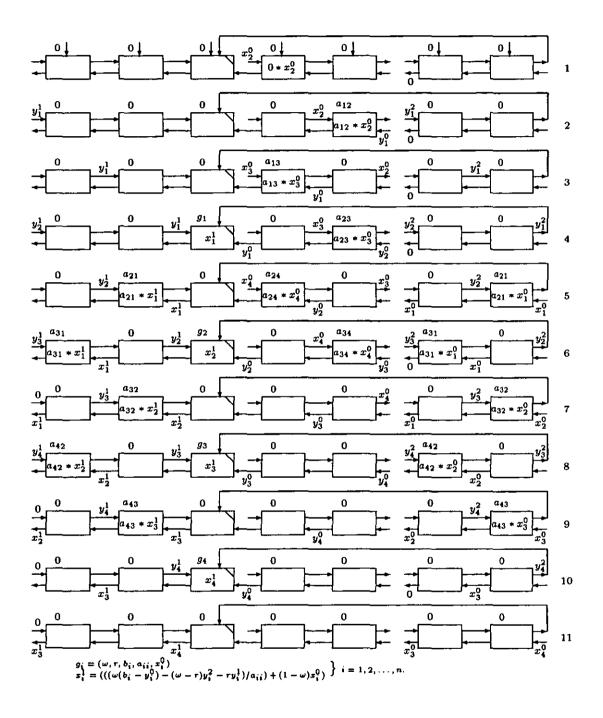

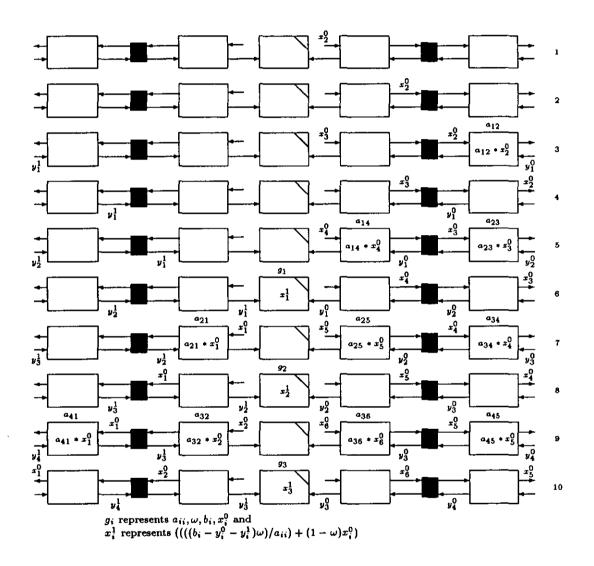

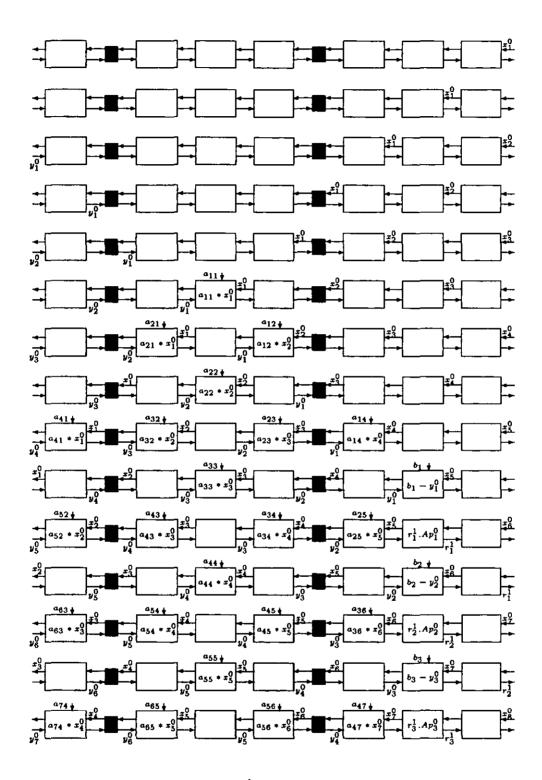

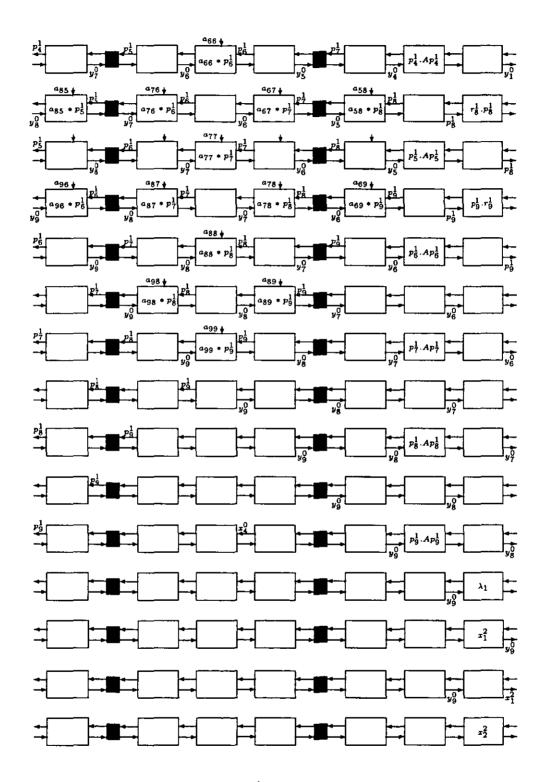

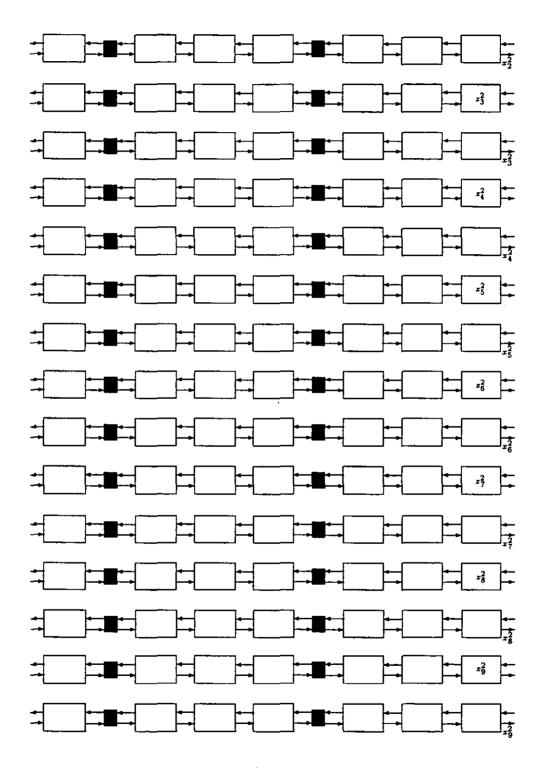

| 6.6  | 1 <sup>st</sup> 10 snap shots for the J.O.R. iterative method 195                    |

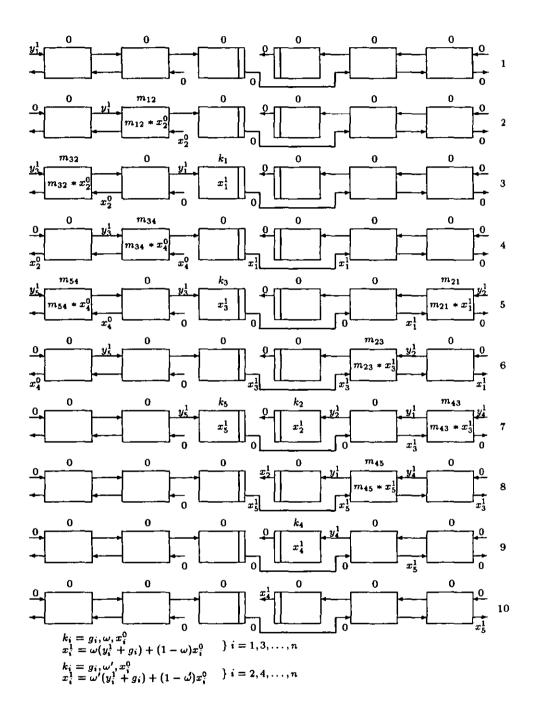

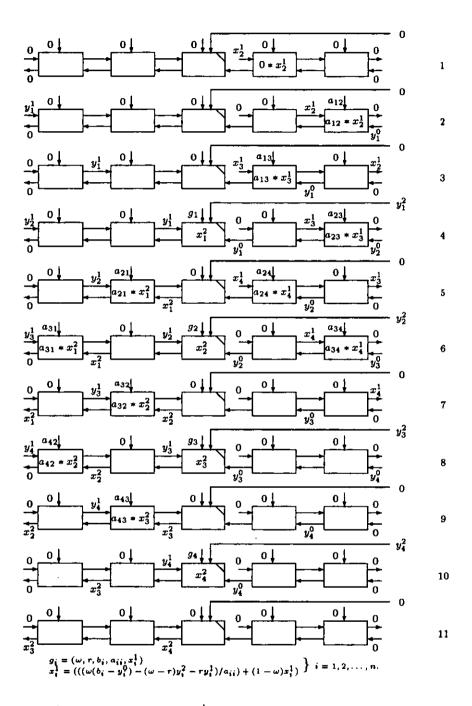

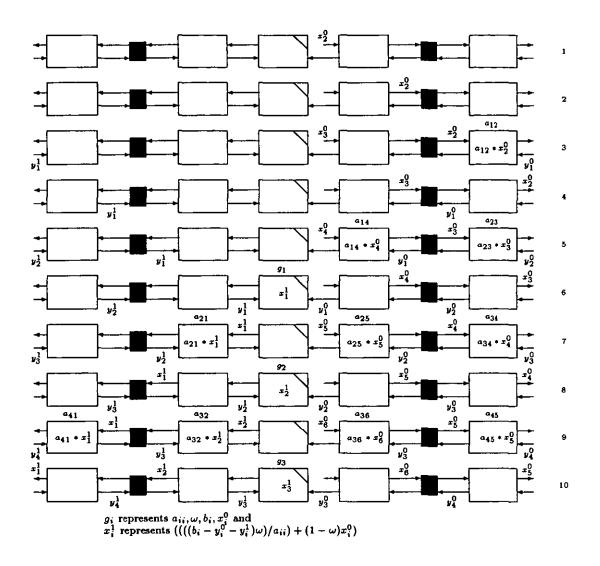

| 6.7  | 1 <sup>st</sup> 10 snap shots for the S.O.R. iterative method 197                    |

| 6.8  | 3D design for the S.O.R. systolic array                                              |

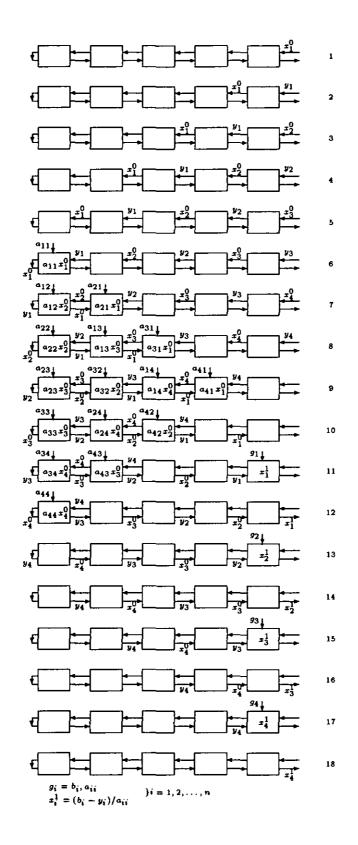

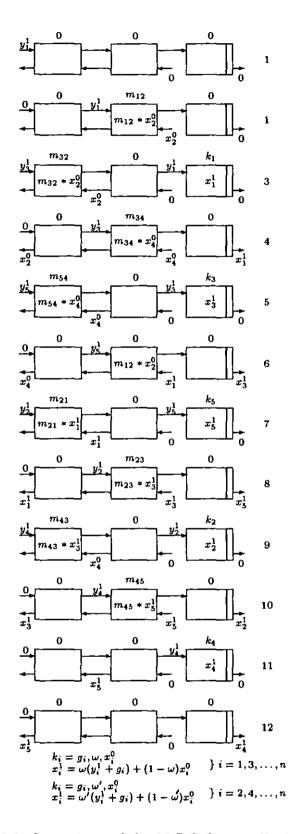

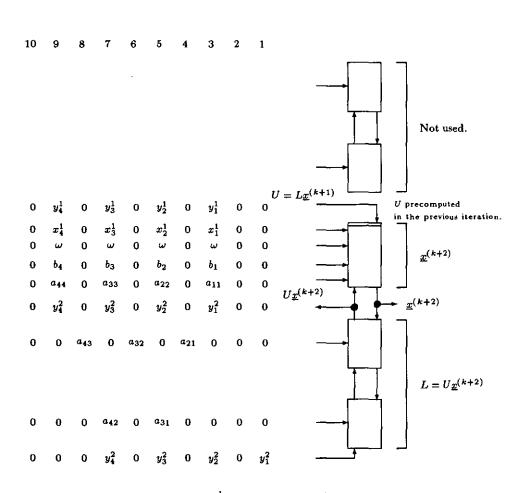

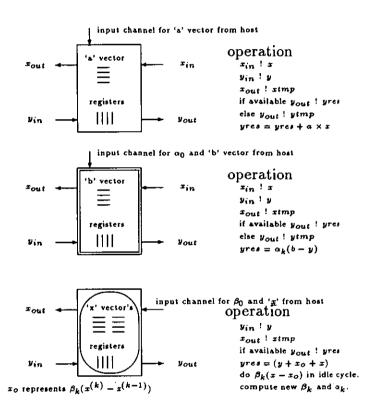

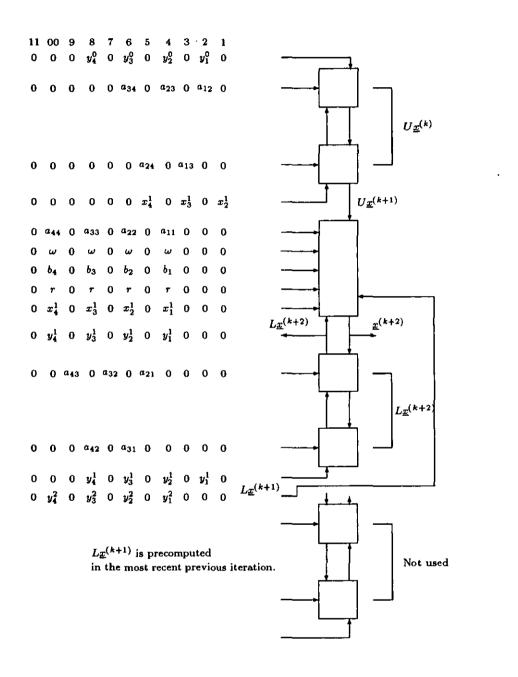

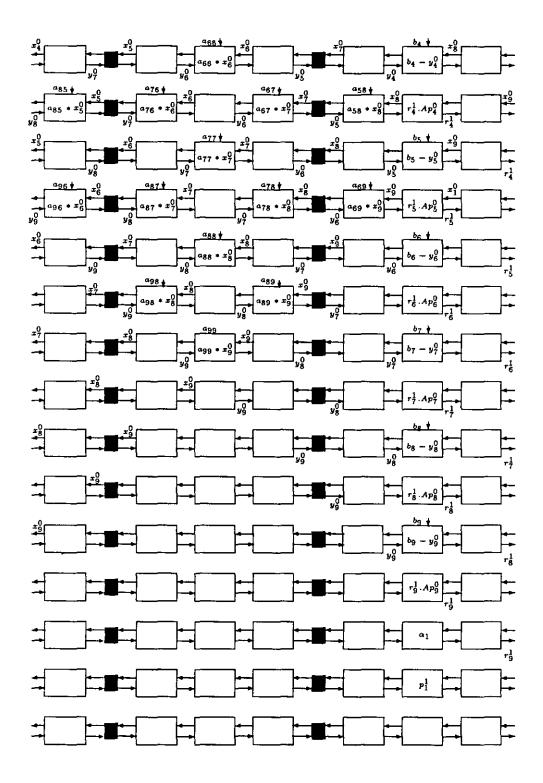

| 6.9  | Snap shots for the $2^{nd}$ iteration of the C.G. iterative method 205               |

| 6.10 | Snap shots for the $2^{nd}$ iteration of the C.G. iterative method 206               |

| 6.11 | Snap shots for the $2^{nd}$ iteration of the C.G. iterative method 207               |

| 6.12 | Snap shots for the $2^{nd}$ iteration of the C.G. iterative method 208               |

| 6.13 | Snap shots for the $2^{nd}$ iteration of the C.G. iterative method 209               |

| 6.14 | Snap shots for the $2^{nd}$ iteration of the C.G. iterative method 210               |

# List of Tables

| 3.1 | Statistics for matrix vector multiply                                    |

|-----|--------------------------------------------------------------------------|

| 3.2 | Time, area and utilisation of the Jacobi iterative method 99             |

| 3.3 | Time, area and utilisation of Guass-Seidel iterative method 105          |

| 4.1 | Area and time requirements for M.S.O.R. design 1                         |

| 4.2 | Area and time requirements for M.S.O.R. design 2 127                     |

| 4.3 | Area and time requirements for S.S.O.R. iterative method 131             |

| 4.4 | Area and time requirements for the improved S.S.O.R. design 135          |

| 5.1 | Area and time requirements for the stationary and nonstation-            |

|     | ary second order Richardson iterative method                             |

| 5.2 | Combination of $\omega$ and $r$ to yield different iterative methods 169 |

| 5.3 | Area and time requirements for the S.A.O.R. iterative method 176         |

| 6.1 | Number of Virtual IPS cells vs Grid points                               |

| 6.2 | Area and time requirements for the 2D-J.O.R. systolic design 191         |

| 6.3 | Iteration count for the J.O.R. iterative method for different sizes      |

|     | and $\omega$                                                             |

| 6.4 | Iteration counts for the S.O.R. iterative method for different           |

|     | sizes and $\omega$                                                       |

| 6.5 | Iteration counts for the S.O.R. iterative method for different   |

|-----|------------------------------------------------------------------|

|     | sizes and $\omega$                                               |

| 6.6 | Area and time requirements for the 2D-C.G. systolic design 204   |

| 6.7 | Area and time requirements for the 2D-P.C.G. systolic design 214 |

| 6.8 | Iteration counts for various iterative methods for model problem |

|     | 1                                                                |

| 6.9 | Iteration counts for various iterative methods for model problem |

|     | 2                                                                |

# Chapter 1

# Introduction and Fundamentals of Parallel Computer Architectures

This chapter provides introduction to the thesis, an overview of parallel processing and different system organizations. Increased computational applications, new computer technologies and novel concepts in system organizations have lead to an increasing interest in highly powerful and reliable computer architectures. Several approaches have been developed to increase the power and throughput of the conventional Von Neumann architecture. Pipelining is used to achieve concurrency on a time overlap basis. The idea of having several memory units instead of one, is used to fetch the operands concurrently from separate memory units, thus improving throughput. The use of more than one processor to solve large problems fast gave birth to the field of parallel processing.

## 1.1 Introduction

The solution of many important problems related to scientific and engineering applications require solving large systems of linear equations. Examples include fluid dynamics, weather predictions, aircraft design, structural problems and many others. These systems arise from modeling with partial differential equations by the use of finite difference/element methods. Thus, solving large systems of equations has been a central issue in numerical methodology and analysis. Two basic families of methods for solving systems can be distinguished: direct and iterative. There are times that one should prefer to use a direct method but the opposite is also true.

Besides being important from this point of view, developments in computer technology bring additional interest to the study of iterative methods. Although some well known iterative schemes are very old, it was the growth of digital computers and their increased use in solving the partial differential equations that triggered considerable new interest in the area. Thus, the fifties and sixties became the period in which most of the significant results on iterative methods were produced. Memory limitations, that adversely affect direct methods, were the main reason for this. The memory and speed of computers have increased dramatically since then, but so has the computational needs of researchers and developers, reaching the point of requiring the solution of systems with millions of unknowns. The development of parallel and vector computers changed the nature of numerical algorithms. Computer algorithms and architectures became closely related and affect each other. Then in the new super computer architectures, communication costs and bottlenecks became a major limitation in the efficient implementation of algorithms. The developments in micro-electronics have revolutionised computer design. Integrated circuit technology has increased the number and complexity of components that can fit on a chip. The Very Large Scale Integrated (VLSI) technology makes it feasible to build low-cost special purpose designs to rapidly solve sophisticated problems. Iterative methods seem to behave considerably better than direct methods, thus attracted renewed interest.

This work is motivated not only by the importance of the iterative methods, as explained above, but also by the unresolved issues that these methods present.

With the exception of the Jacobi iterative method (which, when it converges, converges slowly), known iterative methods do not present inherent parallelism. One solution to this problem requires modification of existing methods or to discover new methods with increased parallelism. The other solution is to select existing computer architectures or design new ones that are most suitable for the implementation of parallel iterative methods. The designs developed will have different hardware requirements and execution times. So the design may be implementable but too expensive (difficult) to fabricate. Even if some methods are implementable, convergence may be too slow. Of the many methods one often does not know which one will converge significantly fast and definitely one will prefer to use the fastest possible. This leads to discover better implementation schemes in terms of parallelism. The issues related to the practical implementation will not be dealt with in this thesis.

Rest of this chapter briefly describes the different parallel computer organisations.

Chapter 2, contains basic mathematical definitions in the areas of numerical solution of the systems of linear equations and the discrete approximation to the solution of partial differential equations. Some basic matrix iterative methods are explained briefly as well.

Chapter 3, is an introduction to the basic concepts of the systolic approach in parallel processing. It starts with a description of the basic building block of the systolic design. Later in the chapter, the matrix vector multiplication example is presented on a linear systolic array, proposed by H. T. Kung. Then different techniques to improve the utilisation of the array, and to decrease the chip area are explained. We implement these new ideas to the basic iterative

methods and describe their usefulness.

Chapter 4, describes the systolic implementation of the S.O.R. and S.S.O.R. iterative methods on the linear systolic array. The Conrad-Wallach strategy is implemented in order to reduce the iteration time of the array and hence the computational work is reduced to that of the S.O.R. iterative method.

Chapter 5, describes the first and second order stationary and nonstationary Richardson iterative methods. The A.O.R. iterative method and the S.A.O.R. iterative method are also described. The systolic implementation of these methods are developed. A similar strategy as Conrad-Wallach is applied to the S.A.O.R. iterative method. Different pipelining techniques to improve the utilisation are shown and explained.

Chapter 6, presents the systolic designs for the 2-dimensional and 3-dimensional problems obtained from the discretisation of partial differential equations. The discretised problems are solved using the J.O.R., S.O.R. and second order Richardson (with and without Chebyshev acceleration) iterative methods. Later we explain the Conjugate Gradient and Preconditioned Conjugate Gradient methods and implement them systolically.

Chapter 7, completes this thesis with a review of the main results and some general conclusions, that reflect the research areas mentioned in this thesis. A list of references is also given, consisting of material covering a wide spectrum of research interests in the systolic systems and computing.

# 1.2 Architectural configuration of parallel computers

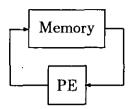

The Von Neumann computer model (classical sequential model) of computation consists of a stream of instructions and a stream of data, executing one instruction at a time, to produce a computational result, as shown in figure (1.1). The Von Neumann architecture is improved by using multiple proces-

Figure 1.1: Von Neumann computer model.

sors that can communicate and cooperate, which gave birth to the field of parallel processing (see Almasi and Gottlieb [1]). Parallel computers can be classified according to their architectures namely; Pipelined computers, Array processors, Multiprocessor systems, Data flow computers and VLSI algorithmic processors. Data flow computers and VLSI algorithmic processor architectures demand extensive hardware to achieve parallelism. The revolution brought by the VLSI technology has made these two approaches an interesting research area.

# 1.2.1 Pipelined computers

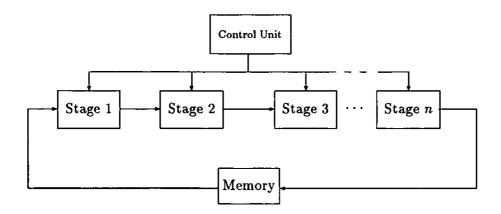

Pipelined computers have emerged and received considerable attention as an attribute and an economical way of speeding up computer systems. Pipelining offers an economical way to realise "temporal" parallelism in digital computers. The pipelining approach is based on the fact that the execution of many machine instructions consumes several clock periods, usually using the same hardware iteratively. If such hardware is replicated serially, then a number of operations may be streamed into the processors at the same time and be executed in an overlapped fashion. Hence input tasks (processes) must be divided into a sequence of subtasks, each of which can be executed by a specialised hardware stage that operates concurrently with other stages in the pipeline. Therefore, a pipeline processor can be described as consisting of a sequence of processing circuits, called segments or stages, through which the data stream

Figure 1.2: n-stage pipelined computer.

passes. The data is processed partially by each segment and the final result is obtained after the data has passed through all the segments of the pipeline. The result stream returns to memory. Here parallelism is achieved by having distinct operand sets or processes manipulated in several segments at the same time (see Hennessy and Patterson [38], Baer [3]). Figure (1.2) shows a schematic diagram of an n-stage pipelined machine. Due to the overlapped instruction and arithmetic execution, it is obvious that pipeline machines are better tuned to perform the same operations repeatedly through the pipeline. Whenever there is a change of operation, say from "add" to "multiply", the arithmetic pipeline must be drained and reconfigured, which will cause extra time delays. Therefore, pipeline computers are more attractive for vector processing, where component operations may be repeated many times such as in matrix computations.

Now to explain how parallelism can be achieved by pipelining, let us consider the process of executing an instruction. Usually the process of executing an instruction in a digital computer involves four major steps: fetching the instruction (IF) from the main memory; decoding it (ID) to identify the operation to be carried; fetching the operand(s) (OF) if required; and finally the execution (EX) of the decoded arithmetic logic operation. If this process is to be carried out in a non-pipelined computer, then these four steps must be

| Instruction i |    |    | Instruction i+1 |    |    |    | Instruction i+2 |    |    |    | Instruction i+3 |    |    |    |    |

|---------------|----|----|-----------------|----|----|----|-----------------|----|----|----|-----------------|----|----|----|----|

| IF            | ID | OF | ΕX              | IF | ID | OF | EX              | IF | ID | OF | EX              | IF | ID | OF | EX |

Figure 1.3: Non-pipelined execution.

| Instruction | Pipe Cycle |    |    |    |    |    |    |  |  |  |

|-------------|------------|----|----|----|----|----|----|--|--|--|

| number      | 1          | 2  | 3  | 4  | 5  | 6  | 7  |  |  |  |

| i           | IF         | ID | OF | EX |    |    |    |  |  |  |

| i+1         |            | IF | ID | OF | EX |    |    |  |  |  |

| i+2         |            |    | IF | ID | OF | EX |    |  |  |  |

| i+3         |            |    |    | IF | ID | OF | EX |  |  |  |

Figure 1.4: Pipelined execution.

completed before the next instruction can be issued, as can be seen from the space-time diagram in figure (1.3) for the non-pipelined processor.

In a pipelined computer, successive instructions are executed in an overlapped fashion, by the four pipelined stages, IF, ID, OF and EX, which are arranged into a linear cascade (see figure 1.4).

An instruction cycle consists of multiple pipeline cycles. A pipeline cycle can be set equal to the delay of the slowest stage. The operation of all stages is synchronised under a common clock control. For non-pipelined computers it takes four pipeline cycles to complete one instruction. Once a pipeline is filled up, an output result is produced from the pipeline on each cycle. The instruction cycle has been effectively reduced to one-fourth of the original cycle time by such overlapped execution. According to the levels of processing Handler, in [36], classified the pipeline processors into three classes which are:

- Arithmetic pipelining: These processors have been constructed for performing either a single arithmetic function or the four basic operations on both fixed- and floating-point numbers.

- Instruction pipelining: The purpose of such a pipeline is to overlap

the execution of the current instruction with the subsequent instruction stages. This is done by the decomposition of instruction execution

into a linear series of autonomous stages e.g. fetch, decode etc.

- Processor pipelining: In this type of pipelining, a cascade of processors, each with a specific task, process the same data stream. The first processor manipulates the passing data stream and the results are stored in a memory block which is accessible by the second processor. The 2<sup>nd</sup> processor passes the refined data stream to the third processor and so on.

The first two classes are "low-level parallelism" and hence are excluded from the set of parallel architecture. There are two reasons for such exclusion; the first one being that the failure to adopt a more restrictive standard might make the majority of modern computers "parallel architecture" negating the term's usefulness. The second reason is that architectures having only these features do not offer an explicit, coherent framework for developing high-level parallel solutions. Theoretically, the maximum speed-up that can be gained from a pipeline processor with n-stages is n, i.e. when the pipeline is full. However, in practice this perfect speed-up cannot be achieved due to memory conflicts, data dependency, program branches and interrupt handling. Some of the most obvious machines that use pipelining technology are: IBM 360/195, CDC STAR, and the University of Manchester MU5 computer.

# 1.2.2 Array processors

An array processor can be defined as a synchronous parallel computer with multiple arithmetic logic units called processing elements (PE's). Those processing elements are controlled by a single control unit (CU) i.e. processor only operates on command from control unit. Each PE is independent i.e. has its own registers, an arithmetic and logical unit (ALU) and a local memory. "Spatial" parallelism can be achieved by the replication of the ALU's.

Two essential reasons were behind the idea of building array processors. The first is an economic reason for it is cheaper to build n processors with only one control unit rather than n similar computers. The second reason is that the communication bandwidth, of the interprocessor communication, can be fully utilised.

The PE's are passive devices without instruction decoding capabilities and they are synchronised to perform the same function at the same time. The control unit fetches and decodes the instructions and broadcasts the data, i.e. vectors to the PE's for distributed execution over different components. Operands are fetched directly from the local memories. Scalar and control instructions are directly executed in the control unit itself.

Different array processors may use different interconnecting patterns among the PE's. In order to maximise the parallelism in an array processor, utilisation of the available memory and processor bandwidths must be very high.

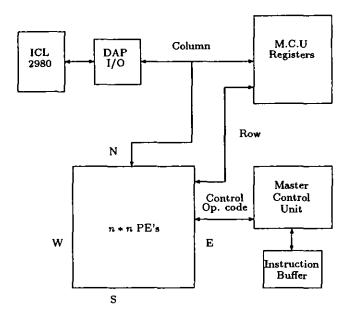

An example of an array processor is the ICL DAP computer. Figure (1.5) is a schematic diagram of the general structure of this machine.

The ICL DAP has simple identical processing elements (upto 4096 processors, arranged in a  $(64 \times 64)$  grid). A single master processor broadcasts program instructions to individual PEs which execute the same instruction on their respective data items. In the DAP, the PEs are connected in a square array. Each PE can simultaneously shift one bit in one direction and receive a bit from the opposite direction. Repeated shifts can move large volumes of data

Figure 1.5: ICL DAP architecture.

from any part of the grid to any other. This is a basic example of a vector or array processor.

Speedup is achieved compared to the Von Neumann model as there is no separate instruction fetch for each data item, and the execution of the data items is done in parallel. This is an expensive solution as multiple processing elements are required. The operational speed of an array processor is supposed to increase linearly as the number of the PE's is increased. However, this is not the case due to the interprocessor communication and the data access overheads.

Some of the application areas that have been suggested as suitable for array processors and in particular for the Illiac IV, the BSP, the MPP and the STARAN systems include: Matrix algebra (multiplication, decomposition, inversion), matrix eigenvalue calculation, linear and integer programming, weather modeling, beam forming and convolution, filtering and Fourier analysis, image processing and pattern recognition, wind-tunnel experiments, automated map generation, and real-time scene analysis.

The above list is by no means exhaustive. Most of these applications need to process spatially distributed data.

# 1.2.3 Multiprocessor systems

Multiprocessor systems have been developed as part of the research efforts aimed to improve the speed, reliability, throughput and availability of computer systems. A multiprocessor system is defined in the American National Standard Vocabulary of Information Processing as "a computer employing two or more processing units under integrated control". This definition is not complete as the concept of sharing and interaction, which are at the core of the techniques of multiprocessing are not included in the ANSI definition. Enslow, in [13], defines the multiprocessor system which has the following characteristics.

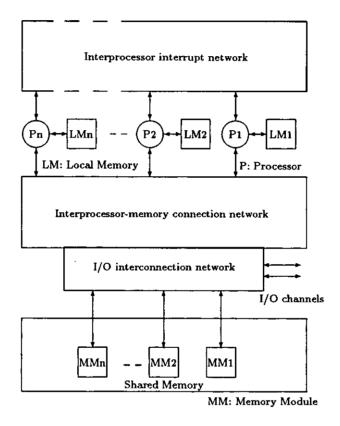

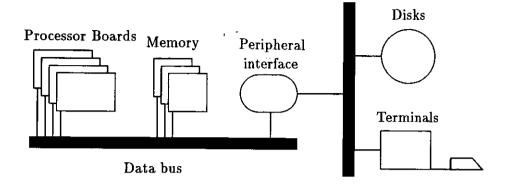

A multiprocessor system contains two or more processors of approximately comparable capabilities. All processors share access to common memory modules, I/O channels and peripheral devices. Most importantly, the entire system is controlled by one operating system which provides interactions between processors and their programs at various levels. Each processor has its local memory and private devices. Figure (1.6) shows a basic multiprocessor organisation.

Processors, in these systems can communicate with each other, either through the shared memory or through an interrupt network. This interconnecting structure between the memories and the processors and between memories and I/O channels is the primary determination of multiprocessor hardware system organisation.

Among these interconnecting structures, three fundamental types have been identified by Hwang and Briggs, in [41], to be used in multiprocessors.

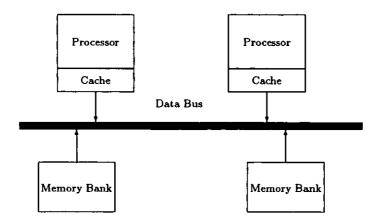

## 1. Time-shared/Common bus

Figure 1.6: Multiprocessor architecture.

Figure 1.7: Time-shared bus (single bus) multiprocessor.

This is the simplest interconnecting structure for either single or multiple processors system. It consists of a common communication path (single bus) connecting all of the functional units, in which each one of them consists of a number of processors, memories and I/O devices.

The time shared bus involves the lowest overall system cost for hardware as the bus can be a simple multiconductor cable, and hence is least complex. The system configuration can be physically modified simply by adding or removing the functional units. However, expanding the system by the addition of functional units may degrade the overall system performance and hence is suitable for small systems. The major draw back of this organisation is that a bus failure halts the entire system. Figure (1.7) illustrates a general scheme of a common bus multiprocessor system.

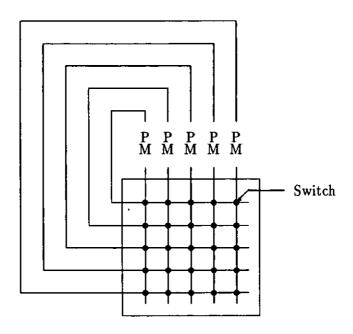

#### 2. Cross-bar switch network

To overcome the major drawback of the time-shared bus organisation mentioned earlier, the crossbar switch networks are used.

The crossbar interconnecting technology uses a crossbar switch of PxM cross points to connect P processors to M memories. Thus, the interconnections between processors and memory units are increased in such a

Figure 1.8: Crossbar switch network multiprocessor.

way that each processor is allowed to have equal access to any nonbusy memory unit. Therefore, each memory unit (M) has its own separate path to a processor (P) as shown in figure (1.8).

The crossbar switch is the most complex interconnection system. The functional units are the simplest and hence cheapest because the control and switching logic is in the switch. The main characteristics of this organisation are the high throughput, highest potential for system efficiency. System expansion improves the overall performance, the expansion of the system is limited only by the size of the switch. Also, this organisation has the potential for the highest total transfer rate. It is quite easy to partition the system to isolate the malfunctioning devices or to establish independent systems. However, the system proves to be too costly (PM) and complex for highly parallel systems because of too many connections.

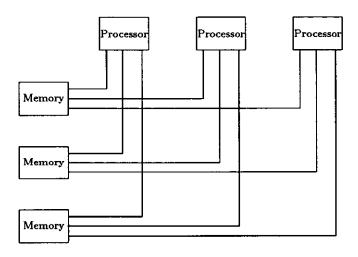

#### 3. Multiport memories

Figure 1.9: Multiport memories multiprocessor organisation.

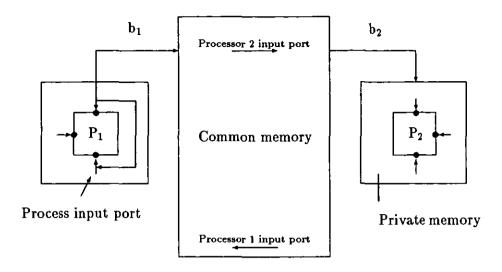

In this organisation, the switching is concentrated in the memory module. Each processor has access through its own bus to all of the memory modules. Conflicts are resolved by assigning a fixed priority to the memory ports. It is possible to designate a portion of the memory as private to certain processors, I/O units, or a combination of both. Figure (1.9) shows a multiport memory multiprocessor organisation. Multiport memory requires the most expensive units since most of the control and switching circuitry is included in the memory units. The system has a very high transfer rate. The size and configuration options are determined by the number and type of memory ports available, and this decision is made quite early in the overall design process and is difficult to modify. This organisation requires number of cables and connectors.

Cost wise, the time-shared bus is the cheapest and the crossbar is the most expensive. The memory modules of the multiport organisation must have additional logic in their controllers and hence become expensive. The time-shared bus allows easy expansions, but the performance of the systems degrades rapidly if the system bus is overloaded. In terms of reliability, the time-shared bus and crossbar switches appear equally poor. Finally, both

crossbar and multiport schemes allow maximum concurrency.

### 1.2.4 Data flow computers

The conventional Von Neumann machines are known as control flow computers because instructions are executed sequentially as controlled by a program counter. Therefore computation in such computers is done according to the flow of control in the program and each instruction is executed in turn making program execution inherently slow. To exploit parallelism in a program, data flow computers were developed. The basic concept behind this development is to schedule each operation in the function being carried out at run time when all the operands are available. The sequence of operations in the data flow computers obey the precedence constraints imposed by the algorithm rather than by the location of the instructions in the memory. The instructions in a program are not ordered, hence no program counter is required.

In theory, the amount of concurrency exploited in data flow machines is constrained by the availability of hardware resources, i.e. how many instructions can be executed simultaneously by the computer.

After executing the instruction, the result is distributed to all subsequent instructions, which make use of this partial result as an operand. In this way the data flow model of computation exploits the natural parallelism of algorithms. In computer architecture this makes it possible to create systems which can dynamically adopt their inner configuration to the natural structure of the algorithm being performed.

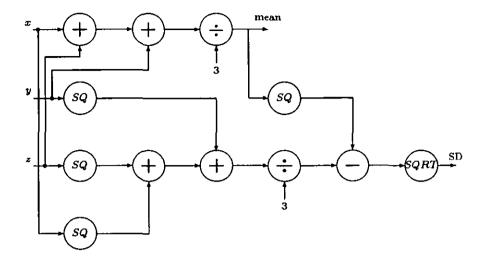

Programs for data-driven computations can be represented by "data flow graphs". An example of a data flow graph is given in figure (1.10) for the calculation of the mean and standard deviation (SD) given by following formulas:

$$mean = \frac{(x+y+z)}{3}, \tag{1.2.1}$$

Figure 1.10: Data flow graph for calculating mean and standard deviation.

$$SD = \sqrt{\frac{((x^2 + y^2 + z^2)}{3} - \text{mean}^2)}.$$

(1.2.2)

Miller and Cocke, in [58], designed the two basic models of data flow computer architectures which are:

- Search Mode configuration computer (SM-type).

- Interconnecting Mode configuration computer (IM-type).

Both models are characterised by the possibility of dynamic adoption of its configuration to the structure of the algorithms. This is done by interconnecting (according to the graph) the processors that correspond to the operators in the data flow program of the problem. The reconfiguration is done either by hardware or software means. In the IM-type, the interconnection between processors is actually implemented through a large switch, i.e. by hardware means. In the SM-type, the interconnection is simulated by using a special instruction format, i.e. by software means. Due to reconfigurability, the data flow computer is able to achieve the performance of a specialised system whilst still keeping its general purpose capabilities.

In data flow computers, information items are either operation packets or data tokens. An operation packet is composed of the op-code, operands and destination of its successor instructions. A data token is formed with a result value and its destinations. Depending on the way these data tokens are handled, data flow computers are subdivided into a static model or a dynamic model.

The static model of data flow computers provides a fixed amount of storage per arc, i.e. only one data token is allowed to exist on any arc at any given time, otherwise the successive sets of tokens cannot be distinguished. In the dynamic model the machine uses tagged tokens so that more than one token can exist in an arc at the same time. An architectural comparison of data flow machines is described in Srini [72].

### 1.2.5 VLSI systems

As a result of the advancement in large-scale integration (LSI) technology, Very Large-Scale Integration (VLSI) technology has been developed. In this technology, circuit designs were introduced in which the number of transistors has been increased by a factor of 10 to 100 compared to the LSI technology. The VLSI technology has made possible for a 32-bit processor with memory and I/O support to be fabricated on a single chip.

The main advantages offered by the VLSI technology are; its capacity to implement enormous number of devices on a chip, at a very low cost, reduced power consumption and physical size, and reliability. Additionally, the high level of integration conceivably eliminates the need to physically separate processors from the memory, thus eliminating the bottleneck between them. The main problem with VLSI technology is to overcome the design complexity. This problem can be solved by using regular design structures e.g. a memory chip. Software tools as well as hardware aspects are becoming more and more important in the design and testing stages of VLSI circuits. This leads to the

fact that the production of a new chip requires software as much as hardware engineering knowledge.

The two major difficulties exercised by conventional computers are the separation between the processor from its memory and the limited opportunities for concurrent processing. By using VLSI technology it became possible to overcome these difficulties because memory and processing architecture can be implemented with the same technology and by their close proximity. Beside that the potential power of VLSI has come from the large amount of concurrency that the technology supports.

The degree of concurrency or parallelism in VLSI computing structure is largely determined by the underlying algorithm. The I/O bottleneck problem in VLSI systems presents a serious restriction imposed on the algorithm design. The challenge is to design parallel algorithms which can be partitioned such that the amount of communication between modules is as small as possible. Enormous parallelism can be obtained by introducing a high degree of pipelining and multiprocessing while designing the algorithm. Properly designed parallel structures that need to communicate only with their nearest neighbours will gain the most out of the VLSI design.

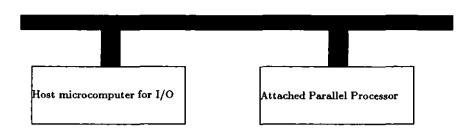

One way of achieving parallelism is by attaching a special-purpose parallel processor to the system bus of a microcomputer to speed-up the compute-bound algorithm rather than the I/O-bound computation. In a compute-bound algorithm, the number of computing operations is larger than the total number of I/O operations. Otherwise, the problem is I/O-bound. The attached parallel processor shown in figure (1.11) has two general architectural designs. The first being the multiprocessor lattice architecture based on the idea of several processing elements operating under centralised control and the second is a systolic array architecture which makes extensive use of pipelining.

A multiprocessor lattice architecture is an (n\*n) array of processing elements working concurrently under a centralised control and transmitted via a long

Figure 1.11: Achieving parallelism by using a special-purpose parallel processor.

local communication path connecting neighbouring processing elements. Each processing element has a private memory to store both results and any other temporary values which might be needed. The ICL DAP (see figure 1.5) is an example of an array lattice architecture. Designing a VLSI systolic system it is assumed that the processing cells (elements) in the array can be of different types and perform different operations. However, one design goal is to reduce the number of processing cell types.

The mapping of algorithms into systolic arrays is different than mapping of algorithms into architectures with fixed number of processors and interconnections. In case of systolic arrays, one has to deal with issues ranging from the organisation of the network of processing elements to the detailed operation of the processing elements. In fact, the mapping is the design of the VLSI array according to the properties of the algorithm and a set of design goals.

The design and implementation of a VLSI array can be broken into three main phases; task definition, design and processing (see Kung [44]). The design phase can be subdivided into system level, algorithms, logic circuit level and geometric layout. The processing phase concentrates on pattern generation, mask generation, wafer fabrication, device packaging and circuit testing.

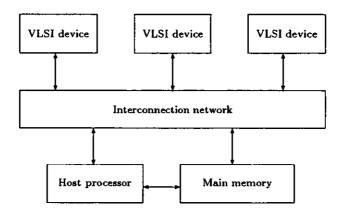

A computer organisation can be obtained by having several special purpose VLSI processor arrays connected to the host computer and main memory via an interconnection network, (see Moldovan [60]). Figure (1.12) presents such a

Figure 1.12: Computer system with several VLSI processor arrays.

design, the idea is to improve the performance of an existing computer system, using VLSI array processors. For example a systolic VLSI device implementing linear algebra routines can be built and connected to the system bus. The host computer when required calls these hardware routines by downloading the data into the device, and collects the results when available. Such devices are known as hardware accelerators (see Megson [56]). Each VLSI device consists of a number of processors working in parallel. The systolic array can be defined according to Kung and Leiserson, in [46], as a computing structure for making use of special-purpose VLSI chips.

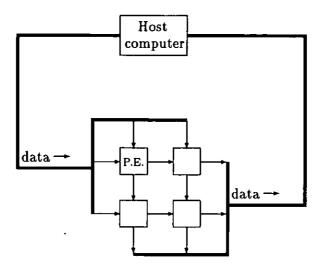

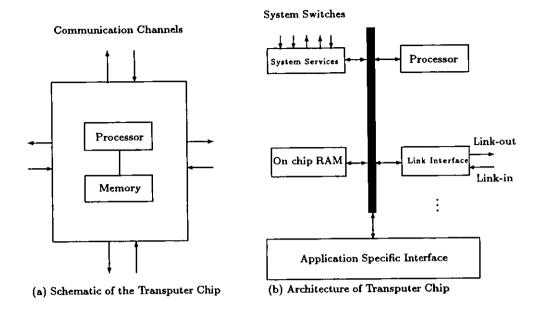

A chip based on a systolic design consists, essentially of a few types of very simple cells (processing elements) which are mesh-interconnected in a regular and modular way and which achieve high performance through extensive concurrent and pipeline use of the cells. Figure (1.13) shows the basic principles of a systolic array.

The name systolic given by Kung and Leiserson is taken from the physiology of living cells. A "systole" is a contraction of the heart by means of which blood is pumped to the different components of the organism. In the systolic system, the information (data and instructions) is rhythmically given into a structure of elementary processors (cells) to be processed and passed to a neighbour cell until a result reaches some boundary of the system communicating with the

Figure 1.13: Systolic processor array.

host computer.

The speedup obtained in systolic arrays is not linear. The computational time can be divided into a parallel portion and serial portion. The speedup is asymptotically limited by the serial portion (performed on a single processor); independent of the parallel portion. This principle is known as Amdahl's law. If there are a sequence of 100 operations to be performed in parallel, compared to a single processor machine an 80 processor machine would attain a speedup of 5 or less but not 80! Similarly systolic arrays have the Von Neumann bottleneck. Systolic arrays have applications in the field of numerical problems, signal processing, pattern recognition.

# 1.3 Classification of computer systems

The Von Neumann model (classical sequential model) of computation consists of a stream of instructions and a stream of data, executing one instruction at a time, to produce a computational result, as shown in figure (1.1). The Von Neumann architecture is improved by using multiple processors and gave birth

to the field of parallel processing. Flynn, in [23], give a taxonomy to classify these computational models as follows.

A computer architecture, can be classified in terms of parallelism within the data stream and instruction stream. A stream simply means a sequence of items as executed or operated on by a processor. In this context, instruction stream means the sequence of instructions that are executed in a processing unit and data stream means the sequence of operands that are manipulated in a processor.

Flynn classified computer systems into four classes according to the replication of instruction streams and data streams. These classes which are demonstrated in figure (1.14) are:

- 1. Single-Instruction Single-Data stream (SISD): This, in fact, is the sequential computer (Von Neumann machine), where at any time, only one instruction is in execution affecting at most one item of data.

- 2. Single-Instruction Multiple-Data stream (SIMD): This is a class of computers in which the data stream has been replicated. Therefore, each instruction operates on a data vector rather than on a single operand. One well known class of SIMD machines is the array processors (e.g. Illiac IV which contains an array of 64 fast floating point processors). Other SIMD computers, like the Distributed Array Processor (DAP), Connection machine are the classical examples.

- 3. Multiple-Instruction Single-Data stream (MISD): Here in this class the replication is in the instruction stream instead of the data stream. Each operand is operated upon simultaneously by several instructions. This mode of operation is generally unrealistic for parallel computers. The nearest example for such a machine is the punched card processor (see Stone [74]). There has been no commercial machine built of this type.

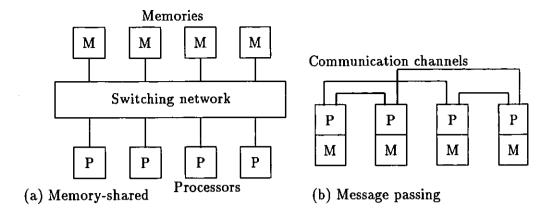

4. Multiple-Instruction Multiple-Data stream (MIMD): In this type of machine parallelism is combined in both the instruction and data streams. A computer system of this class is composed of n processors each of which is a complete computer with the processors connected together to provide a means for cooperating during computation.

Multiprocessors are a subclass of MIMD systems in which processors have common access to the primary memory and I/O channels with a single operating system controlling the entire complex. Shared memory machines like (Sequent Balance) and distributed memory systems (The Hypercube and Transputer networks) discussed later in this chapter are the examples of MIMD machines.

Of the four types of computer systems mentioned above, the two of immediate interest are the SIMD and MIMD computers. These two types, which will be discussed in more detail later, are vastly different in how they attain parallelism of operations.

Flynn's macroscopic classification of parallel architecture does not depend on the structure of the machines, but rather on how the machine relates its instructions to the data being processed. Therefore, this classification scheme can be considered too broad.

Other classification schemes were designed depending on different criteria. One of these classifications is Shore's classification (see Shore [68]) which was based on how the computer is organised from its constituent parts. According to this criteria six different types of machines were recognized. These types which are distinguished by a numerical designator are:

- Machine I: This is the conventional Von Neumann computer with one control unit, one processing unit, an instruction memory and a data memory. This data memory reads all bits of any word for processing in parallel by the processing unit.

- Machine II: Same as machine I except that the data memory reads a

#### S.I.S.D. Computers Instruction Data Control Unit Memory Processor stream stream S.I.M.D. Computers Data Memory 1 Processor 1 stream 1 Data Memory 2 Processor 2 stream 2 Instruction Control Unit stream Data Memory n Processor n stream nM.I.S.D. Computers Instruction Control Unit 1 Processor 1 stream 1 Instruction Control Unit 2 Processor 2 stream 2 Data Memory stream Instruction Control Unit n Processor nstream nM.I.M.D. Computers Instruction Data Memory 1 Control Unit 1 Processor 1 stream 1 stream 1 Instruction Data Memory 2 Control Unit 2 Processor 2 stream 2 stream 2 Instruction Data Memory n Control Unit n Processor n stream nstream n

Figure 1.14: Flynn's classification of computer systems.

bit slice from all words in memory instead of all bits of one word. The processing unit in this machine is organised to perform its operations in a bit-serial fashion.

- Machine III: Combination of machines I and II.

- Machine IV: This machine can be obtained by replicating processor units and data memory units of machine I.

- Machine V: This is machine III with additional facility that processor units are arranged in a line and nearest-neighbour connections are provided.

- Machine VI: In this machine processor logic is distributed throughout the memory and because of that it is called logic-in-memory array (LIMA).

Skillicorn, in [69], presented a classification scheme, or taxonomy, that extends Flynn's to make some discrimination. This taxonomy is based on a functional view of architecture and on the information flow between units.

Feng's scheme, in [21], is based on serial versus parallel processing. It is a performance oriented classification that describes the parallelism of the set of processors in a machine in terms of the number of bits that can be processed simultaneously.

Another approach used by Reddi and Feustel, in [65], made use of the physical organisation, information flow and representation and transformation of information as the basis for classification.

Handler, in [36], in his classification describes architectures by giving the number of processors and how they can be pipelined together.

# 1.3.1 SIMD computers