This item was submitted to Loughborough's Research Repository by the author. Items in Figshare are protected by copyright, with all rights reserved, unless otherwise indicated.

# Design and reliability of polymeric packages for high voltage power semiconductors

PLEASE CITE THE PUBLISHED VERSION

**PUBLISHER**

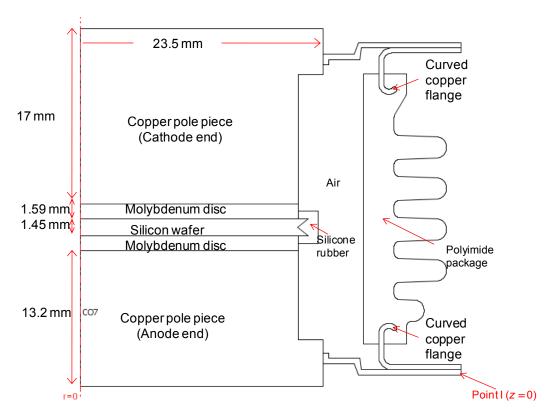

© N.S. Nadeesh

LICENCE

CC BY-NC-ND 4.0

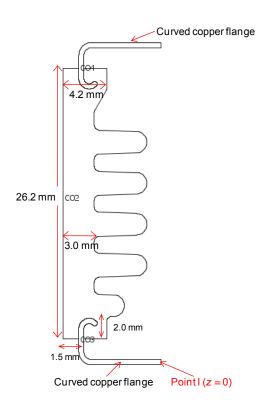

REPOSITORY RECORD

Nobeen, Nadeesh. 2019. "Design and Reliability of Polymeric Packages for High Voltage Power Semiconductors". figshare. https://hdl.handle.net/2134/8957.

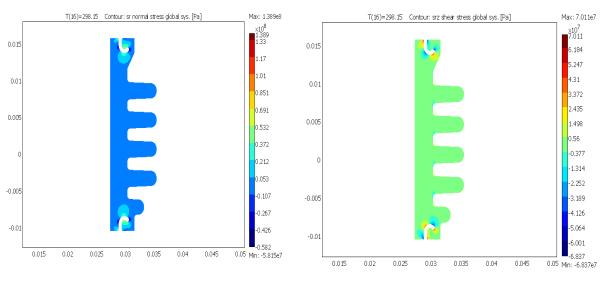

This item was submitted to Loughborough's Institutional Repository (https://dspace.lboro.ac.uk/) by the author and is made available under the following Creative Commons Licence conditions.

#### Attribution-NonCommercial-NoDerivs 2.5

#### You are free:

• to copy, distribute, display, and perform the work

#### Under the following conditions:

Attribution. You must attribute the work in the manner specified by the author or licensor.

Noncommercial. You may not use this work for commercial purposes.

No Derivative Works. You may not alter, transform, or build upon this work.

- For any reuse or distribution, you must make clear to others the license terms of

- Any of these conditions can be waived if you get permission from the copyright holder.

Your fair use and other rights are in no way affected by the above.

This is a human-readable summary of the Legal Code (the full license).

Disclaimer 🗖

For the full text of this licence, please go to: http://creativecommons.org/licenses/by-nc-nd/2.5/

# Design & Reliability of Polymeric Packages for High Voltage Power Semiconductors

Ву

N. S. Nobeen

Under the Supervision of Mr D. C. Whalley

Dr D. A. Hutt

#### **A Doctoral Thesis**

Submitted in partial fulfilment of the requirements

for the award of

Doctor of Philosophy of Loughborough University

May 2011

© by N. S. Nobeen 2011

### **Abstract**

This thesis focuses on the development of a novel polymer based housing for power thyristor devices typically used in long distance high voltage direct current (HVDC) transmission.

Power thyristor devices used in HVDC power conversion stations are typically packaged in a hermetically sealed ceramic housing and have demonstrated an excellent history of reliability and performance. However, to avoid increasing the number of thyristors in future higher powered HVDC schemes thyristors having higher power ratings at 8.5 kV and sizes at 125 mm and 150 mm diameters are sought for implementation to achieve higher transmission ratings of, for example, 4000 A at ±800 kV. The main disadvantages of such large ceramic-based packages are higher processing cost and weight whilst robustness is also a concern. To overcome these issues, replacing the current ceramic housing with a polymeric material has been investigated in this project. The advantages it is anticipated such packages will provide include lower cost, less weight, robustness, recyclability, etc. However, some challenges it will also offer are: non-hermeticity i.e. polymers are moisture and gas permeable, potentially more complex manufacturing routes, and different electrical, mechanical and thermal properties compared to ceramic materials. The work presented in this thesis was part of a larger project where these challenges have been addressed by developing and testing a prototype polymeric thyristor housing. The prototype is aimed at demonstrating that polymer packages can deliver performance and reliability comparable to, if not better than, current ceramic packages.

In this thesis, it is the package development and reliability related studies that are discussed. Because the housings will experience severe electrical stresses and various thermal excursions during their service life, the electrical and thermo-mechanical behaviour of the polymer housing was studied using finite element analysis to gain an understanding of the effects of various design variables and materials properties on performance and the tradeoffs

between performance and manufacturability. From these modelling studies, design guidelines have been established for the future development of polymer housings. On the other hand, to identify the physics-of-failure of the prototype that was manufactured as part of the project, accelerated life tests were performed to study its reliability. The knowledge gained from the polymer prototype development was then applied to the design of a larger 125 mm diameter housing using the Taguchi method of experimental design.

#### **Keywords:**

High voltage direct current, Power thyristor, Polymer package, Finite Element Analysis, Reliability study, Accelerated Life test, Taguchi method, Partial discharge, Dielectric breakdown

# Acknowledgement

I would like to take this opportunity to express my sincere thanks to the various people who have helped me in the process of my research.

I owe my deepest gratitude to Mr. David Whalley and Dr. David Hutt, my supervisors, for providing me the opportunity to work in this exciting project. Their expert academic advice, continuous support and constructive comments have been a great value for creating an enthusiastic environment to carry out my work efficiently. It was a great pleasure and privilege for me to have pursued my PhD under their supervision.

I also wish to thank immensely Mr. Barry Haworth from the Materials Department in Loughborough University, Mr. David Newcombe and Mr. Ashley Plumpton from Dynex Semiconductors Ltd, Mr. Ian James and Mr. Mark Donoghue from Areva (now Alstom Grid UK Ltd), and Mr. Geoff Lewis and Mr. Stef Degreef from DuPont™ for their kind support and advice during the project. Without their crucial help and collaboration, this work would have been unsuccessful.

My thanks are also due to the Engineering and Physical Sciences Research Council (EPSRC) and the Wolfson School of Mechanical and Manufacturing Engineering of Loughborough University in support of my studentship to undertake this research. I would also like to convey my appreciation to my research colleagues who played a vital role in getting me through my challenging research journey. Most specially my good friend, Dr. Lorenzo Cladi, who broadened my background in the Catenaccio and Sampdoria's limited history, and also supported me during the 'disappointing' CL and Premiership evenings when I have had to watch my team ending winless every year!

Finally, I also wish to dedicate this work to Eun for the continuous moral support and encouragement during my research and beyond; Avinash, who

has always been my best friend as well as the best brother in the world, has greatly supported me although being far away; and above all to my parents, Sunil and Bharatee, who have always encouraged me and my brother in every step of our lives. Without their love, prayers, moral support and never ending sacrifices, it would not have been possible for me to have the confidence to pursue a PhD and reach up to this level.

# **Table of Contents**

| 1 | Intr | oduction                                               | 1  |

|---|------|--------------------------------------------------------|----|

|   | 1.1  | Electricity Generation and Transmission                | 1  |

|   | 1.2  | HVDC Technology: an overview                           | 2  |

|   |      | 1.2.1 Future challenges of power semiconductor devices | 10 |

|   | 1.3  | NEWTON project overview                                | 11 |

| 2 | Rev  | view of thyristor housing designs                      | 16 |

|   | 2.1  | Introduction                                           | 16 |

|   | 2.2  | Thyristor packages                                     | 19 |

|   |      | 2.2.1 Hermetic housing designs                         | 19 |

|   |      | 2.2.2 Polymeric housing designs                        | 21 |

|   | 2.3  | Key design features of thyristors                      | 22 |

|   | 2.4  | Thyristor device failure modes                         | 26 |

|   |      | 2.4.1 Short circuit failure                            | 26 |

|   |      | 2.4.2 Explosion failure                                | 29 |

|   | 2.5  | Summary                                                | 32 |

| 3 | Fai  | lure modes of thyristor devices                        | 34 |

|   | 3.1  | Introduction                                           | 34 |

|   | 3.2  | Overstress failure mechanisms                          | 35 |

|   | 3.3  | Wear-out failure mechanism                             | 37 |

|   | 3.4  | Thyristor failures                                     | 39 |

|   | 3.5  | Reliability complexities                               | 42 |

|   |      | 3.5.1.1 Accelerated testing                            | 43 |

|   | 3.6  | 'Designing' reliability into the NEWTON device         | 45 |

| 4 | Res  | search Methodology                                     | 49 |

|   | 4.1  | Introduction                                           | 49 |

|   | 4.2  | Housing prototype design selection                     | 50 |

|   | 4.3  | Design considerations                                  | 52 |

|   | 4.4  | 50 mm prototype development                            | 58 |

| 5 | An   | overview of the Finite Element Analysis method         | 62 |

|   | 5.1  | Introduction                                           | 62 |

|   | 5.2  | Finite Element Analysis                                | 62 |

|   | 5.3  | Research Methodology                                   | 65 |

|   |      | 5.3.1 Comsol Multiphysics Background                   | 66 |

|   | 5.4  | Validation of Finite Element Methodology               | 69 |

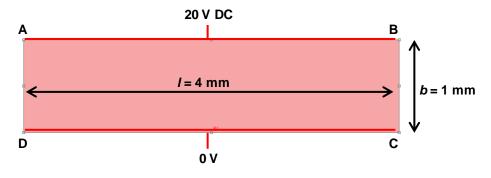

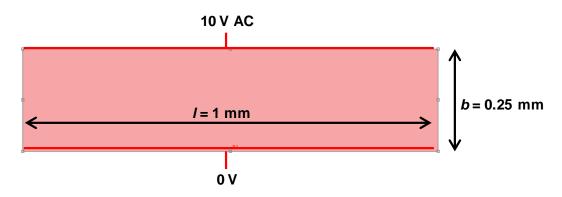

|   |      | 5.4.1 DC Simulation                                    | 69 |

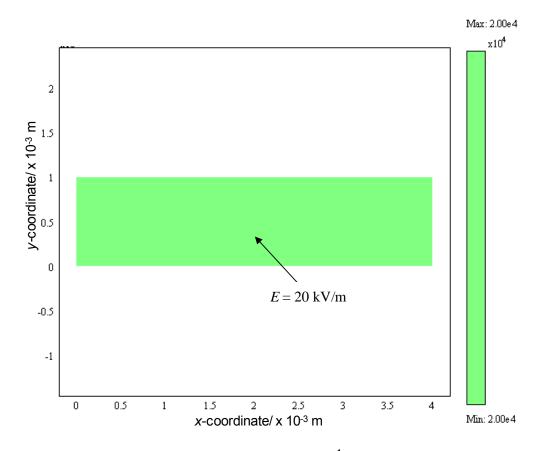

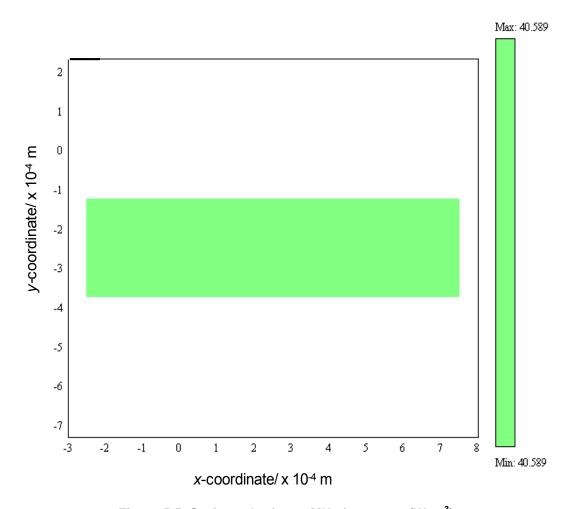

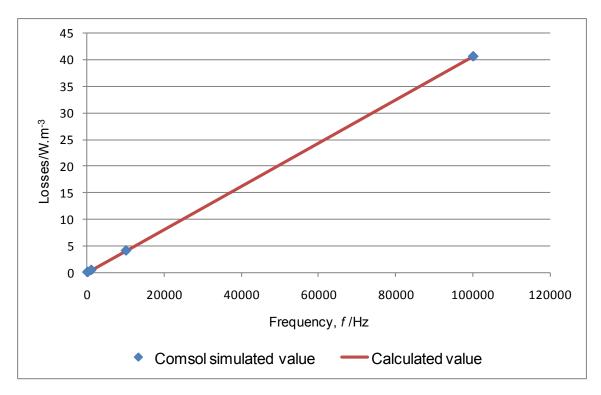

|   |      | 5.4.2 AC Simulation                                    | 72 |

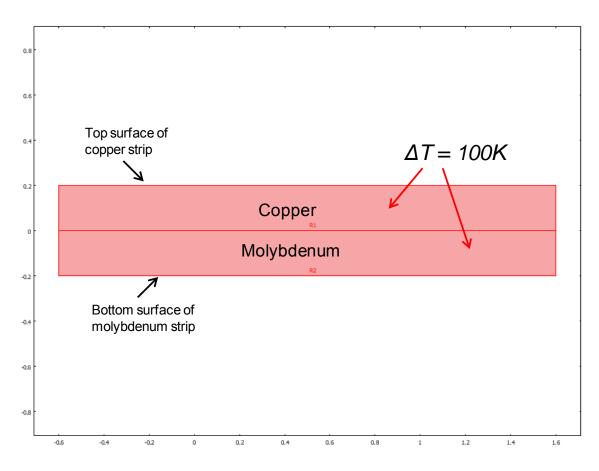

|   |      | 5.4.3 Thermo mechanical Simulation                     | 75 |

|   | 5.5         | Summary                                                                         | 78       |  |  |

|---|-------------|---------------------------------------------------------------------------------|----------|--|--|

| 6 | Ele         | ectrical performance studies for polymeric thyristor housings                   | 80       |  |  |

|   | 6.1         | Introduction                                                                    | 80       |  |  |

|   | 6.2         | Electrical Properties of Polymers                                               | 80       |  |  |

|   |             | 6.2.1 Electrical Behaviour of Polymers                                          | 82       |  |  |

|   |             | 6.2.1.1 Permittivity                                                            | 83       |  |  |

|   |             | 6.2.1.2 Relative Permittivity                                                   | 84       |  |  |

|   |             | 6.2.1.3 Loss tangent or Dissipation factor, tan δ                               | 84       |  |  |

|   |             | 6.2.1.4 Dielectric Strength                                                     | 86       |  |  |

|   |             | 6.2.1.5 Arc Resistance                                                          | 86       |  |  |

|   |             | 6.2.1.6 Comparative Tracking Index (CTI)                                        | 86       |  |  |

|   |             | Research Scope                                                                  |          |  |  |

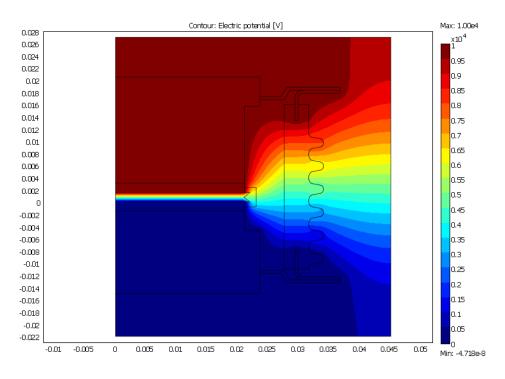

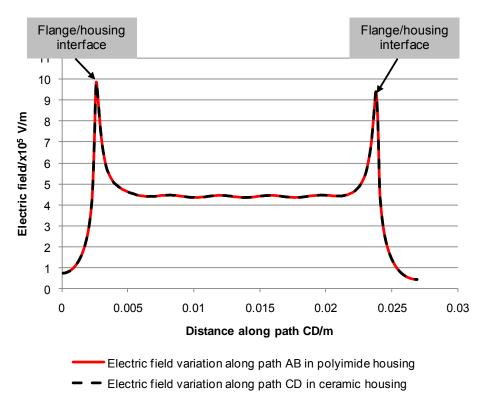

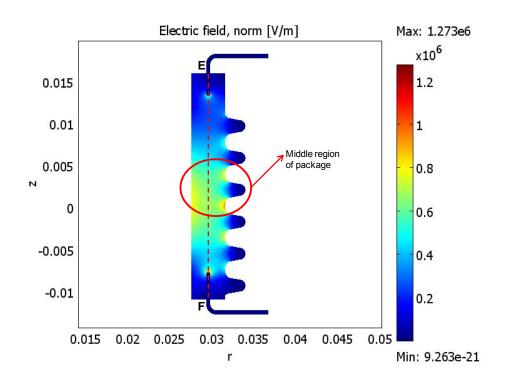

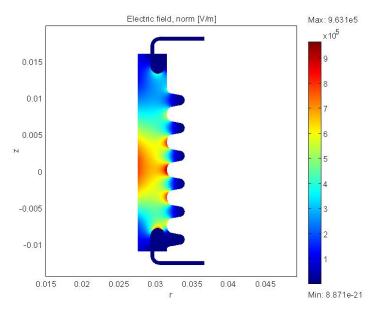

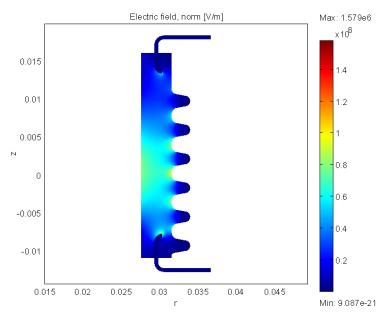

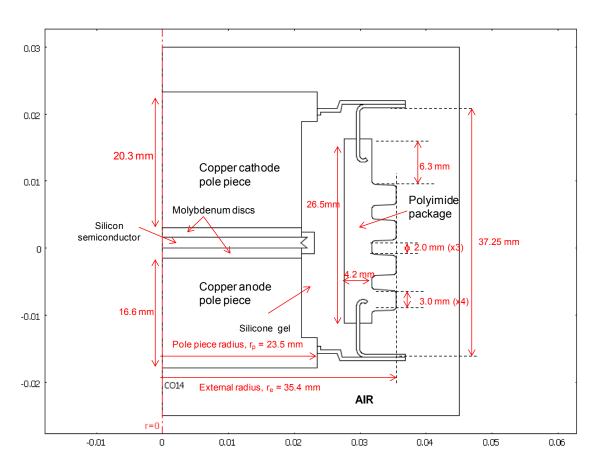

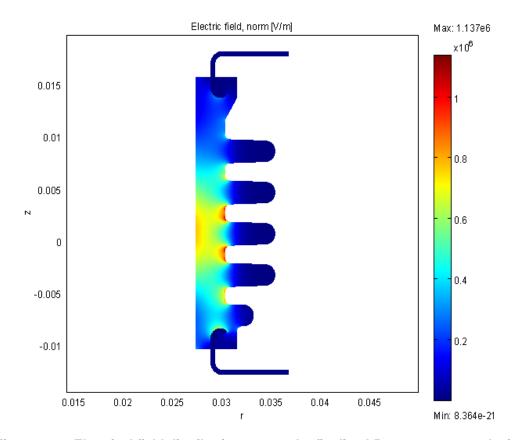

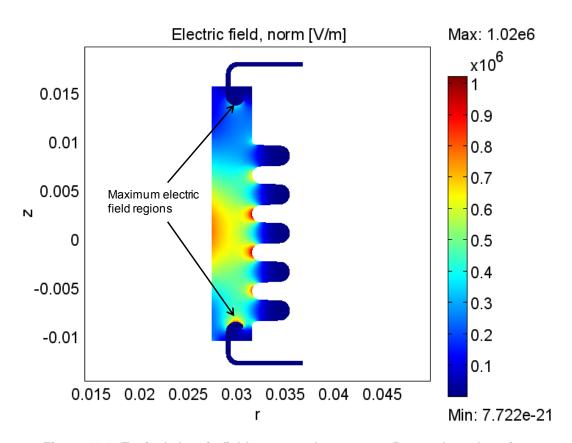

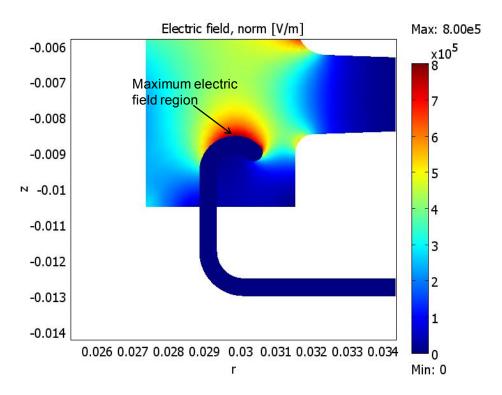

|   | 6.4         | DC Modelling Studies                                                            | 92       |  |  |

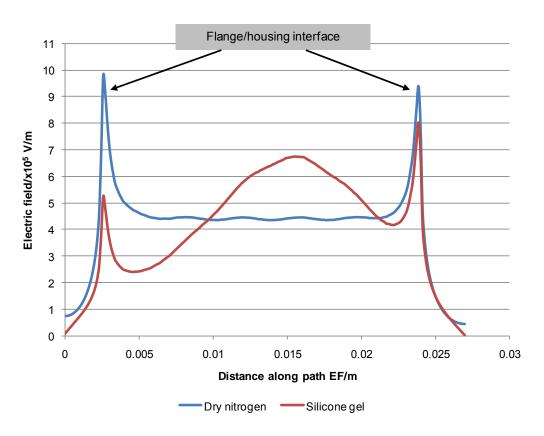

|   |             | 6.4.1 A comparison of silicone gel and dry nitrogen as cavity fillers           | 96       |  |  |

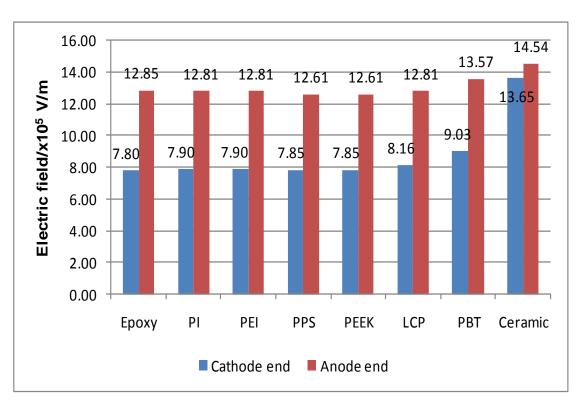

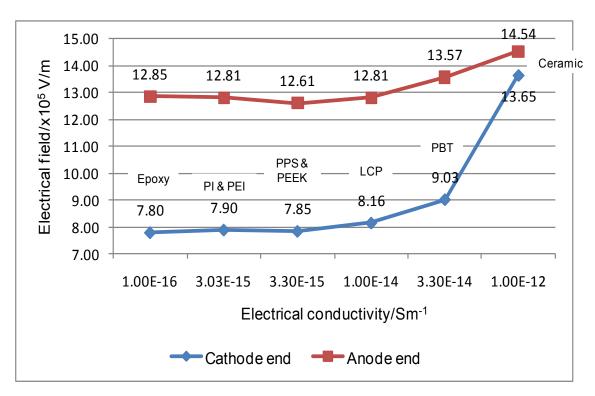

|   |             | 6.4.2 Comparison of Alternate Polymer Housing Materials                         | 99       |  |  |

|   | 6.5         | AC simulations                                                                  | 102      |  |  |

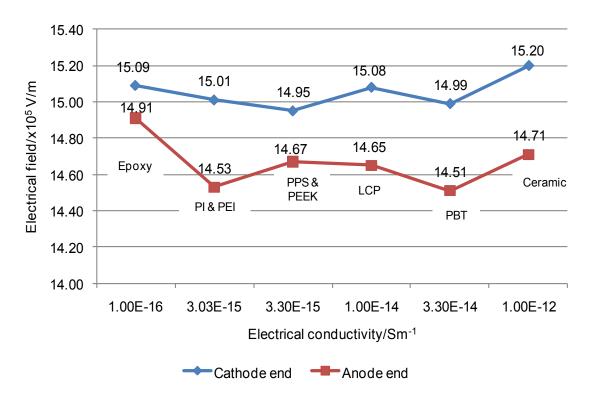

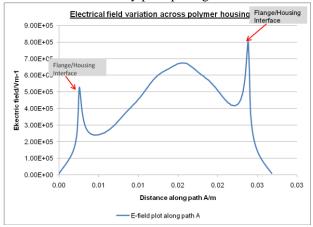

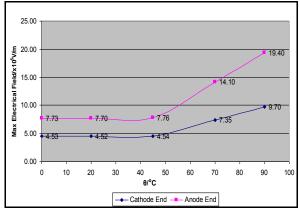

|   |             | 6.5.1 AC simulation results                                                     | 107      |  |  |

|   |             | 6.5.1.1 Influence of AC voltage and its harmonics                               | 107      |  |  |

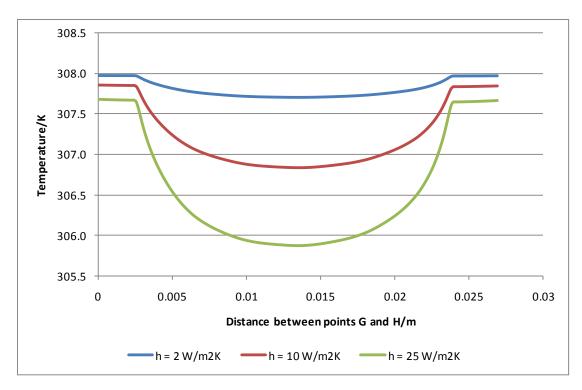

|   |             | 6.5.1.2 Influence of copper pole piece temperature and heat transfer co         |          |  |  |

|   |             | boundary conditions                                                             |          |  |  |

|   |             | Discussion                                                                      |          |  |  |

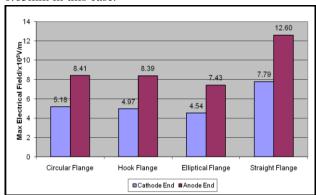

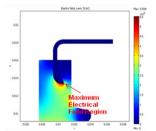

| 7 |             | mm prototype development I: Flange end design                                   |          |  |  |

|   |             | Introduction                                                                    |          |  |  |

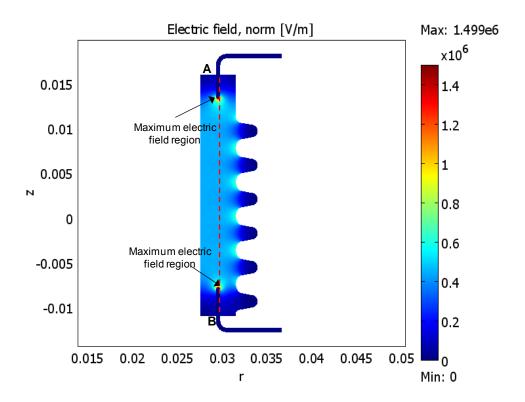

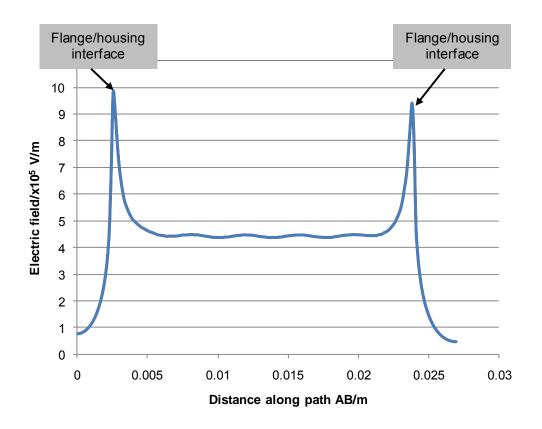

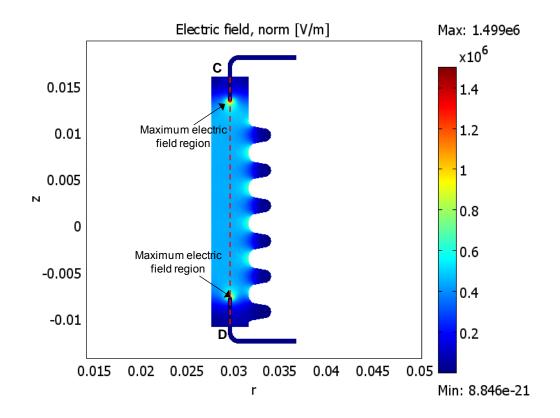

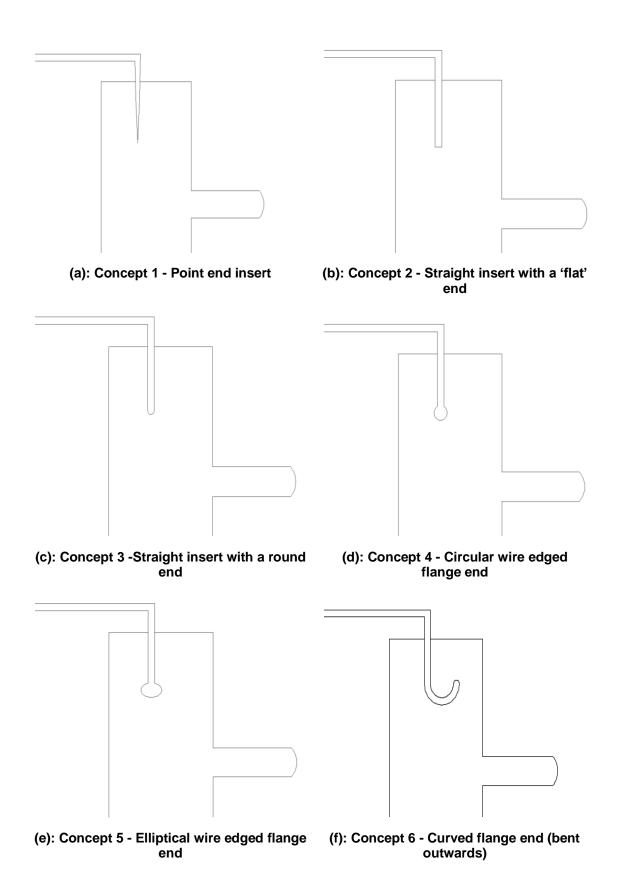

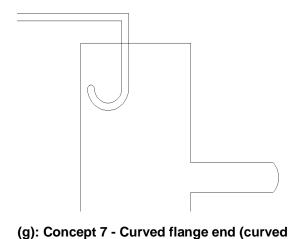

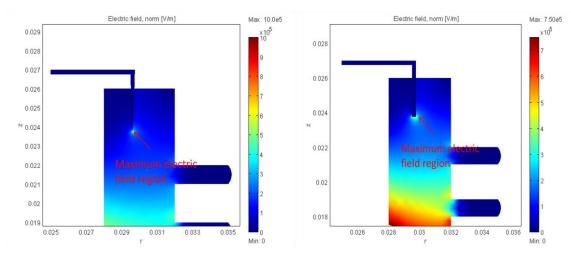

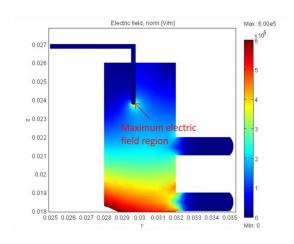

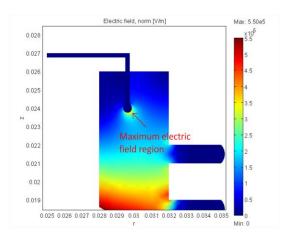

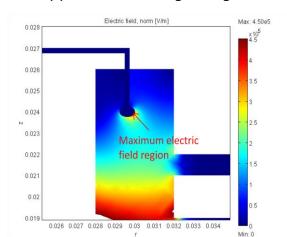

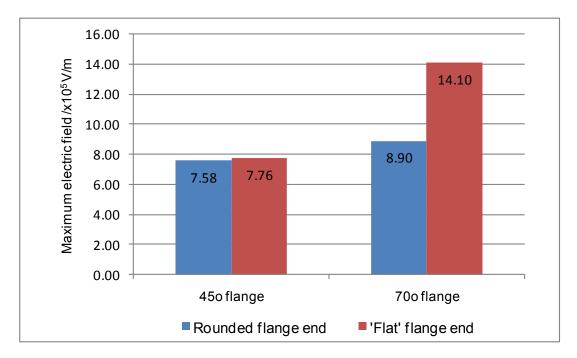

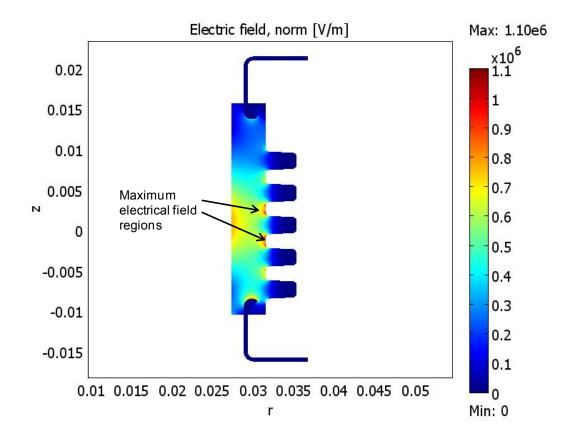

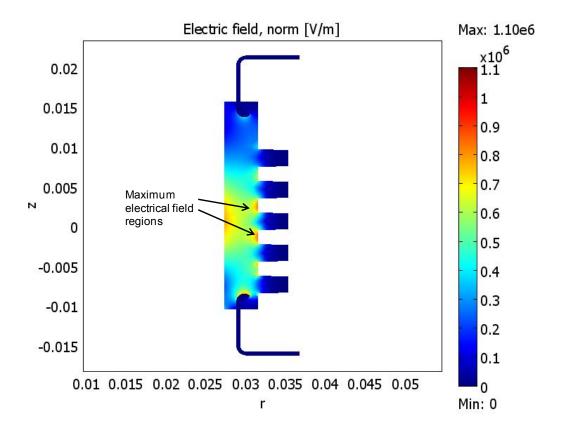

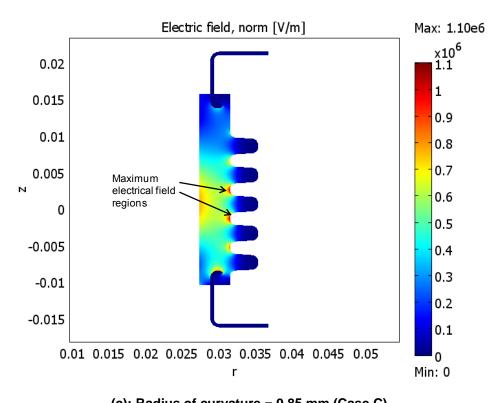

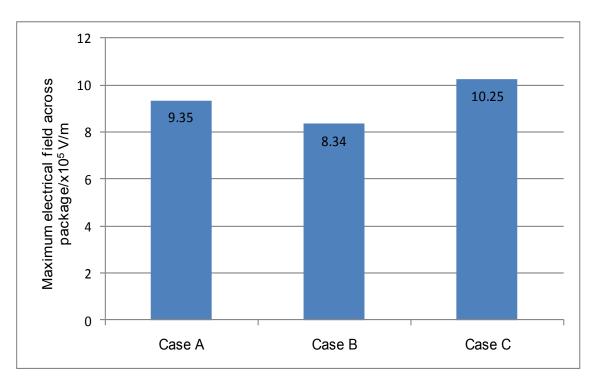

|   |             | 7.2 Electrical field variation around metal insert ends                         |          |  |  |

|   |             | Circular flange                                                                 |          |  |  |

|   |             | Elliptical flange                                                               |          |  |  |

|   |             | Curved flange                                                                   |          |  |  |

|   | 7.6         | Electric field comparison around circular, elliptical and curved flange end geo | ometries |  |  |

|   | 7.7         | Optimisation of the flange end design                                           | 135      |  |  |

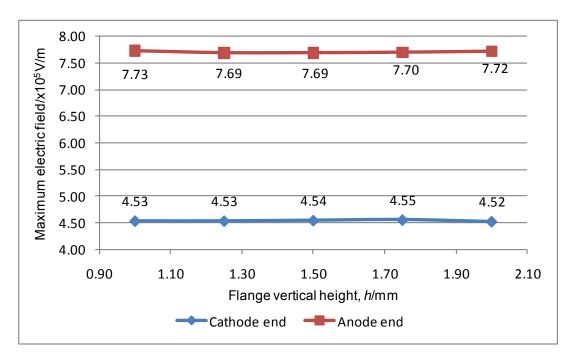

|   |             | 7.7.1 Variation of vertical height, <i>h</i> , of the curved flange             | 136      |  |  |

|   |             | 7.7.2 Contour length variation                                                  | 138      |  |  |

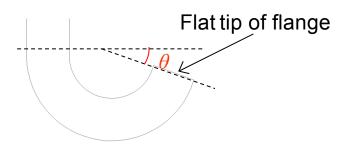

|   |             | 7.7.3 Flange tip design                                                         | 141      |  |  |

|   | 7.8         | Discussion                                                                      | 144      |  |  |

| 8 | <b>50</b> 1 | mm prototype development II: Influence of thyristor housing geometry            | 148      |  |  |

|   |             | Introduction                                                                    |          |  |  |

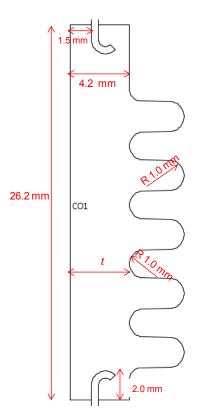

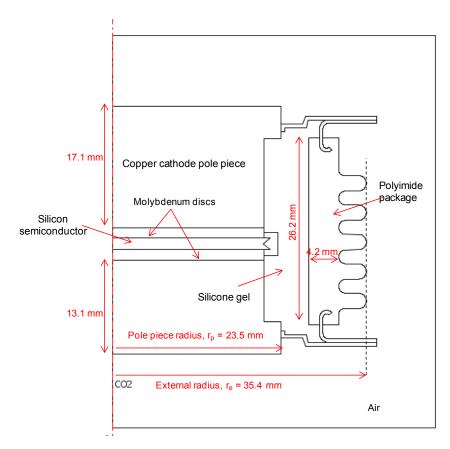

|   | 8.2         | Stage 1: Housing geometry study                                                 |          |  |  |

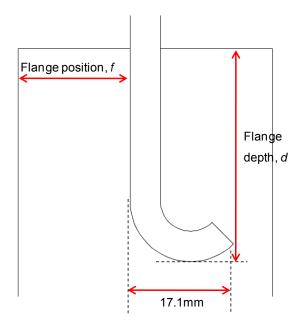

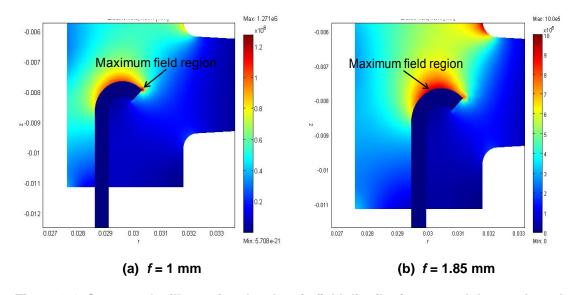

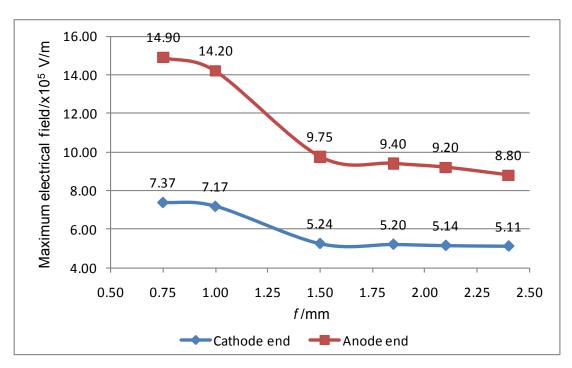

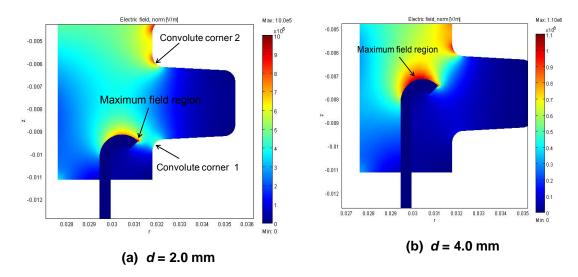

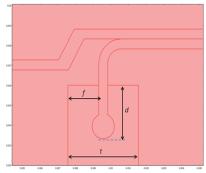

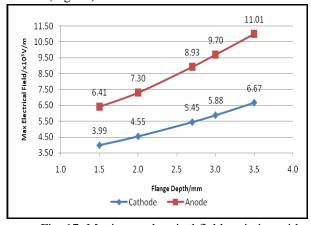

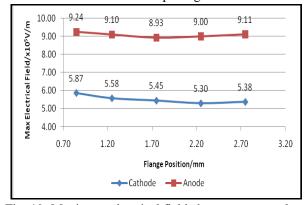

|   |             | 8.2.1 Flange position, <i>f</i> , and insert depth, <i>d</i> , geometries       |          |  |  |

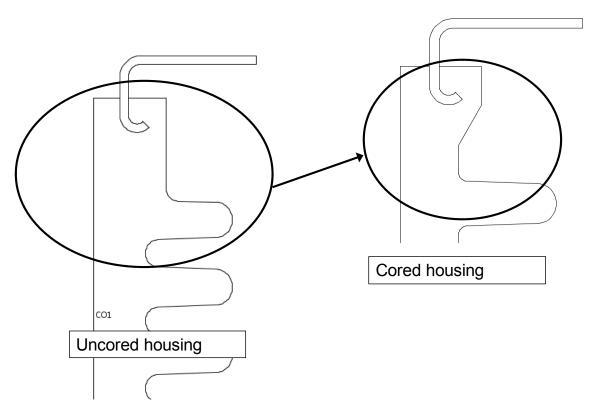

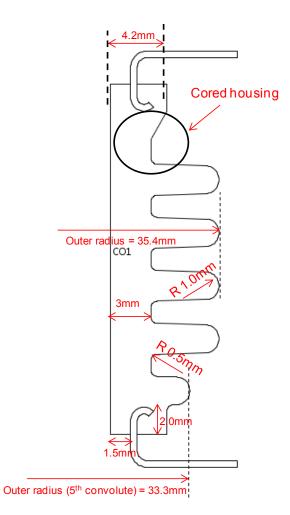

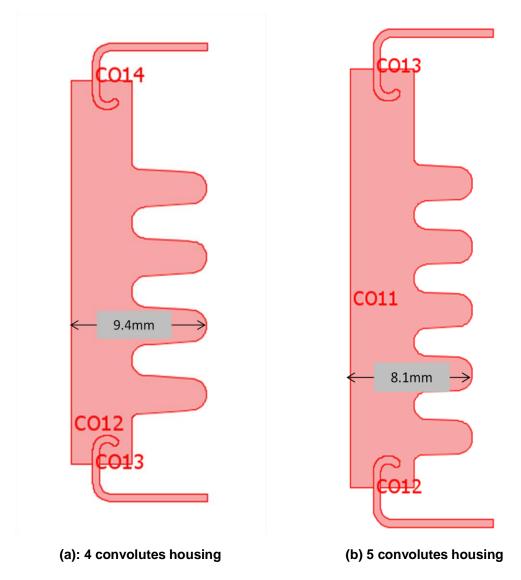

|   |             | 8.2.2 Housing convolute design                                                  |          |  |  |

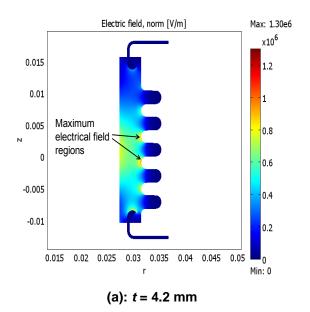

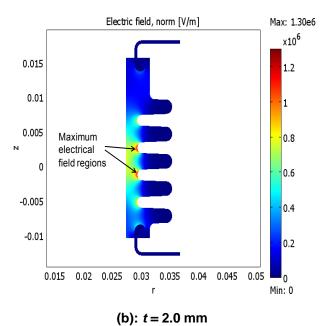

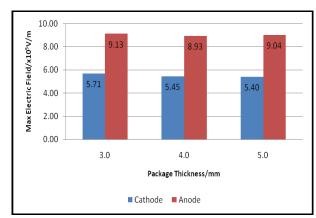

|   | 8.3         | Stage 2: Variation of package thickness                                         | 163      |  |  |

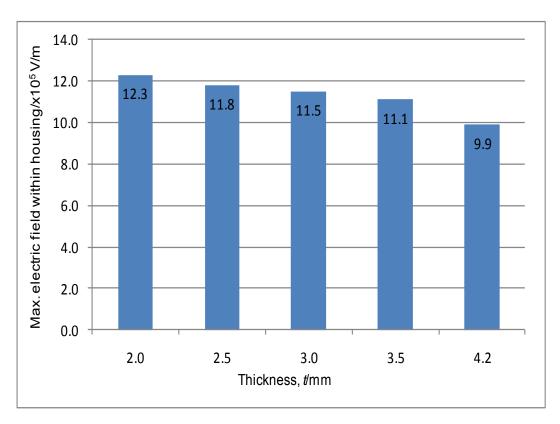

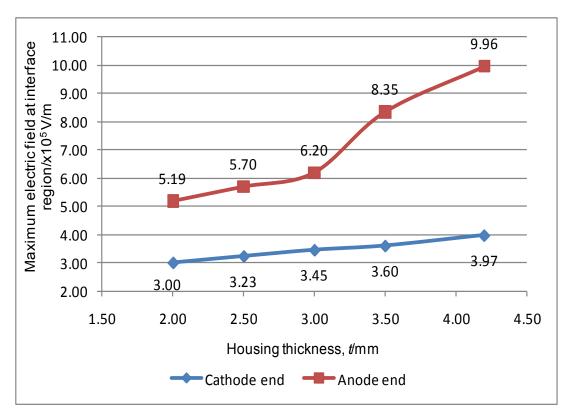

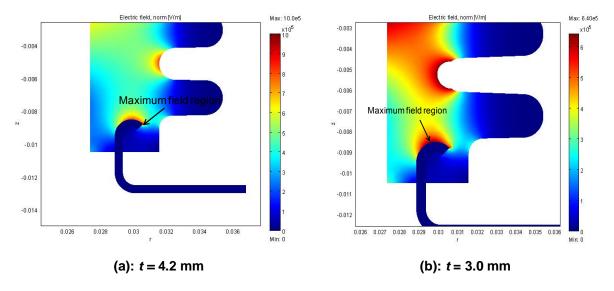

|    |            | 8.3.1   | Electric                       | cal performance studies                                | 165       |  |  |  |  |

|----|------------|---------|--------------------------------|--------------------------------------------------------|-----------|--|--|--|--|

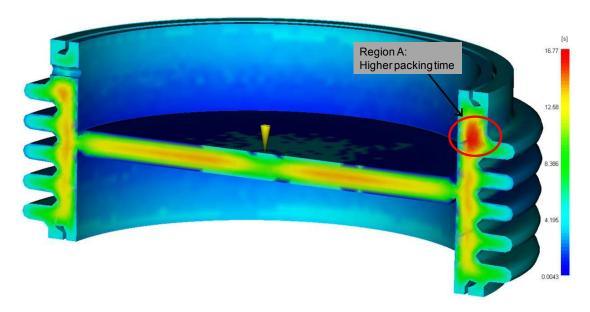

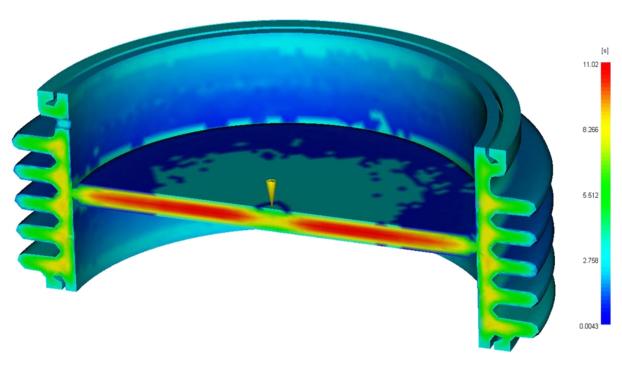

|    |            | 8.3.2   | Injectio                       | n moulding simulation studies                          | 168       |  |  |  |  |

|    | 8.4        | Final   | design                         | of 50 mm prototype housing                             | 171       |  |  |  |  |

|    | 8.5        | Conc    | lusion                         |                                                        | 174       |  |  |  |  |

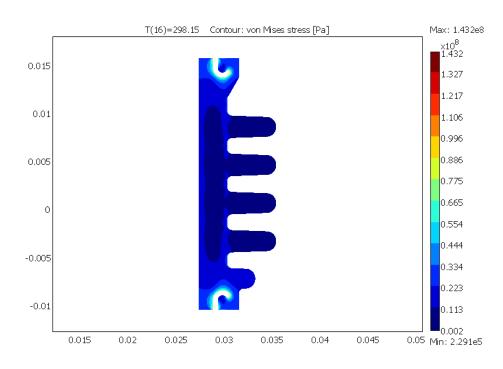

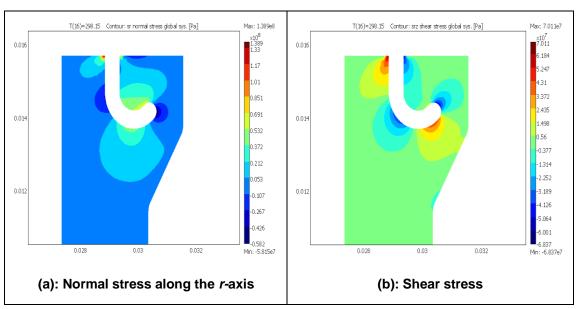

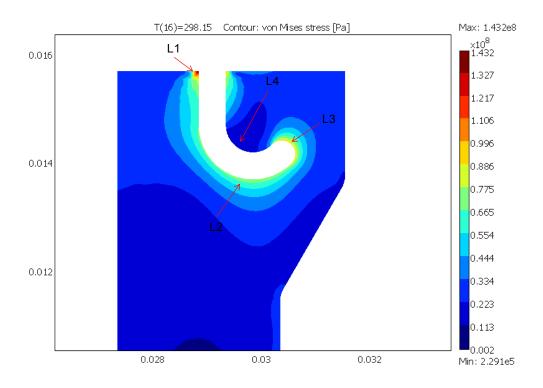

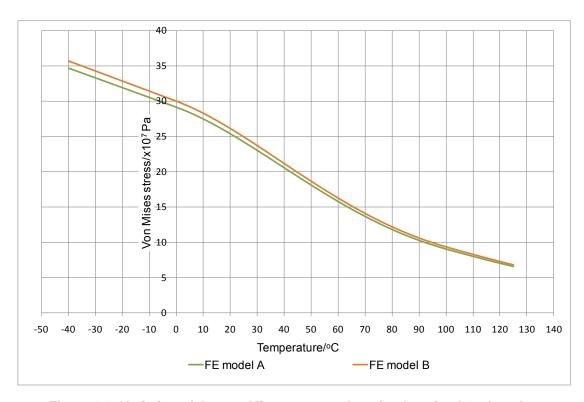

| 9  | The        | ermo-ı  | mechan                         | nical study of the 50mm prototype housing              | 178       |  |  |  |  |

|    | 9.1        | Introd  | duction                        |                                                        | 178       |  |  |  |  |

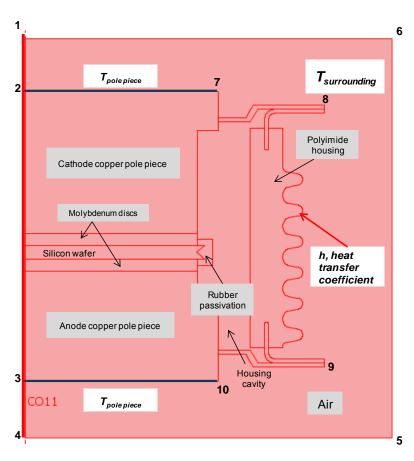

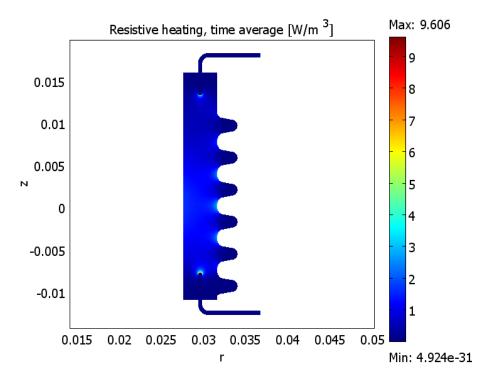

|    | 9.2        | Therr   | no-mec                         | hanical simulation                                     | 180       |  |  |  |  |

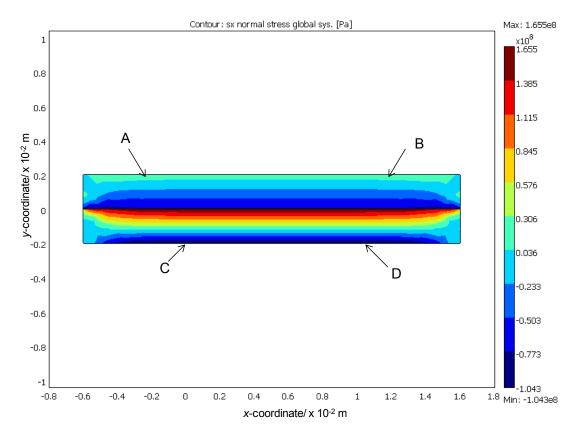

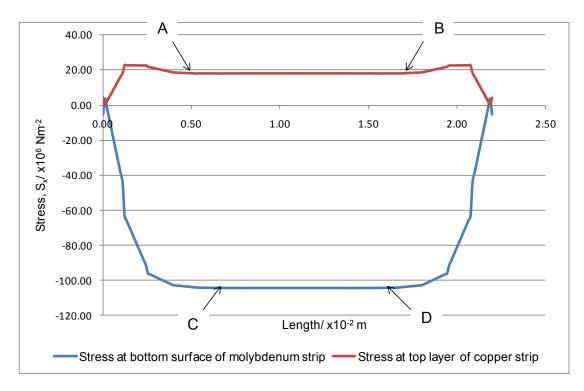

|    |            | 9.2.1   | Simula                         | tion results & discussion                              | 183       |  |  |  |  |

|    | 9.3        | Temp    | Temperature cycling experiment |                                                        |           |  |  |  |  |

|    |            | 9.3.1   | Partial                        | discharge test approach                                | 189       |  |  |  |  |

|    |            | 9.3.2   | Dye pe                         | netrant test procedure                                 | 191       |  |  |  |  |

|    |            | 9.3.3   | Results                        | s & Discussion                                         | 193       |  |  |  |  |

|    | 9.4        | Discu   | ıssion                         |                                                        | 197       |  |  |  |  |

| 1( | 0          | Desig   | gn of a                        | 125 mm thyristor package using the Taguchi Method of E | xperiment |  |  |  |  |

|    | Des        | sign (1 | ΓMED) .                        |                                                        | 201       |  |  |  |  |

|    | 10.        | 1       | Introdu                        | ction                                                  | 201       |  |  |  |  |

|    | 10.2       | 2       | Taguch                         | ni Method of Experimental Design (TMED)                | 202       |  |  |  |  |

|    | 10.3       | 3       | Resear                         | ch methodology                                         | 204       |  |  |  |  |

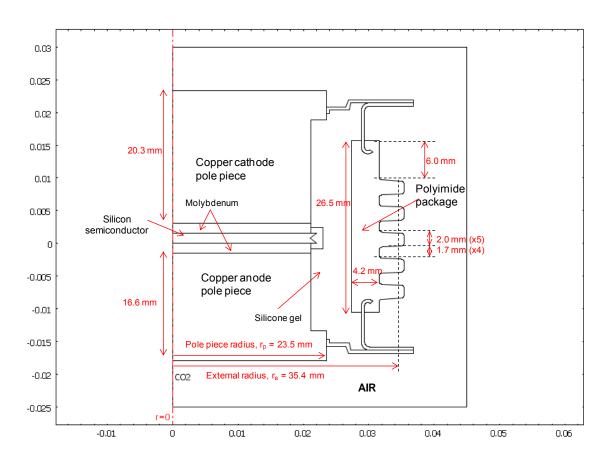

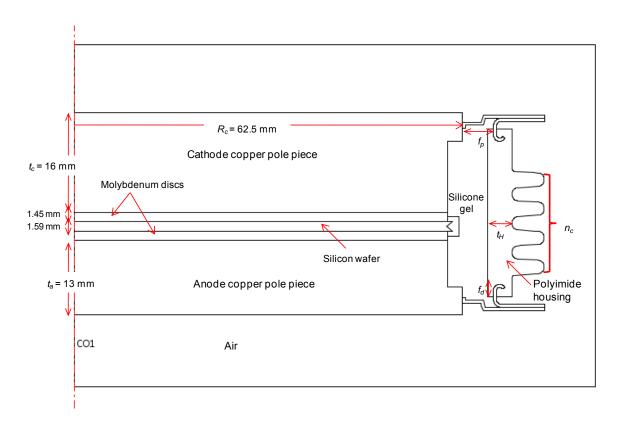

|    |            | 10.3.   | 1                              | FEA Model                                              | 205       |  |  |  |  |

|    | 10.4       | 4       | Design                         | factor interactions – Stage A                          | 207       |  |  |  |  |

|    |            | 10.4.   | 1                              | Methodology                                            | 207       |  |  |  |  |

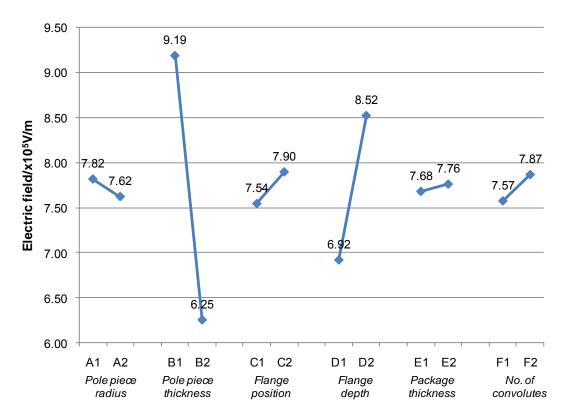

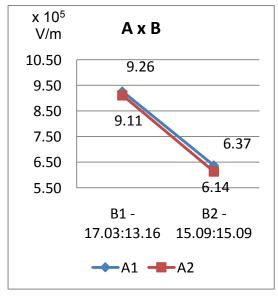

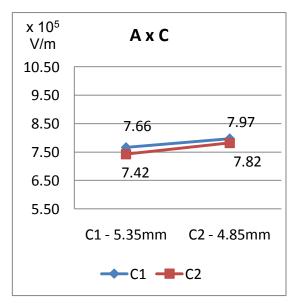

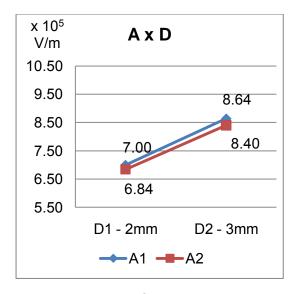

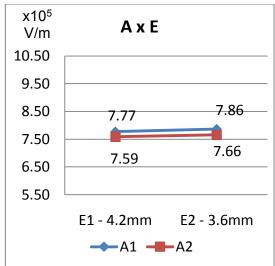

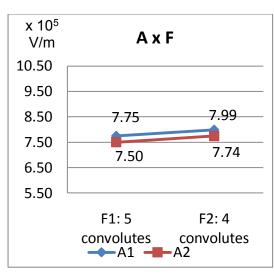

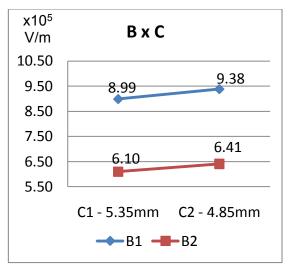

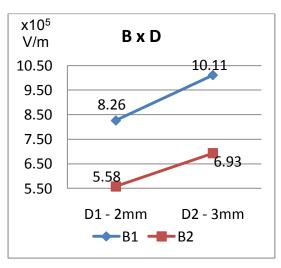

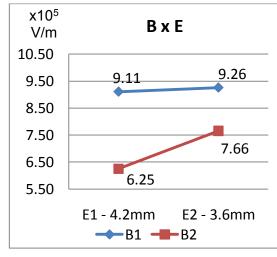

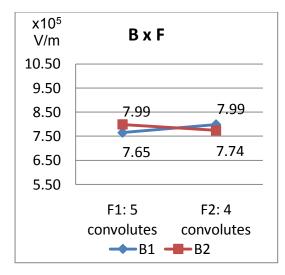

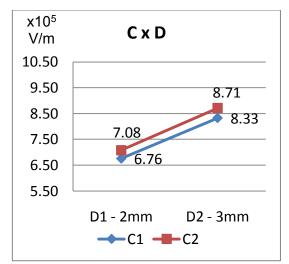

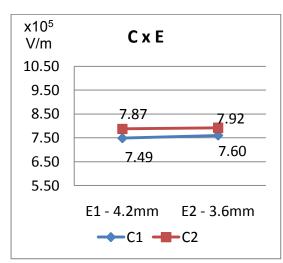

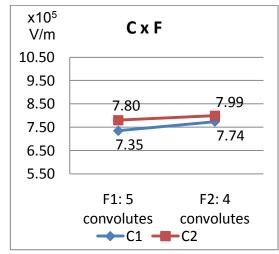

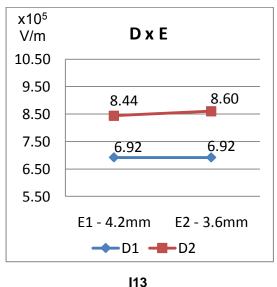

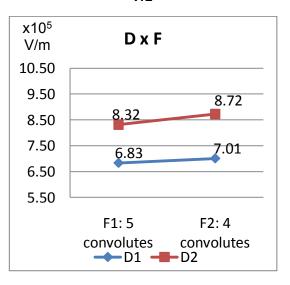

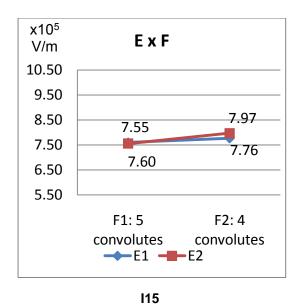

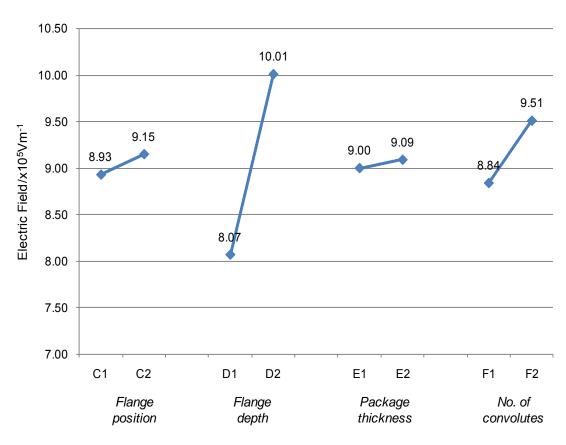

|    |            | 10.4.2  | 2                              | Results & Discussion                                   | 209       |  |  |  |  |

|    | 10.        | 5       | Stage I                        | B - 125 mm housing design                              | 217       |  |  |  |  |

|    |            | 10.5.   | 1                              | Methodology                                            | 217       |  |  |  |  |

|    |            |         | 10.5.1.                        | 1 ANOVA                                                | 219       |  |  |  |  |

|    |            | 10.5.2  | 2                              | Results & Discussions                                  | 222       |  |  |  |  |

|    | 10.6       | 6       | Conclu                         | sion                                                   | 225       |  |  |  |  |

| 1  | 1          | Cond    | lusions                        | s and future work                                      | 227       |  |  |  |  |

|    | 11.        | 1       | Introdu                        | uction                                                 | 227       |  |  |  |  |

|    | 11.2       | 2       | Resea                          | rch summary                                            | 227       |  |  |  |  |

|    |            | 11.2.   | 1                              | Design & Design-for-manufacture recommendations        | 235       |  |  |  |  |

|    | 11.3       | 3       | Future                         | work                                                   | 237       |  |  |  |  |

| R  | efer       | ence.   |                                |                                                        | 241       |  |  |  |  |

| Α  | ppe        | ndix 1  | 1                              |                                                        | 252       |  |  |  |  |

| Δ  | Annendix 2 |         |                                |                                                        |           |  |  |  |  |

#### 1 Introduction

# 1.1 Electricity Generation and Transmission

Since the availability of the first commercial electricity, electrical technology has rapidly expanded to become the backbone of our modern society and is today used in an almost limitless set of applications which include heating, cooking, transport, lighting, IT, etc. Unlike other energy sources, such as oil or gas, electricity cannot be stored easily and economically in sufficient quantities. As a result, it is usually generated and distributed the moment it is needed. Transmitting electricity today requires a rather complex and dynamic infrastructure, whereby the power on the transmission line at any specific time must accommodate changing electricity supply and demand conditions, equipment shutdown and maintenance, weather extremes and fuel shortages among others.

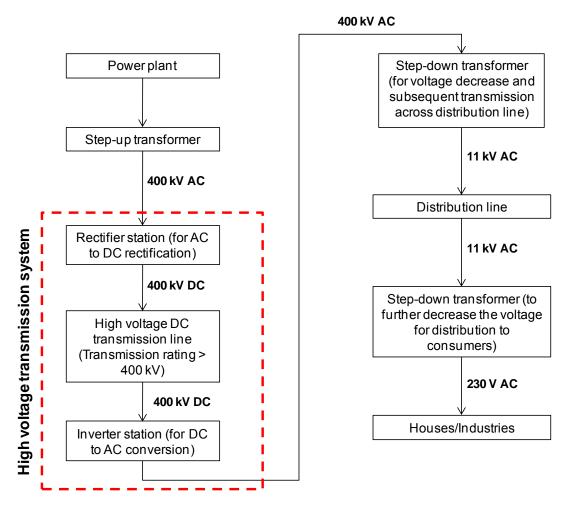

Electricity is generated at power plants from a range of primary sources, e.g. nuclear, coal, hydro, etc. It is then transmitted through transformers and transmission lines, to substations, distribution lines, and finally to the electrical consumer. The distribution along transmission lines can be done in either of two modes - direct current (DC) or alternating current (AC). The choice of these depends on a host of interrelated factors, such as transmission ratings, geographical topography, safety and cost. Although AC transmission tends to be effective for most electrical distribution situations, DC transfer is increasingly adopted for energy transfer between different grids or when transmitting large power ratings over long distances. For example, for a typical 2000 MW transmission, Rudervall et al., 2010 showed that DC transmission becomes more economical than AC when the transmission distance is greater than 800 km. An example of a distribution system containing a high voltage direct current (HVDC) based link is illustrated in Figure 1.1, where AC power generated at a power plant is increased in

voltage using step-up transformers and rectified to direct current at the rectifier station for transport over long distances along either overhead lines on land, or submarine cables across an expanse of sea, to an inverter station where power is needed. Such transmission voltages tend to be around 400 kV. Once at the inverter station, the DC voltage is converted back to AC and decreased in steps to voltages, such as 11 kV for medium to large industries and 230 V for smaller factories and residential areas (Parliamentary Office of Science and Technology, 2001).

Figure 1.1: Outline of a distribution system containing a HVDC transmission link

# 1.2 HVDC Technology: an overview

The origin of experimental work on high voltage transmission can be traced back as early as 1881 to the work of Marcel Deprez who published the first

theoretical examination of HVDC power transmission and successfully transmitted 1.5 kW at 2 kV over a distance of 35 miles (Arrillaga, 1998). Since then, different researchers have continued the work of Deprez to attain higher transmission voltages. Compared to DC transmission, the AC method was initially considered the preferred mode of high voltage transmission because it offered better efficiency and less power loss. However with the expansion of long distance and higher voltage transmission over time, AC transmission became inefficient due to stability related problems, such as oscillation of the reactive power between the capacitances and inductances in the system, and HVDC transmission mode was reconsidered (Arrillaga, Transmitting DC power at high voltages (i.e. greater than 1.5 kV) and long distances only became possible with the use of the mercury-arc valve in the Gotland link in 1954 (Asplund et al., 2003a). However, with the invention of thyristors in 1957, the HVDC transmission area was offered new possibilities. In fact, since its first implementation in the Gotland link in 1967 when they replaced some mercury arc valves, thyristor valves have been implemented in several HVDC schemes (Asplund et al., 2003b). Because of its reliability and low loss properties, HVDC bulk transmission is expected to increasingly rely on thyristor-based technologies.

As shown in Figure 1.1, the HVDC transmission system consists of a rectifier unit at the sending end, and an inverter unit at the receiving end. The two ends are connected by a DC transmission line. The rectifier and inverter stations at both the transmission and receiving ends of the link consist of similar equipment. The main components are the thyristor valves, transformers (to adapt the AC voltage level to/from the required DC voltage level), and AC/DC filters to limit the amount of harmonics to the tolerance level of the network. The transmission medium used for bulk transmission over land is frequently a bipolar overhead line, whilst for submarine transmission of HVDC either solid or oil-filled cables are used (Rudervall et al., 2010).

The conversion of the AC to DC at the transmitting end and DC to AC at the receiving end are normally achieved in three ways, namely natural

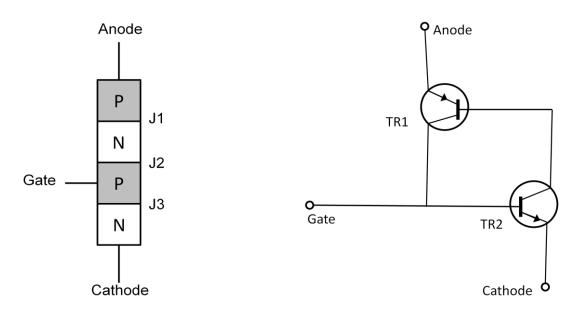

commutated converters, capacitor commutated converters, and forced commutated converters (Rudervall et al., 2010). Compared to the other two technologies, the natural commutated converters are the most widely used system in HVDC transmission and the main component of the converter station is the thyristor, which is a solid-state semiconductor device similar to a diode with an extra control terminal (the gate). It comprises of four layers of alternating N and P-type material, e.g. P-N-P-N or N-P-N-P. The main terminals, the anode and cathode, are separated by the full four layers, and the gate is attached to the P-type material near the cathode as illustrated in Figure 1.2. Its operation can be understood in terms of a pair of tightly coupled bipolar transistors (Figure 1.3), whereby the emitter of an NPN transistor is connected to the cathode and the second PNP transistor connected to the anode. The gate is connected to the base of the NPN transistor.

Figure 1.2: Layer diagram of a thyristor

Figure 1.3: Equivalent circuit of a thyristor

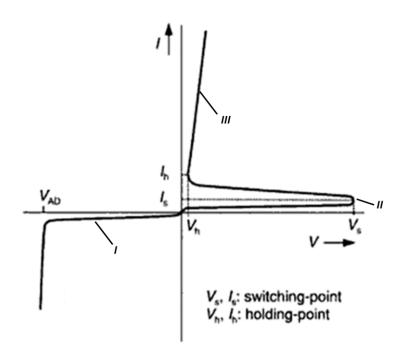

The typical current-voltage characteristic of a thyristor is illustrated in Figure 1.4. From the graph, it can be seen that the device operates in three states, namely (1) reverse blocking mode (*II*), (2) forward blocking mode (*III*), and (3) forward conducting mode (*III*). In the reverse blocking mode, the anode is negatively biased with respect to the cathode, and both PN junction (J1 and J3) are reverse biased. When the polarity is reversed, the thyristor changes to

the forward blocking mode, until a gate signal is applied or the applied voltage exceeds the blocking voltage to trigger the device into the on-state (or forward conducting mode) to behave as a pin diode. The thyristor will remain in a forward conducting mode even if the gate signal is removed (as opposed to a normal bipolar junction transistor). Turn-off of the device can be achieved by reducing the forward current below a threshold value known as the 'holding current'. The forward and blocking capability of the thyristor is determined by the avalanche breakdown of the blocking PN junction and the influence of the current gain,  $\alpha_{pnp}$  and  $\alpha_{npn}$ , of the partial transistors contained in the thyristor (Mitlehner et al., 1988).

Figure 1.4: I-V characteristic of a thyristor (Arrillaga, 1998)

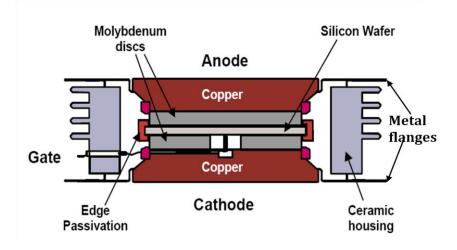

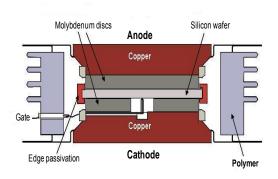

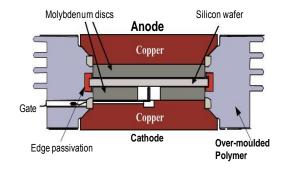

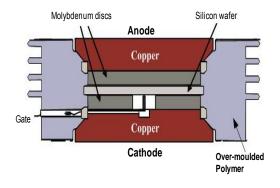

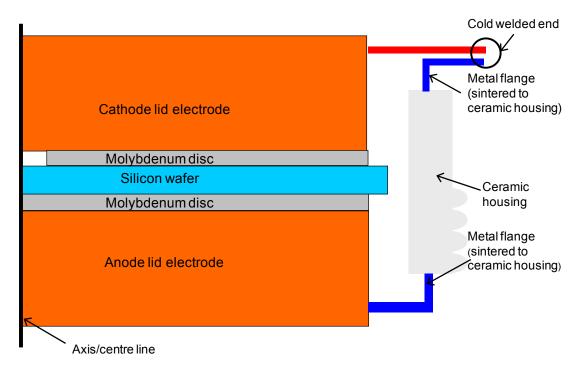

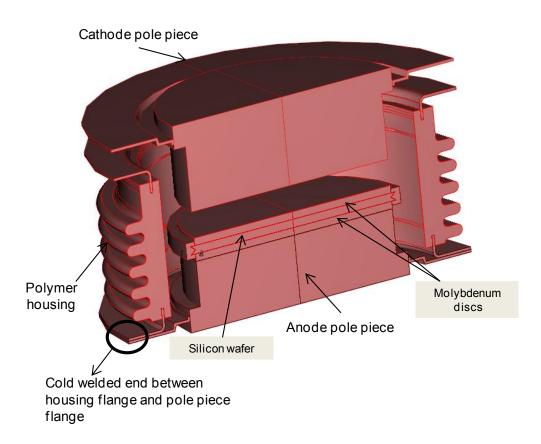

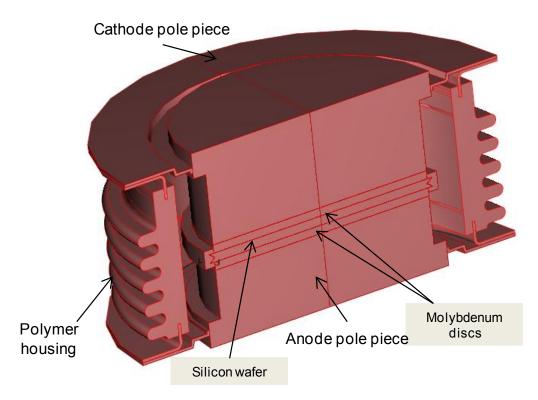

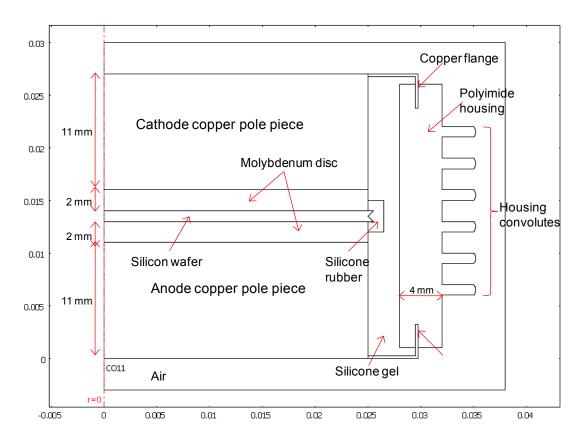

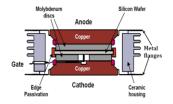

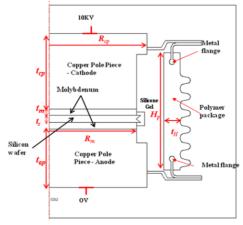

An example of a HVDC thyristor is shown in Figure 1.5. This device is predominantly packaged in a press-pack configuration, and is often referred to as a hockey-puck thyristor. Such a thyristor package comprises of a silicon wafer sandwiched between molybdenum discs and copper electrodes acting as anode and cathode terminals and serving as heat transfer media to cool the device (Figure 1.6). A gate lead is provided to establish connection between the gate electrode of the wafer and an external circuit to trigger the

semiconductor device. The whole assembly is enclosed in a hermetically sealed ceramic housing to prevent environmental attack and provide mechanical robustness.

Figure 1.5: Photo of a 125 mm hockey-puck thyristor, sourced from Woodhouse, 2007b

**Figure 1.6: Cross-sectional view of a hockey-puck thyristor, sourced from** Woodhouse, 2007b

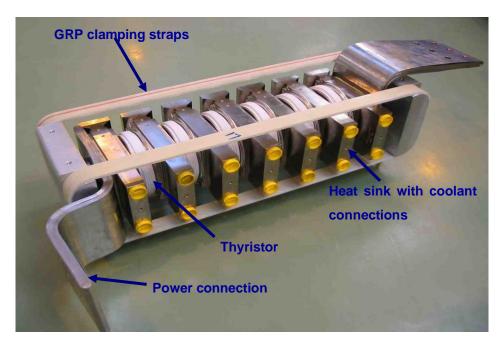

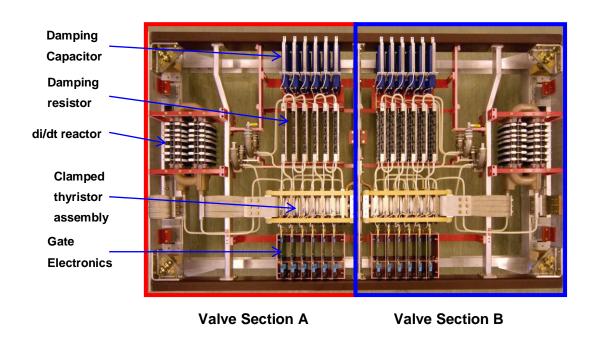

To achieve the desired total blocking voltage, a number of these thyristors must be connected in series. A small group, e.g. 6, are normally stacked to form a clamped thyristor assembly structure (Figure 1.7). The thyristor assembly, which is also comprised of nickel-plated aluminium heat sinks connected to the anode and cathode pole pieces of the thyristors for heat removal, is then connected to various other components to form a thyristor module. Such a module, which is typically around 3.3 m x 2.1 m in dimensions, is made up of two identical valve sections A and B, and is comprised of identical components, namely damping capacitors, damping

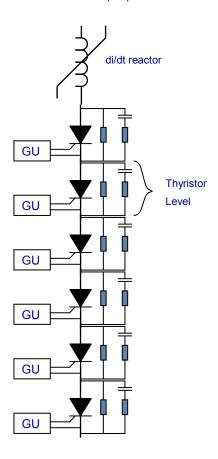

resistors, gate electronics, a *di/dt* reactor and thyristor clamped assembly (Figure 1.8). The schematic diagram of such a valve section is illustrated in Figure 1.9.

Figure 1.7: Photo of a clamped thyristor arrangement (Woodhouse, 2007b)

Figure 1.8: Photo of a thyristor module, sourced from Woodhouse, 2007b

#### Valve Section (VS)

Figure 1.9: Schematic representation of a thyristor valve section, sourced from Woodhouse, 2007b

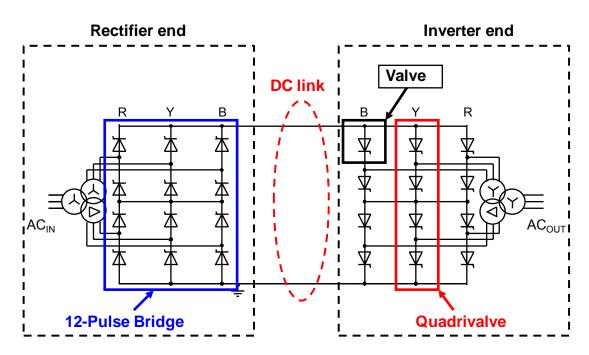

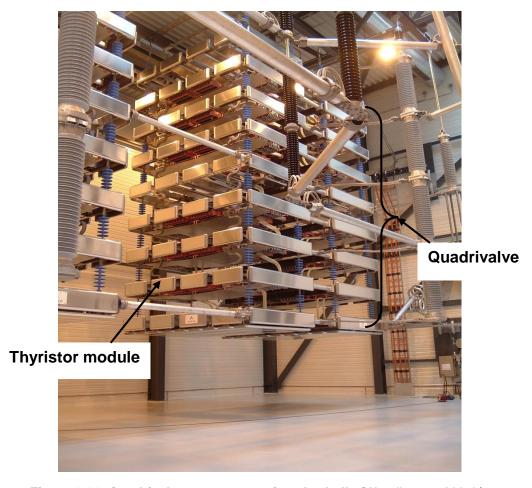

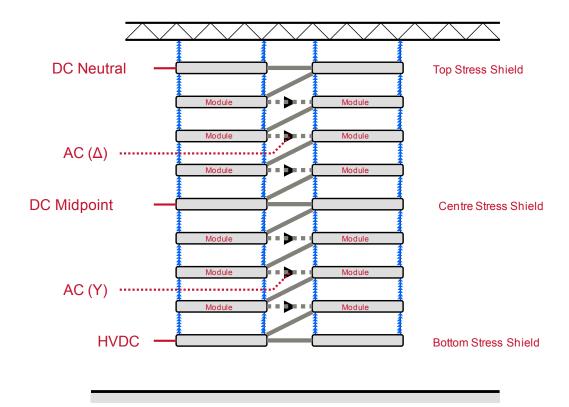

Depending on the transmission rating, a number of thyristor modules are then connected in series to form the thyristor valve. These valves are then grouped to form a 12-pulse converter (Figure 1.10) for each pole at each terminal of the DC line for the HVDC conversion. The thyristor valves used in the 12-pulse converter are normally grouped as quadrivalves mainly to economise on insulation and are located in air conditioned buildings known as valve halls. In the valve halls, the valve modules are arranged as stacked structures suspended from the ceiling of the hall to provide mechanical stability with regards to earthquakes, as shown in Figure 1.11 which illustrates a quadrivalve arrangement, while Figure 1.12 shows a schematic of the physical arrangement of the quadrivalve (Stomberg et al., 2010).

Figure 1.10: Outline of a 12-pulse bridge circuit (Woodhouse, 2007b)

Figure 1.11: Quadrivalve arrangement in valve halls (Woodhouse, 2007b)

Figure 1.12: Schematic drawing showing the physical implementation of a quadrivalve

#### 1.2.1 Future challenges of power semiconductor devices

With the rapid economic development of large and highly populated countries, such as China, India, Brazil, etc., HVDC transmission is expected to play a major role in their expanding energy demands. Certain studies have actually shown these countries will be better served if the transmission voltage and current is increased above present levels of 3000 A at ±500 kV. For example, China is proposing a transmission rating of 4000 A at ±800 kV for its future transmission grids (Lescale et al., 2010).

To meet the future challenges in HVDC transmission, many trade-offs and interactions are required to achieve a practical and economic design rating for the thyristor-based converters. For example, this involves optimising the trade-offs between thyristor parameters, the design of solid state valves in which they are fitted, and the design of the converter system in which the valves will be used. However, one important trade-off parameter concerns the

diameter of the silicon semiconductor of the thyristor. For a fixed diameter of silicon, the voltage and current ratings are inversely related. Thus, to achieve a 4000 A capacity rather than 3000 A, a 125 mm diameter silicon wafer would require lowering the voltage rating from the present level to around 7 kV, leading to more thyristors to be connected in series to achieve the given total blocking voltage therefore increasing the cost and size of the HVDC transmission system. To compensate for this trend, thyristors with larger diameters, e.g. 150 mm diameter, are being sought for implementation in the future (Woodhouse, 2007a).

Another alternative route to improve a thyristor performance lies in improving the silicon technology. However, since silicon technology is today considered mature, and major breakthroughs are not anticipated (Linder, 2010a), the attention of engineers is increasingly aimed at developing maintenance-free valves for future transmission schemes. One area, where technological improvement still remains possible, is the design and performance optimisation of the semiconductor device housing. In fact, what was previously considered to be a mere container is today a major limitation and contributes a significant amount of the development cost of power electronic systems (Linder, 2010b). This thesis focuses on package development area for power thyristors that require a high level of reliability.

# 1.3 NEWTON project overview

The development trend in high voltage semiconductor packages mirrors in many ways the progress in other areas of the electronics industry, e.g. microelectronics, where the focus is to utilise low cost, light weight, environmentally friendly and high performance materials (Goosey, 1999). However, unlike semiconductor devices used in microelectronics, where miniaturisation of components is the pathway (Test, 1988, Tummala R R, 2005), components for high voltage applications are anticipated to be designed to a larger size and with fewer numbers being used (to minimise cost and complexity) for future high voltage schemes.

As illustrated in Figure 1.5, the thyristor housing has traditionally been made of ceramic materials and has demonstrated an excellent history of reliability and performance because of its hermetic and wear resistant nature (Lips, 1998). Nevertheless, the main disadvantages of ceramic housings today are their processing cost and weight. An alternative material class that can potentially overcome these limitations of the current packages is polymers. Unlike ceramics, some advantages polymers provide are relatively low cost, light weight, good formability and recyclability. However, some drawbacks of using polymers are: (1) they are non-hermetic (Vettraino et al., 1999) – leading to flashover or partial discharge failure in high voltage applications, (2) expensive manufacturing routes, (3) and sometimes varying properties over a wide temperature range.

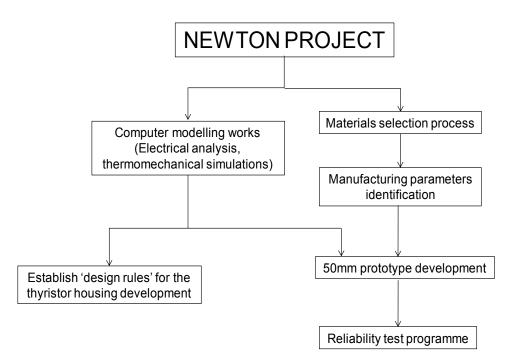

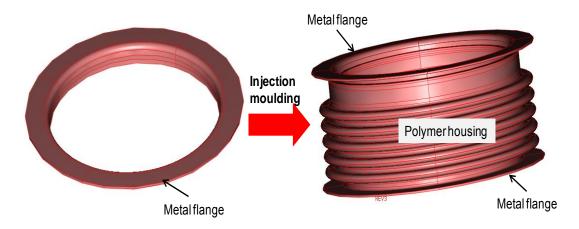

The NEWTON project (New Thyristors for Transmission & Distribution Applications) was a Technology Strategy Board (TSB) funded project (Ref: H0163B) between Dynex Semiconductors Ltd, Areva T&D UK Ltd and Loughborough University, and aimed at developing a new low cost packaging for fully bonded large area silicon wafers that were under development in a parallel TSB funded programme. The research activities of this project focussed on a 'replacement' hockey-puck type thyristor package, where the ceramic housing was substituted with a polymer material. Although attempts to develop polymer-based thyristor housings had been made previously, the thyristor device being developed here was aimed primarily for use in UHVDC applications (typically for ±800 kV requirements) in technologically developing countries, such as China, India, Southern Africa, and South America. This research programme would eventually lead to the development of a new state of the art 150 mm high voltage thyristor device for use in HVDC solutions (Woodhouse, 2007a).

For this project, Loughborough University (LU) was responsible for the material selection of the housing, manufacturing process identification, housing design, and reliability studies for the new polymer-based package.

The different technical activities involved in the project are depicted in Figure 1.13.

Figure 1.13: Overview of LU technical activities in NEWTON project

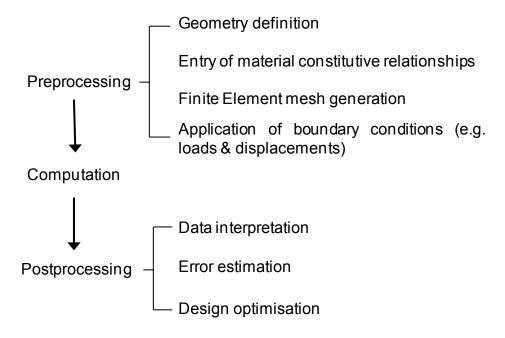

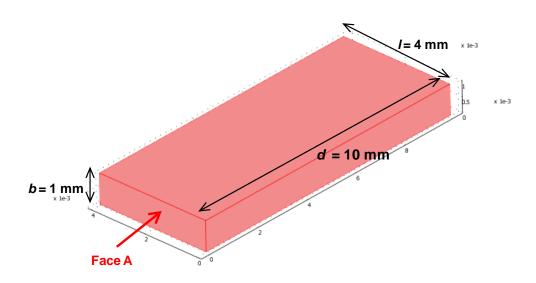

The PhD research project that is reported in this thesis, formed part of these Loughborough University activities and focussed on the study of the polymeric package behaviour and improving its design. The research activities were divided into two main groups, namely (1) computer modelling, and (2) reliability studies. In the computer modelling studies, because the housing would experience electrical stresses and temperature excursions during service, electrical and thermo-mechanical simulations were performed. Together with improving the package design and performance, the studies also aimed to establish design guidelines for future thyristor housing development. On the other hand, to identify whether the polymer material is appropriate for the thyristor housing from both performance and commercial aspects, reliability studies were performed. These tests were carried out on a 50 mm prototype developed in the NEWTON project and aimed at revealing different failure mechanisms that would potentially cause the package to fail. The research findings can be expected to assist in the development of polymeric housings of higher reliability in the future.

To address the different objectives of this research project, this thesis has been structured into four parts, namely (1) project background and research methodology, (2) the prototype development, (3) housing development and reliability investigations, and (4) research conclusions. The project background and research methodology are discussed in Chapters 2 to 5. Chapter 2 describes different thyristor housing designs, while Chapter 3 discusses the different failure modes of thyristor housings. Chapters 4 and 5 respectively overview the general research approach, and the main research methodology (i.e. finite element analysis) used to study the package performance in this project.

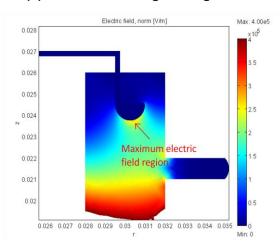

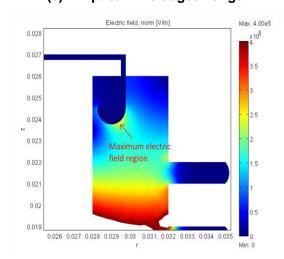

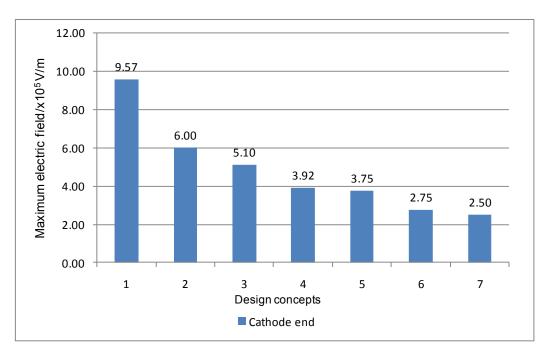

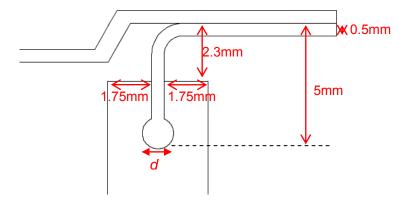

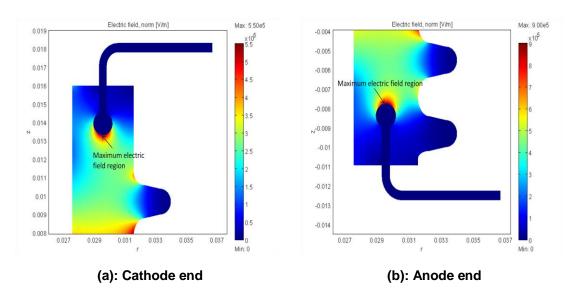

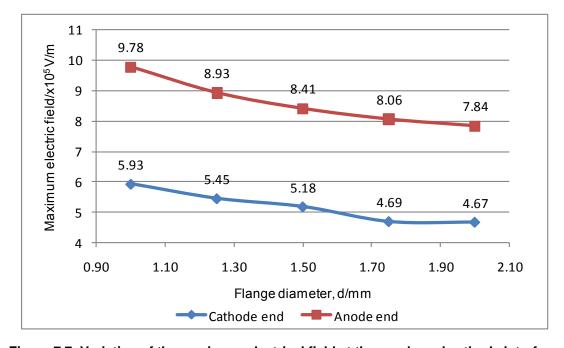

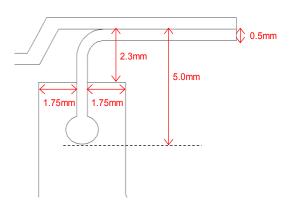

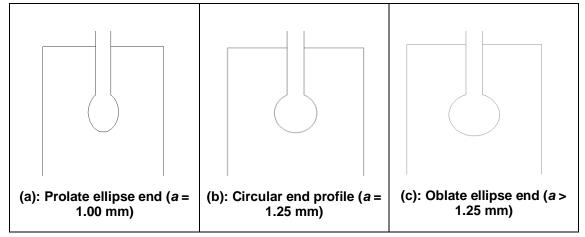

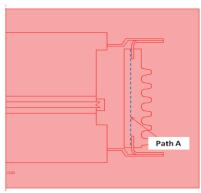

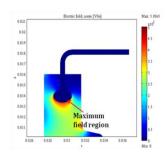

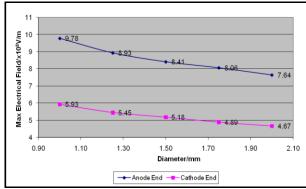

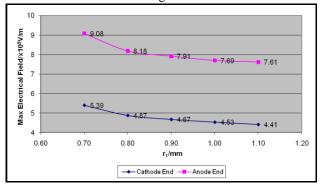

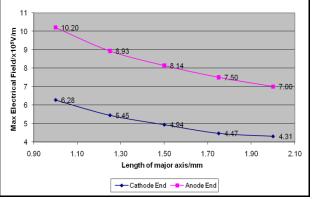

The 50 mm prototype development using a series of computer modelling studies is discussed in Chapters 6 to 8. In Chapter 6, the computer modelling studies investigating the electrical behaviour of the 50 mm polymer prototype housing are discussed, while simulation studies aimed at improving the prototype design are reported in Chapters 7 and 8. Because localised electrical stresses were observed to occur in the polymer housing, an electrical modelling study aimed at reducing the electric field magnitude in the regions of concerns is overviewed in Chapter 7. Chapter 8 describes the influence of different housing parameters, such as the flange depth, housing thickness, etc., on the electrical performance of the housing. These results have then been compared with moulding simulation results, before establishing the final design of the prototype. The third part of the thesis describing the reliability investigation on the 50 mm prototype and the development of a larger diameter housing development are respectively highlighted in Chapters 9 and 10. Chapter 9 discusses another simulationbased study to investigate the thermo-mechanical behaviour of the polymer housing, and the reliability of the manufactured 50 mm prototype when it is exposed to different temperature loading conditions. On the other hand, Chapter 10 describes the influence of different geometrical parameters on the electric field magnitude in the housing and discusses the design of a 125 mm housing using the results from early case studies and the Taguchi Method of Experimental Design. The research conclusions and scope of further work are then finally outlined in Chapter 11.

# 2 Review of thyristor housing designs

#### 2.1 Introduction

Electronic packaging refers to the integration of semiconductor devices into a robust electronics system that can withstand environmental conditions and perform reliably over a certain period of time (Barlow III, 1999). Compared to traditional mechanical packaging, electronic packaging aims to provide the electronic circuit with power and signal interconnections, a heat dissipation pathway and a protected environment to prevent contamination, mechanical damage and electronic interference. Typical electronic systems are comprised of several levels of packaging, namely (1) the device and carrier, (2) motherboard or printed circuit board, and (3) enclosure, and each packaging level has distinctive types of interconnection devices associated with it. Packaging of electronic systems has evolved to become today a major crossdisciplinary field in engineering. In fact, with packages today moving from bulky expensive materials, such as ceramics and metals, to predominantly plastics and with increasing environmental regulations (Nei et al., 2007), electronic packaging is expected to play a dominant role in the design of electronic systems.

Since their introduction to replace the mercury-arc valves used in HVDC transmission schemes during the late 1960s, high voltage thyristors have also evolved to accommodate higher performance and demanding operating requirements. The thyristors used in high power converter stations are today required to have a very low failure rate. Since the failure rate cannot be zero in practice, a series of redundant devices are normally provided so that a small number of thyristor are allowed to fail without having to immediately shut down the converter station to undertake repair. Any failed devices are then replaced during planned maintenance periods (typically 2 years for HVDC) (Woodhouse, 2007a). In such situations, it is therefore important that the

thyristors have a high level of reliability for long periods of time, and be protected from different failure causes.

Thyristors are available in various package design configurations depending on their power levels. Low power thyristors, as depicted in Figure 2.1 (a), are commonly available as small plastic packages consisting of a silicon chip; medium power thyristors (Figure 2.1 (b)), that comprise of a silicon wafer, are available as stud-mount configurations. For high power applications, e.g. high voltage transmission, press-pack (or hockey-puck) thyristors (Figure 2.1 (c)) are used, because they allow efficient cooling and appropriate stacking for series connection (Rashid, 2007). As shown in Figure 1.6 in Chapter 1, the basic building block of such high voltage thyristors is the silicon wafer. Such wafers (Figure 2.1 (d)) are normally manufactured from highly pure monocrystalline silicon and have an aluminium metal pattern deposited on them. Because the integrity of the silicon wafer (along with its other components) is critical for the long term reliability of a power thyristor, the housing also needs to be reliable to act as an effective barrier to protect the basic unit from ingress of harmful environmental contaminants, and also have appropriate mechanical properties to prevent it from damage due to clamping loads when the thyristors are clamped.

(a) Low power thyristor

(b) Stud-base thyristor configuration

(d) Photo of a silicon wafer

Figure 2.1: Typical thyristor packages types

An extensive review of the literature was conducted during the initial stages of the NEWTON project to review different thyristor package designs developed in the past. This aimed to assist the development of initial conceptual designs (discussed in Chapters 6 to 8) and also identify potential intellectual property rights issues that may be relevant to the NEWTON developed device. From the literature review, various studies performed in the past, e.g. Tadros et al., 1989, Welleman et al., 2003, N. Monsur et al., 2006, were observed to focus on improving the electrical and thermal performance of high voltage thyristors. Various patents for different thyristor housing designs were also found to have been awarded over the years, as improved performance became necessary. A summary of the patents describing thyristor package designs can be referred to in Appendix 1.

This chapter aims to provide an overview of some of these patents, and identify the design features that improve their performance and reduce failures. Section 2.2 presents examples of some common hockey puck thyristor housing configurations, while key design elements included in the thyristor to improve its design and reduce potential failure causes, e.g. moisture ingress inside the device, are highlighted in section 2.3. Finally,

examples of some patented designs aimed at mitigating common failures due to short-circuit and explosion are reviewed in section 2.4.

## 2.2 Thyristor packages

Although a review of different patents has shown the existence of certain non-hermetic thyristor where the main package body is comprised of polymeric materials (e.g. epoxy), the hermetic press-pack configuration made of ceramic has been the dominant technology over the years. A hermetic housing configuration in its simplest definition means being sealed so that a package is gas tight, and prevents intrusion of contaminants, such as liquid, solid or gas, for an indefinite period of time (Madduri et al., 2008). Such packages have traditionally been used in military, aerospace and some commercial applications, and have demonstrated higher performance and long-term reliability, compared to non-hermetic packages which are vulnerable to moisture for example (Ardebili et al., 2009). Traditional materials used to build hermetic housings have included ceramic, metal and glass because of their non-porous characteristics and their consistent properties across a range of temperatures. Examples of some patented hermetic and non-hermetic (polymeric) housings are discussed in sections 2.2.1 and 2.2.2 respectively.

### 2.2.1 Hermetic housing designs

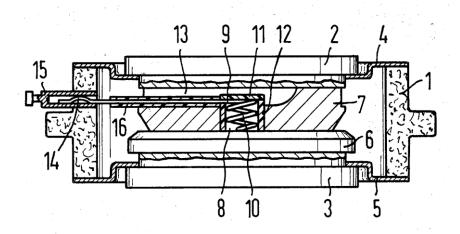

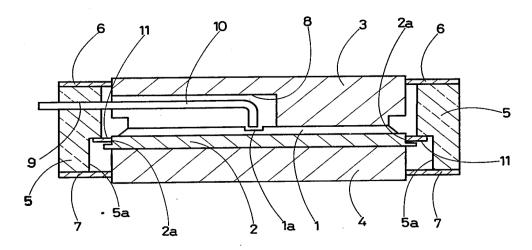

Figure 2.2 shows an example of a one-part hermetically sealed thyristor housing developed by Bahlinger et al., 1975, while another variant of a hermetic thyristor, a two-part housing described by Clelford, 1970, is illustrated in Figure 2.3. The thyristor assembly shown in Figure 2.2 comprises of two metal cover plates (2, 3), sandwiching the thyristor, and enclosed in an alumina housing (1) to prevent ingress of any harmful contaminants. The metal plates engage respectively the cathode and anode of the thyristor by close pressure contact, while connection to the gate electrode of the thyristor is established by a gate control lead (9) of beryllium bronze.

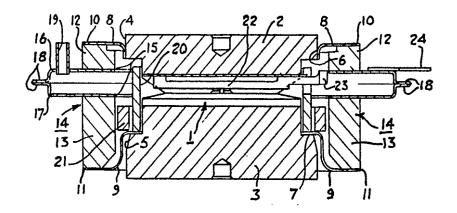

On the other hand, for the two-part housing (Figure 2.3), projecting flanges (16, 17) are welded together on the outside to join together the two separate segments of the housing, while the inner edges of the flanges are sealed to join the housing. In this design, the thyristor element (1) is sandwiched between pairs of copper pole pieces secured to the inner periphery of an annular flange (8, 9), and its outer periphery is secured to a corresponding part of an annular ceramic housing (14).

Commercial HVDC thyristors (Figure 1.6) available nowadays actually also share different features common to the one-part and two-part housings described above. For example, as in the one-part and two-part devices, current thyristor devices are also based on ceramic material. They also consist of anode and cathode copper pole pieces for electrical connectivity and heat removal purposes. The different components in the device, namely the copper pole pieces, the molybdenum discs, and the silicon wafer arranged in a stacked structure, also engage each other by close pressure contact. As in the case of the two-part housing, the thyristor device is also assembled by welding together metal flanges that are part of the housing and copper pole pieces.

Figure 2.2: One-part hermetic housing (Bahlinger et al., 1975)

1 – Aluminium oxide housing wall; 2, 3 - metal cover plates (cathode and anode respectively); 4, 5 are metal plate of kovar material (iron, cobalt and nickel alloy); 6 - wafer; 7 - metal plate; 8 – recess; 9 - metal conductor; 10 – spring; 11 - insulating plate; 12 - insulating ring; 13 - slot; 14 - end of control line; 15 - socket

Figure 2.3: Two-part hermetic housing (Clelford, 1970)

1 - wafer; 2, 3 - copper heat sinks; 4, 5 - the heat sinks circumferential periphery; 8, 9 - annular flange; 14 - housing; 12, 13 - two parts of the housing 14; 16, 17 - dished shaped flange; 19 - conduit from flange 16; 20 - ring, made of an electrically insulating material; 21 - ring made of desiccant material to maintain a dry interior; 22 - gate contact; 24 - external electrical connector; 23 - electrical tab to provide connection between contact 22 and external connector 24

#### 2.2.2 Polymeric housing designs

Together with the hermetic package configuration, the patent review revealed that development of polymer-based high power thyristor housings have also been attempted in the past. For instance, devices developed by Brandt et al., 1980, Gerstenkoper et al., 1980, Merlin et al., 2003, Rohsler, 1982, and Podlesak et al., 1996 used polymers, such as epoxy resins and polyimide, for their housing.

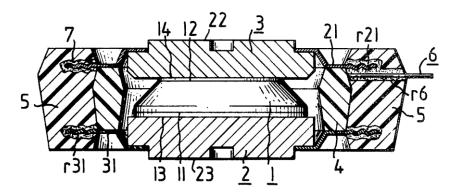

One example of such a polymer housing for a press-pack thyristor, developed by Brandt et al., 1980, is shown in Figure 2.4. The device depicted here consists of a semiconductor wafer (1) sandwiched between a pair of solid-copper metal bodies (2, 3), mounted on its respective ends (11, 12). An insulating ring (4) made of either mineral or glass fibre reinforced epoxy resin is also provided to centre the metal bodies and semiconductor wafer. Annular copper sheets (21, 31) are hard-soldered to the periphery of the metal pieces. They protrude radially above the insulating ring and are provided with

corrugated edges embedded in the plastic jacket - manufactured by an injection pressing process and made of a thermosetting resin, e.g. epoxy. Although polymers are permeable to moisture, non-hermetic housings can also function reliably as hermetic ceramic packages through the inclusion of certain design features. For instance, for the polymer package developed by Brandt et al., 1980 (Figure 2.4), the moisture resistance property of the device is improved through the use of corrugated edges of the annular copper sheets that are embedded in the plastic jacket of the device. Examples of some other design configurations, that improve the reliability polymer housings and can thereby be extended to the polymer housing developed in the NEWTON project in the future, are described in section 2.3.

Figure 2.4: Example of a non-hermetic polymer housing (Brandt et al., 1980)

where 1 denotes the thyristor wafer (semiconductor); 2, 3 are metal bodies; 4 - insulating ring, made of mineral or glass fiber reinforced epoxy resin; 5 - plastic jacket of epoxy resins; 6 - tube through which control lead is passed; R6 - powder coating; 7 - powder coating of either epoxy resins, polyester resins, or polyurethane resins; 11, 12 - major surfaces of semiconductor element; 13, 14 - main electrodes; 21, 31 - annular metal strips; r21, r31 - corrugated edge regions

# 2.3 Key design features of thyristors

As highlighted in Chapter 1 and in section 2.1 of this chapter, thyristors require a high level of reliability throughout long service period. As a result, the integrity of different components, such as the semiconductor element, molybdenum discs, the housing, and also an appropriate connection of the

gate lead to the gate electrode of the semiconductor element, is required to ensure the proper functioning and performance of the thyristor device. From the patent literature review, thyristor devices were seen to contain gate leads of different designs. Examples of some common gate lead configurations include the spring-type gate terminal and the wire bond-type gate lead, as shown in Figures 2.2 and 2.5 respectively.

Figure 2.5: Thyristor device having a wire bond connection gate lead (Merlin et al., 2003) where 10 - semiconductor package; 12, 28 - copper pole piece; 14 - Control lead; 16 - Connection terminal; 20 - semiconductor die; 22 - first major electrode; 24 - control electrode; 26 - second major electrode; 30 - insulating ring, made of insulating plastic; 32, 34 - annular flange; 36 - rib; 18 - connector; 40 - bond wire

For the thyristor to function properly, the gate lead and gate electrode of the semiconductor element are required to be in good contact by processes such as welding and pressure contact, and also properly aligned. Different design concepts have actually been proposed in the past to improve the alignment of the gate lead and the gate electrode of the silicon wafer in a thyristor. For example, in the case of a light-triggered thyristor (LTT) (which is also widely used in HVDC power systems and is triggered by high power laser impulse), the alignment of the light guide and the photosensitive portion of the element are essential. An example of such a LTT device whereby the alignment of the photosensitive portion of the LTT element and light guide is optimised is illustrated in Figure 2.6. In this device, an inner positioning ring (11) is attached to the inner wall of the housing (5a) and fixed on a reinforced metal disc (2) on which the LTT is mounted. The inner diameter of the disc is made

slightly larger than the outer diameter of the reinforced metal disc and the inner wall of the housing is machined to accommodate them.

Such a feature can actually also be included in the NEWTON thyristor to improve the alignment of the gate lead and gate electrode of the silicon wafer in the future. In such a device, an inner positioning ring similar to the LTT thyristor component (11) attached to the inner wall of the polymer housing can be used to improve the alignment between the gate electrode of the silicon wafer and the gate lead that is inserted inside a hollow gate tube (similar to the light guide (10)). The inner positioning ring is then fixed to the molybdenum disc of the NEWTON thyristor in a similar configuration as the position ring (11) is joined to the reinforced metal disc (2) in the LTT device. The inner edge of the polymer housing would also require machining to accommodate the positioning ring and molybdenum disc assembly for the improved gate lead and gate electrode alignment. Together with this, because the LTT device consists of a light guide (10) passing through the ceramic housing (5) similar to the gate lead that would pass in the polymer housing of the NEWTON thyristor, potential scopes also exist in the future to develop a novel LTT device that would also comprise of a housing made of polymeric material (instead of ceramic).

Figure 2.6: Example of a LTT device where light guide and photosensitive element alignment is improved (Kiyohara, 1983)

where 1 - light-triggered thyristor element; 1a - photosensitive part of the element; 2 - reinforced metal disc; 3, 4 - electrode members; 5 - insulated

housing of alumina ceramics; 6, 7 - annular flange; 8 - lateral grove to accommodate the light guide terminal 10; 9 - radial hole in insulated housing; 10 - light guide; 11 - positioning ring

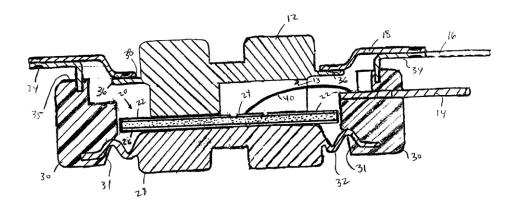

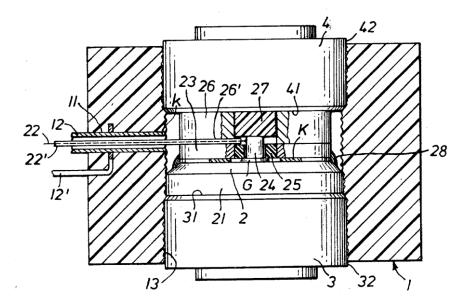

Apart from having an appropriate gate lead and gate electrode alignment, the device is also required to resist environmental contamination (e.g. due to moisture and dust) to avoid potential failure during service. Together with using an ideal enclosure, different patented inventions have also revealed ensuring a close fit between the pole piece components and housing can result in a good barrier between the outside environment and basic unit of the thyristor. Examples of such a design feature, that can be extended to the NEWTON polymer housing, are shown in Figures 2.4 and 2.7. Figure 2.4 by Brandt et al., 1980 (introduced in section 2.2.2) describes a sealed housing achieved by the corrugated copper edges which are surface roughened and coated with powdered plastic to improve adhesion with the external resin housing. The powdered plastic is a powdered lacquer of epoxy resins, polyester resins or polyurethane resins. On the other hand, another such design by Gerstenkoper et al., 1980 depicts an interference fit package formed by a toothed profile along the inner side of the package and an external larger diameter of the contacting discs (Figure 2.7).

Figure 2.7: Interference fit package (Gerstenkoper et al., 1980)

where 1 - elastomer annular housing; 2 - semiconductor wafer, or thyristor disc; 3, 4 - contacting discs; 11 - radial channel for accommodating gate terminal; 12 - metal tube for accommodating gate terminal; 21 - support disc; 31 - major surface of contacting disc 3; 13 - inner peripheral surface of housing 1; 22 - gate terminal lead; 22' - Teflon sleeve; 41 - major surface of contact disc 4; 32, 42 - outer peripheral surface of contacting discs 3, 4; 24 - silver cylinder, used as control electrode contact; 25 - centering ring, made of electrical insulating material; 23 - silver annular ring; 26 - copper annular ring; 27 - cylindrical plug, made of elastomer material, e.g. viton; 28 - silicone lacquer to fix ring 23, 24, and 25 in relative position

# 2.4 Thyristor device failure modes

Most thyristor failures occur due to exceeding the maximum operating ratings of the device - with overvoltage and overcurrent operations being more common failure causes. Other failure causes also tend to be due to mechanical damage in the form of excessive forces applied to the terminals during assembly of the thyristors (Littlefuse, 2008). This can lead to internal damage of the thyristor basic unit and crack formation. When the thyristor is electrically or physically abused in such a way, it can lead to either short-circuit or explosion failure. To mitigate potential failures due to these failure modes, various novel design concepts have also been patented over the years. Some housing designs identified from the patent review are described in the following sections.

#### 2.4.1 Short circuit failure

Short-circuit failure can be described as an unwanted low-resistance connection between two electrical circuit nodes, which are meant to be at different voltages. Unintentional short-circuits are usually caused either when there is insulation breakdown, or introduction of another conducting material – thereby allowing charge flow along the unwanted path. If a short-circuit leads

to an electrically overloaded connection or component, it can cause rapid overheating and lead to irreversible damage in other circuit components.

As described in Chapter 1, a number of thyristors are normally stacked in series to achieve the high total blocking voltage required in HVDC converters. In the event of a short-circuit, the silicon chip of the semiconductor device melts locally to form a hot spot over the entire thickness of the device as current flows. In this case, the faulty semiconductor device should ideally form a stable short-circuit and take the entire current to prevent an open circuit and failure of the entire stack (Gunturi et al., 2004). With the help of redundant thyristors that are included in the stacked thyristor assembly, such stable short-circuit failure should allow the non-faulty thyristors to continue operating normally and prevent unnecessary maintenance downtimes of the HVDC power station. The failed devices can then only be replaced during planned maintenance downtimes (typically 1 or 2 years). Different researchers have patented different power device designs aimed at improving their reliability, and also ensuring they continue operating normally due to short-circuit failure. Two such inventions that can also be extended to prevent short-circuit failure of the NEWTON thyristor are described next.

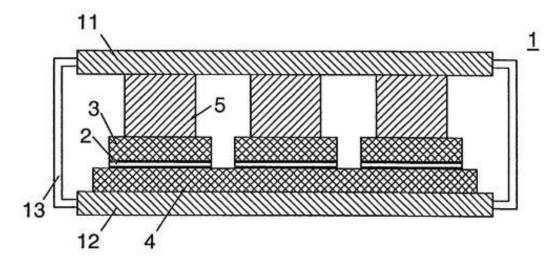

For instance, Gunturi et al., 2004 proposed a novel device design (Figure 2.8) whereby contacting either one or both electrodes of the semiconductor chip with a layer of metal matrix composite (MMC), both the thermo mechanical fatigue life and short circuit failure mode of the power semiconductor device takes longer to occur. This press-pack module design (Figure 2.8) consists of at least one semiconductor device (2) clamped between a conductive base plate (4), and at least one conductive top plate (3) enclosed in a housing (11, 12, 13). The package described here is also comprised of a novel metal matrix composite layer contacted to either one or both electrodes of the silicon semiconductor chip, and forms a eutectic mixture with the silicon material from the chip. The thermal coefficient of expansion of the layer is tailored to match that of the silicon chip to improve the thermo-mechanical property of the sandwich structure. To meet the electrical conductivity performance, the matrix of the layer is normally made of metals, such as silver, aluminium,

copper, or gold, while the reinforcement can be non-metallic, e.g. graphite or ceramic. Examples of such metal matrix composites are Al-graphite, Cu-graphite, Cu-Mo (Gunturi et al., 2004). In the event of a short circuit defect, when the entire sandwich structure consisting of the chip and MMC layer is heated, a conductive layer is formed between the contact layers once the melting point of the eutectic mixture is reached. This melting zone then extends across the entire silicon chip forming a stable conductive channel for the device to continue operating in the event of a short circuit. In this invention, because a MMC layer consisting of a high metallic content is used, a stable eutectic mixture with the Si from the chip is easily formed to ensure a longer operational time of the semiconductor module.

Figure 2.8: Press-pack semiconductor module (Gunturi et al., 2004)

where 1 - Press-pack module; 2 - Semiconductor device, chip; 3 - Composite top plate; 4 - Composite base plate; 5 - Contact piston; 6 - Bonding medium, solder; 11, 12 - Module housing power connections; 13 - Housing elements

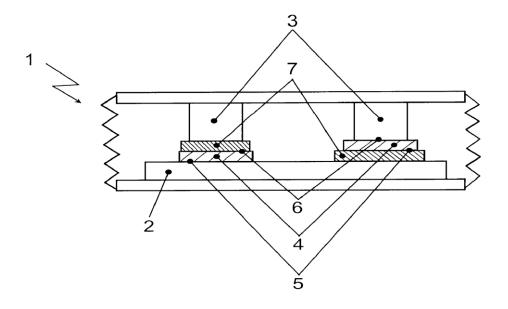

Another example of a power device design where short circuit defect can be mitigated is illustrated in Figure 2.9 (Lang et al., 1999). In this invention, an additional layer, e.g. silver (which can be a paste, foil, or solder component) is brought into contact with the electrodes of the semiconductor chip. The silver and the semiconductor (e.g. silicon) chip forms a eutectic mixture whose melting point is also below that of two partner materials. In the event of a short circuit, the entire sandwich structure is heated, and once the melting point of

the eutectic mixture is reached, a metallical conductive channel is formed on the contact surface between the silver layer and the affected silicon semiconductor chip. The channel is limited to one part of the chip area, but is able to carry the entire rated current, and thus prevents further heating of the rest of the chip and allowing the device to continue operating normally.

Figure 2.9: Semiconductor device (Lang et al., 1999)

where 1 - Housing; 2 - Substrate; 3 - Contact piston; 4 - semiconductor chip; 5, 6 - main electrodes; 7 - Layer (silver)

### 2.4.2 Explosion failure

Failure due to explosion in a semiconductor device normally originates when current initially flows at a defective point of the semiconductor power component to cause the silicon element to melt and evaporate. An arc is subsequently formed which spreads in a loop-shaped configuration to the connecting pieces of the housing that weld them together. This makes the pressure in the arrangement increase explosively causing the housing to be destroyed mechanically (De Bruyne et al., 1979).

Examples of some housing configurations proposed by De Bruyne et al., 1979 to reduce the pressure build-up in the housing (thereby mitigating failure due to explosion) are illustrated in Figures 2.10 to 2.12.

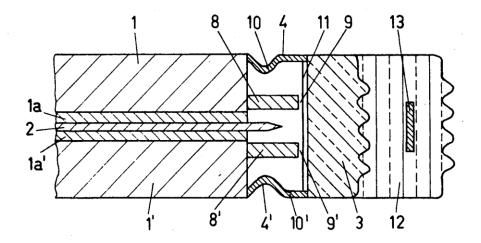

Figure 2.10: Semiconductor device with reinforced housing (De Bruyne et al., 1979)

Figure 2.10 shows a conceptual thyristor design aimed at reducing the severity of failure due to explosion. The device consists of a ceramic enclosure (3) enclosing a thyristor device (2) arranged between copper plates (1, 1'), and molybdenum plates (1a, 1a') contact pieces. To reduce the pressure build-up and explosion risk, the device also consists of different design features namely:

- current conductors (8, 8') made of copper surrounding the contact pieces - in the event of defect points that would cause arc formation and pressure build-up, the current conductors would retain the arc formed firmly on the conductors and prevent them from spreading to the contact pieces (1, 1', 1a, 1a') and the connecting pieces (4, 4')

- thermally and electrically insulating plastic coating (10, 10', 11) which is

made of a slow vaporising plastics e.g. Sylgard (a silicone resin

material), or Teflon (a tetrafluoroethylene fluorocarbon polymer)) the

plastic coating, which is found on the connecting pieces and interior of

the housing, aims to retard the development and propagation of arc

that would result in the explosion of the device

a reinforcing element (12) made of plastics such as polyvinylchloride joined in the radial direction with the housing (3). This element that can optionally be included in the housing is comprised of a fibreglass or steel ring inlay aims at increasing the mechanical strength of the housing and reducing damage due to explosion.

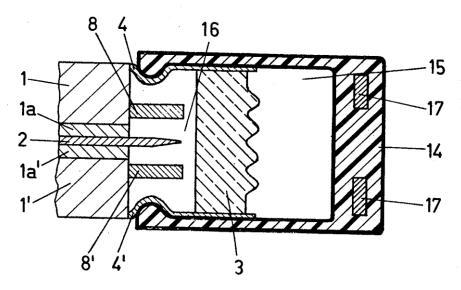

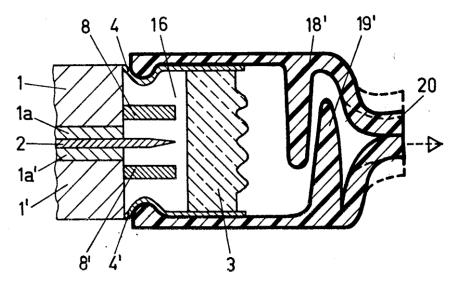

Other housing embodiments also disclosed by De Bruyne et al., 1979 aimed at mitigating damage due to explosion, are also shown in Figures 2.11 and 2.12. The device in Figure 2.11, which consists of an explosion guard (14) made of cast resin or silicone rubber, reduces the risk of damage to other parts in an installation by intercepting any hot gases and fragments generated by an explosion. In this arrangement, the space in between the housing (5) and the guard, which is considerably larger than the space (16) enclosed by the housing (5), reduces damage due to explosion by keeping the pressure and temperature build-up to a minimum. The guard also has improved explosion resistant properties due to its improved mechanical strength properties. This is achieved by providing it with reinforcing rings (17) to absorb radial forces due to pressure build-up. Compared to the housing guard in Figure 2.11, the arrangement in Figure 2.12 also improves resistance due to explosion by using a housing design that acts as an overpressure valve. The outer housing here is composed of flow resistance (18', 19') and sealing lips (20) which function as an overpressure valve at the end faces of the device. In the event of an explosion, the sealing lip (20) deform in the manner shown by the dash lines to permit the controlled release of explosion gases in the direction shown in the figure.

Figure 2.11: Explosion guard housing (De Bruyne et al., 1979)

Figure 2.12: Overpressure valve like housing (De Bruyne et al., 1979)

# 2.5 Summary

In this chapter, an overview of different design concepts for press-pack thyristor packages has been described. The review summarises a study of different patents and published literatures, and also aims to avoid potential commercial and intellectual rights issues that may occur with respect to any thyristor package design that may be developed in the future. From the literature review, different thyristor design configurations have been observed

to have been developed in the past to meet requirements for improved performance. They have also helped identify different housings that contain key design features aimed at mitigating failure modes, such as short circuit and explosion, common to these devices. An overview of the different housing designs reviewed in this chapter is described next.

From the review of different published literatures, it was seen that attempts to develop hermetic and polymer-based non-hermetic thyristor housings have already been made in the past. Hermetic thyristor housings that were developed were based on either a one-part or two-part configurations. Materials that were used to build them were ceramics and aluminium oxide, whilst for non-hermetic housings polymers were used. Examples of polymeric materials used in the past include epoxies and polyimides.

On the other hand, to mitigate failures due to short-circuit in semiconductor devices, previous inventions have consisted of contacting the electrodes of the semiconductor element with either a layer or foil consisting of a material that can easily form an eutectic mixture with the semiconductor material in the event of a short circuit. When the sandwich structure of the semiconductor element and contacting material is heated during the short circuit, a stable conductive channel should then form between the contact layers once the melting point of the eutectic mixture is reached. This should ensure a longer operating time of the failed semiconductor module and avoid unplanned stoppage of the HVDC system. Examples of materials that have been used in previous inventions for the contacting layers have been silver, or metal matrix composites e.g. aluminium-graphite, copper-graphite, copper-molybdenum. Finally devices aimed at reducing failure due to explosion have consisted of adopting approaches, such as attaching a reinforcing element around the semiconductor housing to improve the strength. Examples of reinforcing materials that have been utilised in the past include plastic elements, such as polyvinylchloride or cast resin with optionally a fibreglass or steel ring inlay included in it to absorb radial forces due pressure increase more effectively.

# 3 Failure modes of thyristor devices

#### 3.1 Introduction

In any product development and design effort, the goal is to produce a new product that is successful in the marketplace and results in maximum value to the manufacturer and user of the product. To achieve this goal, the product must be effectively designed and developed, and be of high reliability.

Reliability is defined as the probability that a device will perform its required function under stated conditions for a specific period of time. The longer the required lifetime, the greater is the demand on reliability to avoid potential failure (Di Giacomo, 1997). According to Bajenescu et al., 1999, one may distinguish failures as being of three types. First, there are failures that appear during the early period of life of a component, called early (or infantile) failures. They can be due to faulty manufacture or insufficient quality control during production, and can be reduced by a systematic screening test. The second type of failure is known as wear-out and is generally an indicator of the component ageing. Finally, accidental failures (the third category) are due to unexpected phenomena, such as sudden voltage increases, that can strongly influence the component quality and reliability. They appear randomly, and cannot be eliminated by screening (or burn-in) tests or preventive maintenance for example.

Most failures happen due to a complex set of interactions between the load acting on and within the system, and the materials and elements comprising the system. Dasgupta et al., 1991 categorised failure into four conceptual models, namely (1) stress-strength, (2) damage-endurance, (3) challenge-response, and (4) tolerance requirement. The stress-strength failure model identifies failures that are due to stresses exceeding the component strength (e.g. a steel bar in tension), while the damage-endurance model relates to

damage that accumulates irreversibly (e.g. corrosion, dielectric breakdown), and causes failure when the endurance limit of the device is reached. In the tolerance-requirement model, the system performance characteristic remains satisfactory only when the tolerance remains within requirement, whereas the challenge-response model relates to system failure due to an element that fails to respond when exposed to a stress. The development of a reliable product requires a thorough identification of potential failure mechanisms, i.e. the physical processes that may cause failure of the product by one or more of the conceptual models described above.

According to Dasgupta et al., 1991, different failure mechanisms, e.g. yield, dielectric breakdown, corrosion, etc., that are common in engineering systems can be broadly divided into two categories namely, overstress and wear-out. A description of the different overstress and wear-out failure mechanisms (identified by Dasgupta et al., 1991), is presented in the following sections. Section 3.2 describes the overstress failure mechanisms, while failures that commonly occur in the electronic systems due to wear-out are reviewed in section 3.3. Relevant failure mechanisms that are anticipated to be potential causes of failure in non-hermetic thyristors are then reviewed in section 3.4, before the concept of reliability and how it has been 'designed' in during the development of the polymeric thyristor package are defined in sections 3.5 and 3.6.

### 3.2 Overstress failure mechanisms

Overstress failures are defined as sudden catastrophic failures that happen due to a single occurrence of a stress event exceeding the intrinsic strength of a component (Dasgupta et al., 1991). Different investigations in the past have identified various overstress failure mechanisms that happen for example due to mechanical and electrical stresses, and which can be responsible for failures in both hermetic and non-hermetic electronic packages when they exceed the safe limit. Some examples of failure mechanisms identified by

Dasgupta et al., 1991 that fall into this category include large elastic deformation, plastic deformation, fracture and yield.

From studies by Suhir, 2007, Xie et al., 1998, Yao et al., 2003, etc., failure due to large elastic deformation in electronic devices have been seen to occur most often in slender structures, such as leads, wirebonds, etc. Although the materials behave elastically when they are deformed and no permanent change occurs, such failure results from excessive deformation due to overstress. Examples of some external factors that can contribute to such an overstress are the applied mechanical and vibration loads (Dasgupta et al., 1992). Plastic deformation and fracture are also other examples of failure mechanisms that result from mechanical stresses. Plastic deformation occurs when a component is stressed past its yield strength during operation. This then leads to plastic strain and permanent deformation due to a permanent change in the material. This subsequently fails the electronic package. Plastic deformation may or may not constitute a failure depending on the application. In electronic devices, various investigations, e.g. Sun et al., 2008, Dresbach et al., 2007, have shown that plastic deformation is a common occurrence in metallic elements, such as bond wires, solder, copper plated vias and metallisation.

Failure due to fracture in electronic systems can occur in two forms: brittle and ductile fracture. Brittle fracture originates from high stress concentrations at local microscopic flaws in brittle materials under overstress. The excessive overstress then causes sudden propagation of the dominant micro-crack and results in rapid failure. Such failures are common occurrences in hermetic packages made of ceramic and glass (Mathieu et al., 1993), and can lead to failure of the actual device through ingress of moisture and other corrosive substances. In ductile fracture, failure occurs due to sudden propagation of a pre-existing crack in the material under external stress. Compared to brittle fracture, ductile crack propagation is preceded by yielding that occurs at the crack tip. In electronic systems, such failures can arise in materials such as solder, aluminium and gold wires (Dasgupta et al., 1991).

Apart from the previously described mechanical failure mechanisms, electronic package failure can also be driven by exposure to electrical stresses above the design level. As identified by authors, such as Wang et al., 2003 and Dasgupta et al., 1991, dielectric breakdown is one common example of an electrical failure mechanism that contributes to failure of polymer-based electrical and electronic devices. It occurs due to failure of the dielectric of an electrical component when the applied voltage across the device stresses the dielectric beyond its dielectric strength, resulting in a sudden transition from an insulating to a conductive state.

#### 3.3 Wear-out failure mechanism

In the wear-out failure mechanism, failure occurs when the accumulation of incremental damage exceeds the material endurance limit. Dasgupta et al., 1991 categorised failures, such as fatigue crack initiation and growth, creep, wear, interdiffusion, corrosion, and radiation induced damage, as common examples of wear-out failure mechanisms occurring in electronic packages. An overview of these failure mechanisms is described next.

Fatigue failure usually occurs at stresses much below the ultimate tensile strength, and results from accumulation of damage when a component is exposed to a cyclic stress. Such failure can comprise of two stages, namely crack initiation and crack propagation, or the crack may develop from an existing point or discontinuity, such as a defect in the material grain structure, because of a local stress concentration. Once initiated, the crack then propagates under cyclic stress until the structure is weakened it becomes unstable leading to overstress failure. Past studies, e.g. Omiya et al., 2005, and Regard et al., 2008, highlighted such problems are encountered at locations, such as bond wires, copper plated vias, solder, etc., in electronic devices.

Creep and wear are also other examples of mechanical wear-out failure mechanisms in electronic devices. Compared to plastic and elastic deformation, creep is a time-dependent deformation. The deformation mechanism in polymers due to creep is different from those in metallic and ceramics structures because of their microstructure. In metals, it is due to grain boundary sliding, and intergranular or transgranular void migration, while in polymers the deformation is due to polymer chain reorientation. According to Dasgupta et al., 1991, failure due to creep is an issue at sites, such as solder joints and in printed circuit base materials at soldering temperatures.

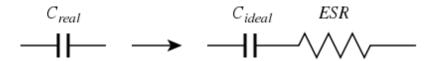

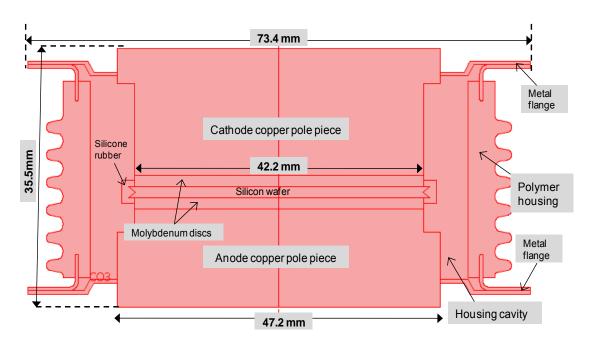

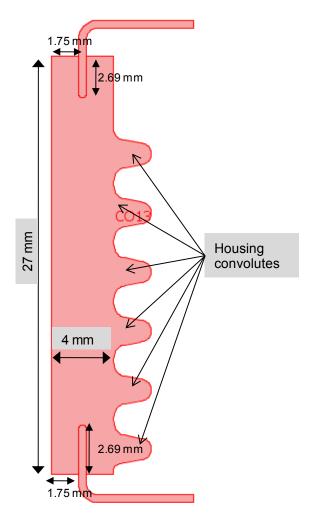

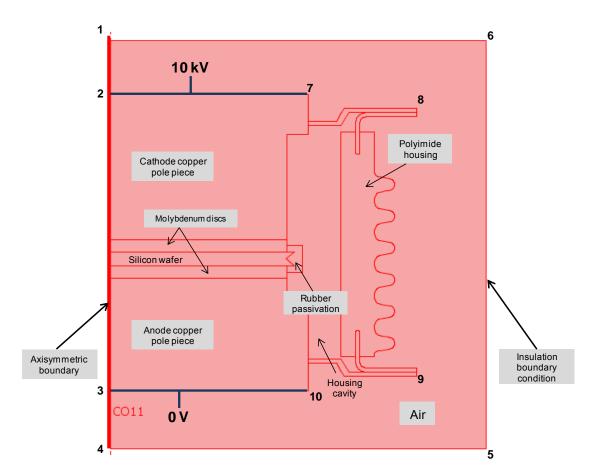

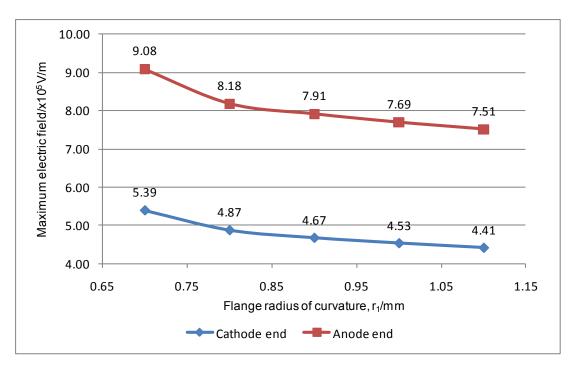

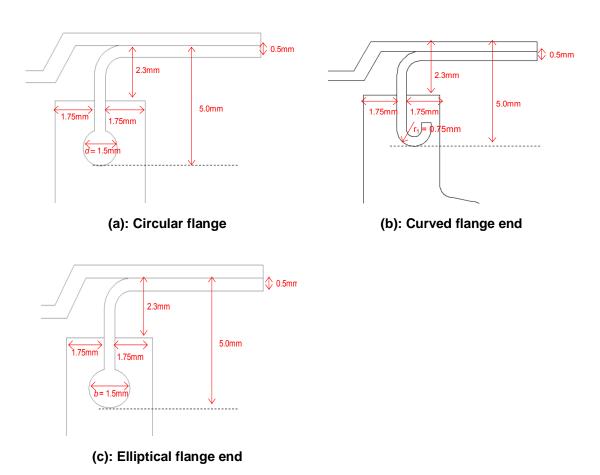

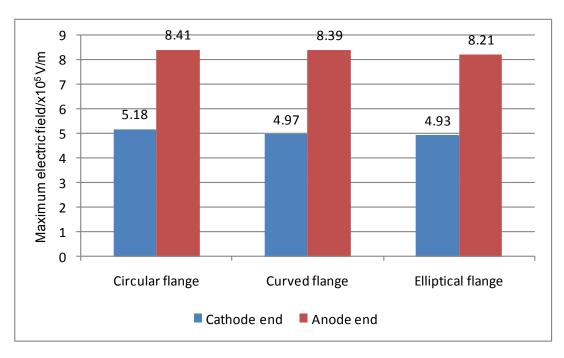

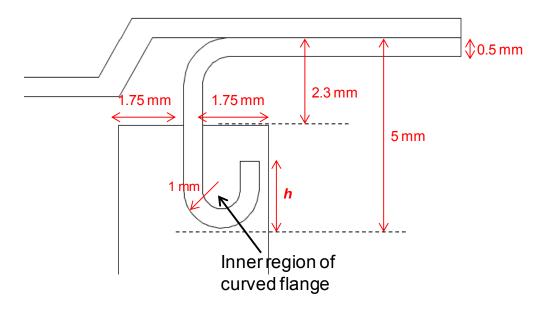

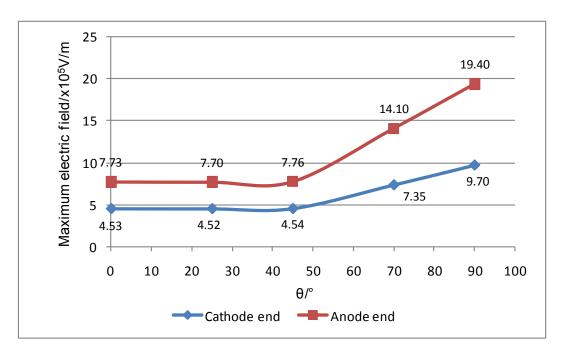

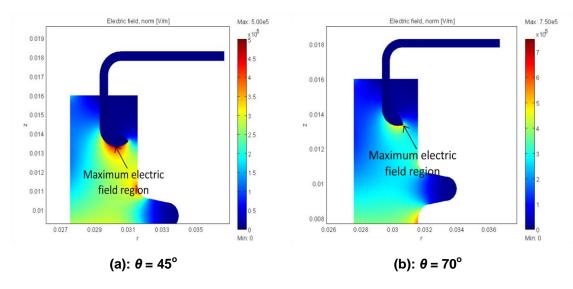

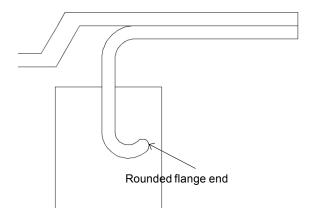

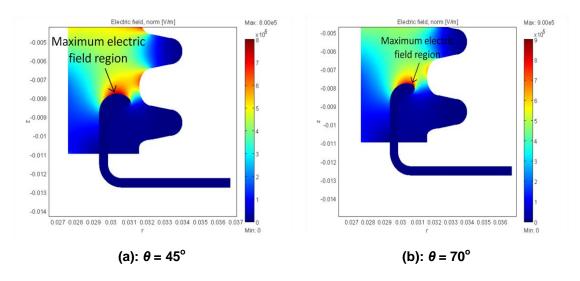

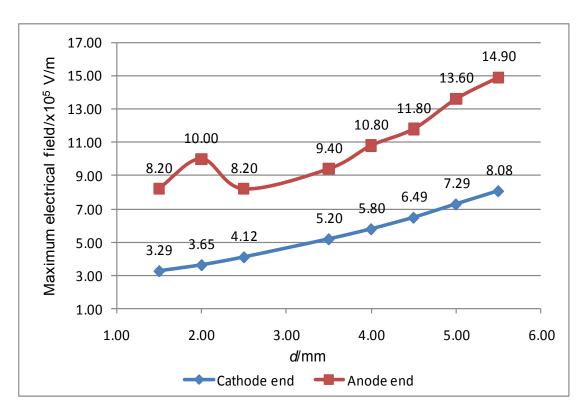

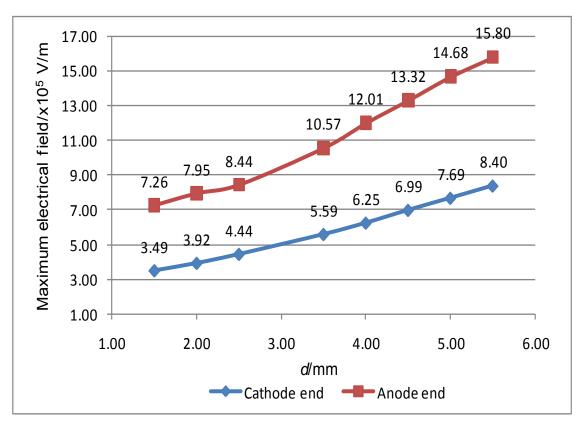

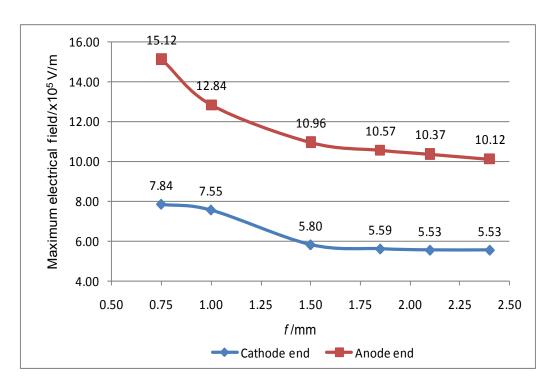

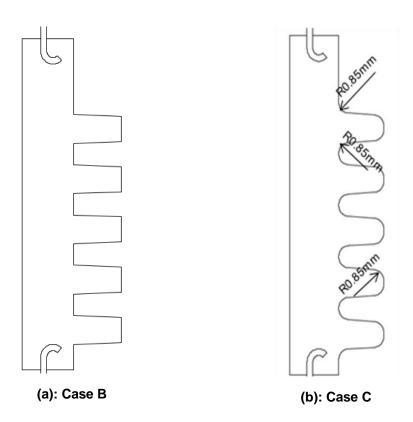

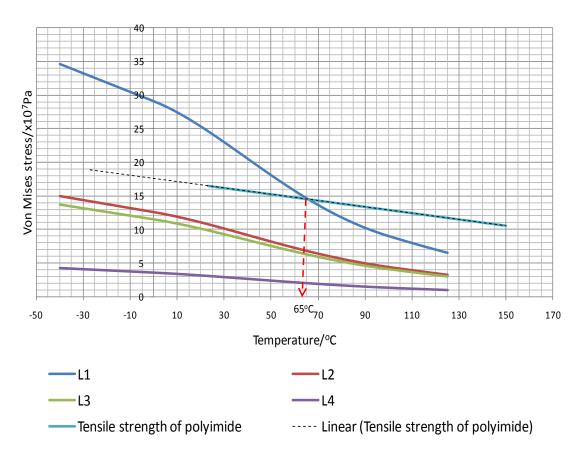

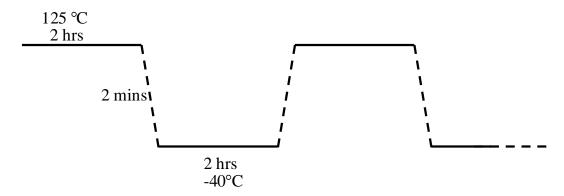

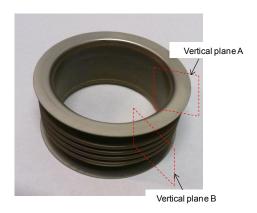

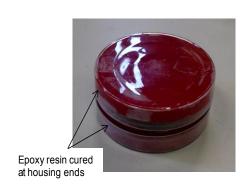

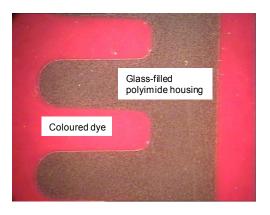

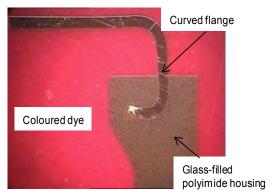

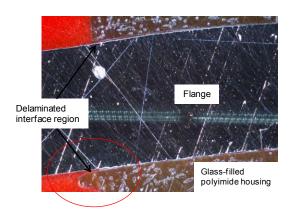

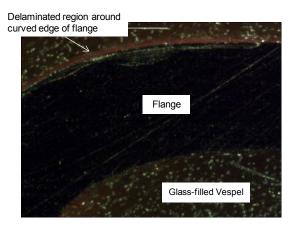

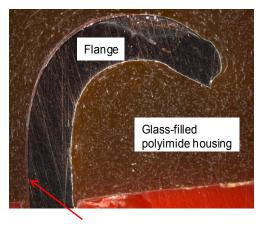

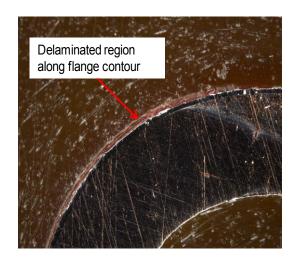

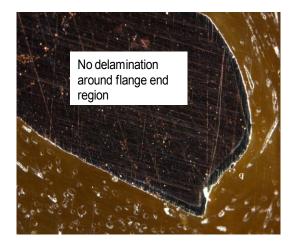

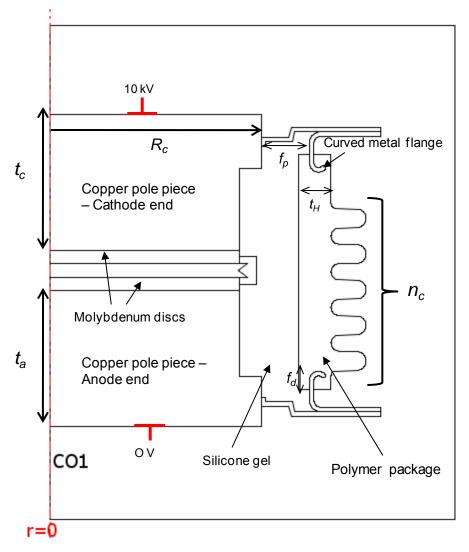

On the other hand, wear refers to the erosion of material resulting from the sliding motion of two surfaces under the action of a contact force. It can be grouped into five categories namely: (1) abrasive (when a hard material is sliding against a soft material), (2) surface fatigue, (3) corrosive (chemical), (4) thermal (mainly in polymers), and (5) adhesive wear which is common in connector mating surfaces in electronic packages.