This item was submitted to Loughborough's Research Repository by the author. Items in Figshare are protected by copyright, with all rights reserved, unless otherwise indicated.

# Parallel scheduling of concurrent VLSI simulation modules onto a multiprocessor

PLEASE CITE THE PUBLISHED VERSION

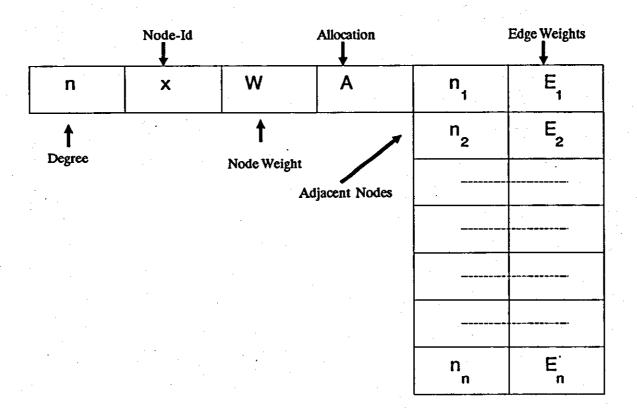

**PUBLISHER**

© M.A. Rahin

**PUBLISHER STATEMENT**

This work is made available according to the conditions of the Creative Commons Attribution-NonCommercial-NoDerivatives 2.5 Generic (CC BY-NC-ND 2.5) licence. Full details of this licence are available at: http://creativecommons.org/licenses/by-nc-nd/2.5/

LICENCE

CC BY-NC-ND 2.5

REPOSITORY RECORD

Rahin, Mohammad A.. 2019. "Parallel Scheduling of Concurrent VLSI Simulation Modules onto a Multiprocessor". figshare. https://hdl.handle.net/2134/27133.

This item was submitted to Loughborough University as a PhD thesis by the author and is made available in the Institutional Repository (<a href="https://dspace.lboro.ac.uk/">https://dspace.lboro.ac.uk/</a>) under the following Creative Commons Licence conditions.

C O M M O N S D E E D

### Attribution-NonCommercial-NoDerivs 2.5

### You are free:

· to copy, distribute, display, and perform the work

### Under the following conditions:

Attribution. You must attribute the work in the manner specified by the author or licensor.

Noncommercial. You may not use this work for commercial purposes.

No Derivative Works. You may not alter, transform, or build upon this work.

- For any reuse or distribution, you must make clear to others the license terms of this work.

- Any of these conditions can be waived if you get permission from the copyright holder.

Your fair use and other rights are in no way affected by the above.

This is a human-readable summary of the Legal Code (the full license).

Disclaimer 🗖

For the full text of this licence, please go to: <a href="http://creativecommons.org/licenses/by-nc-nd/2.5/">http://creativecommons.org/licenses/by-nc-nd/2.5/</a>

# BLDSC no: - DX 98140

# LOUGHBOROUGH UNIVERSITY OF TECHNOLOGY LIBRARY AUTHOR/FILING TITLE RAHIM, MA ACCESSION/COPY NO. 03600250 VOL. NO. CLASS MARK 15 FEB 1995 Lama Cory

036000250 1

| to the first of the second |   |   |

|----------------------------------------------------------------------------------------------------------------|---|---|

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   | , |

|                                                                                                                |   | • |

|                                                                                                                | , |   |

|                                                                                                                |   |   |

|                                                                                                                |   | / |

|                                                                                                                | • |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                | ` |   |

|                                                                                                                | • |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                | : | , |

|                                                                                                                | • |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

| · ·                                                                                                            |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   | i |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

|                                                                                                                |   |   |

# PARALLEL SCHEDULING OF CONCURRENT VLSI SIMULATION MODULES ONTO A MULTIPROCESSOR

by

### MOHAMMAD A. RAHIN

A Doctoral Thesis submitted in partial fulfilment of the requirements for the award of Doctor of Philosophy of the Loughborough University of Technology

July 1991

Supervisor: Dr. J. Sheild

Department of Electronic & Electrical Engineering

Loughborough University

of Technology Library

Chase May 92

Chass

Acc 03 6000 250

W9919443

# University of Technology

LOUGHBOROUGH LEICESTERSHIRE LEII 3TU

Telephone: 0509 263171 Ext. 4006 Telex: 34319

THE STUDENT OFFICE (HIGHER AWARDS)

### CERTIFICATE OF ORIGINALITY

This is to certify that I am responsible for the work submitted in this thesis, that the original work is my own except as specified in acknowledgements or in footnotes, and that neither the thesis nor the original work contained therein has been submitted to this or any other institution for a higher degree.

Mohammad A. Rahin 25 July, 1991.

to my parents

### ABSTRACT

This thesis reports on the research into multiprocessor based task scheduling algorithms as applied to the assignment of VLSI simulation modules onto a multiprocessor. Task scheduling falls into the category of combinatorial optimisation problems and is known to be NP-Hard. The goal of this research is to implement parallel heuristic scheduling algorithms for a general purpose multiprocessor system and to evaluate through simulation their relative performances.

The multiprocessor task scheduling problem in the context of VLSI simulation is presented first followed by a taxonomy of general scheduling algorithms. The factors determining the quality of a schedule are identified and an objective function that guides the heuristic algorithms is then formulated.

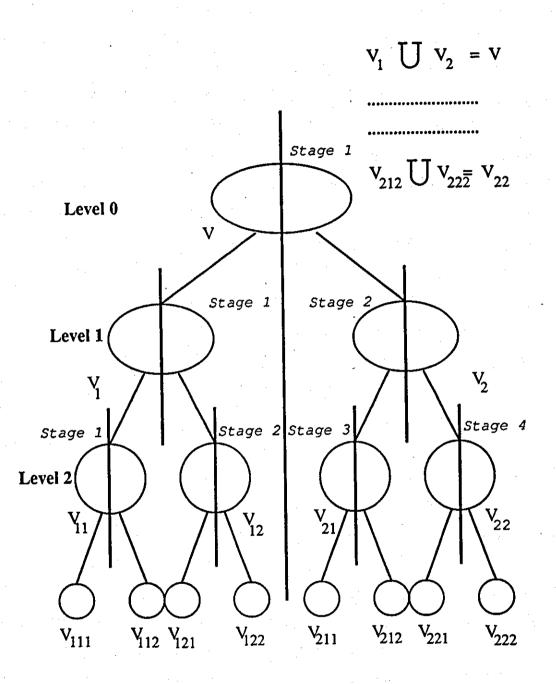

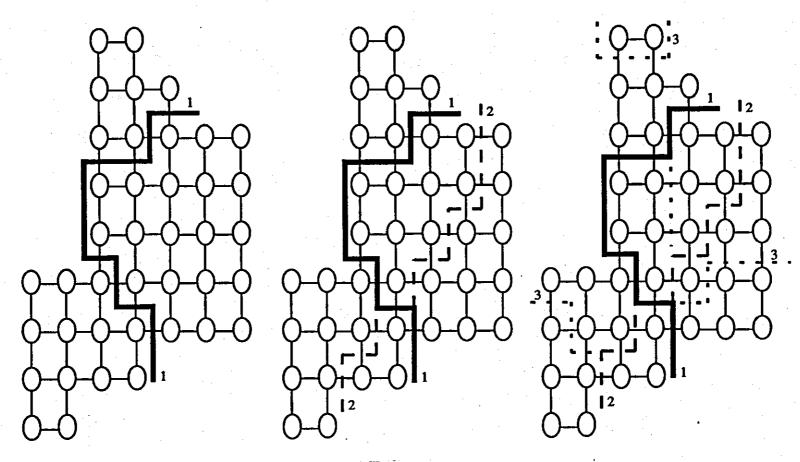

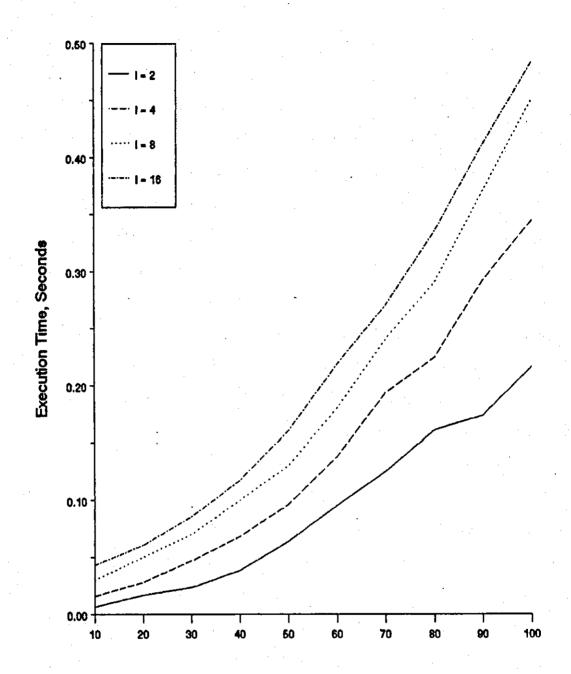

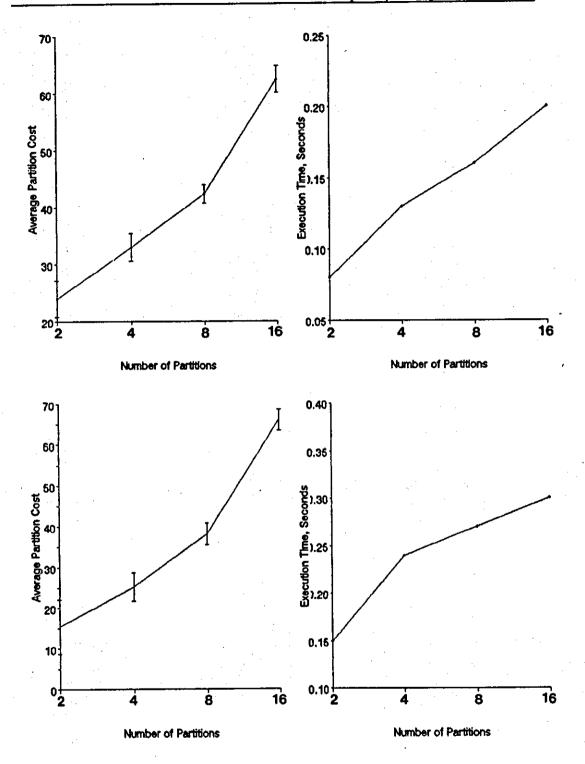

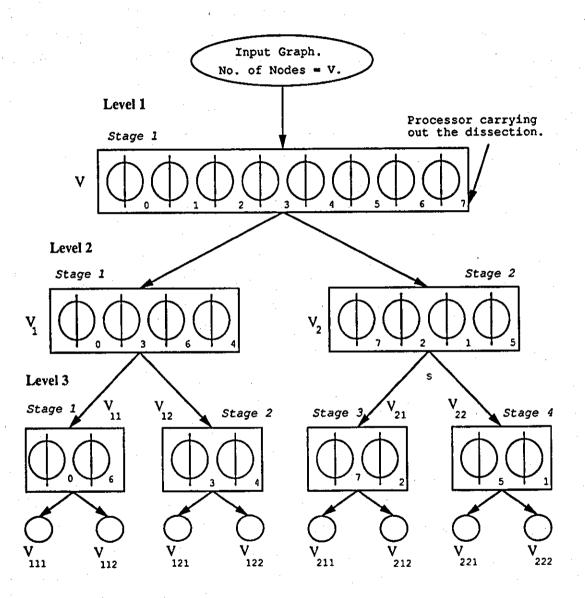

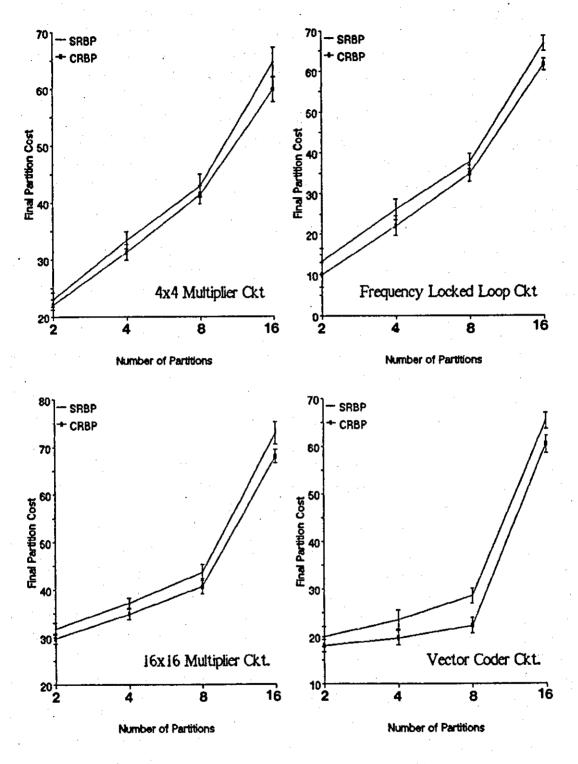

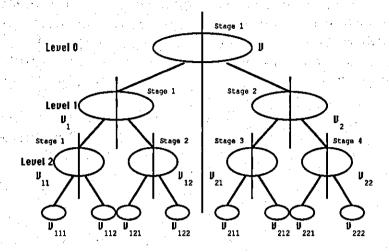

The first of the two algorithms examined is the Concurrent Recursive Binary Partitioning (CRBP). This heuristic is based on Kernighan-Lin's graph bi-partitioning algorithm. A *l*-way partition is achieved by applying binary partitioning recursively, the procedure taking the form of a binary tree. In its parallel implementation each node of this tree is executed independently by a group of available processors and only the best among the solutions obtained is accepted. This provides enhanced processor utilisation and also assures improved results. The factors affecting the performance of the *l*-way partitioning heuristic at different stages are examined and their optimum values are investigated.

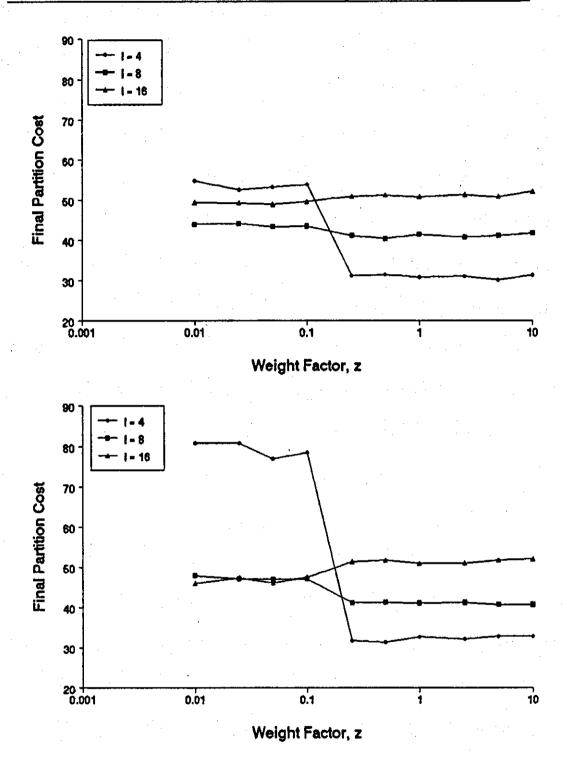

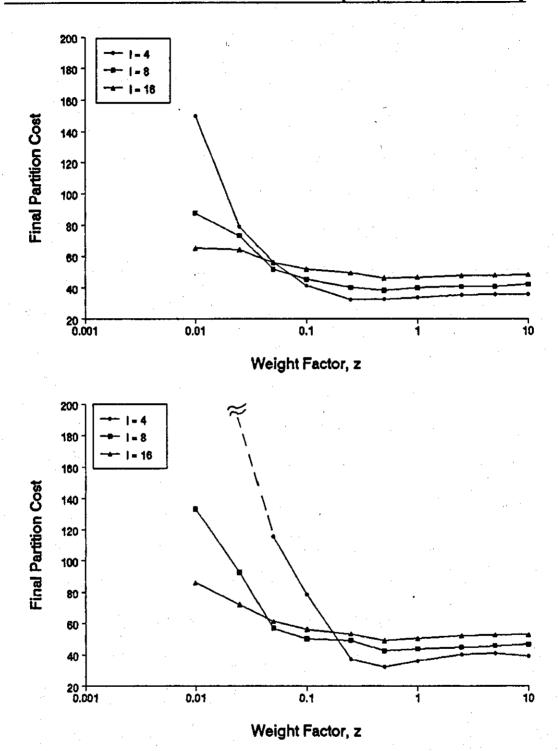

The other parallel algorithm examined is the Concurrent Simulated Annealing (CSA). Simulated annealing is a powerful and robust tool for the solution of many difficult combinatorial optimisation problems. In spite of its ability to produce good quality solutions, it is beset by exceptionally long CPU time demand. The parallel implementation presented here is an attempt to speed-up its convergence time and works with an optimal number of non-interacting parallel moves thereby assuring minimal error due to interaction between parallel moves. Two simple but effective temperature schedules are used. These temperature schedules are in a way dependent on the problem instance and as such adapt. themselves to the varying needs of the input problem instances.

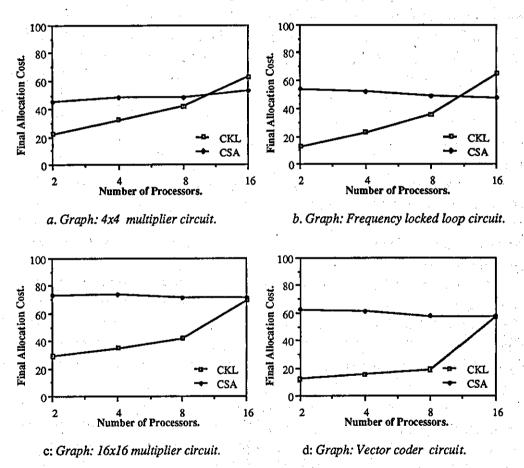

Both the parallel heuristics are subjected to synthetic as well as some actual VLSI simulation data instances. It is found that CRBP has an overall edge in terms of speed of execution and performs well for small number of processors. However, its solution quality deteriorates considerably with the increase of processors. CSA on the other hand, performs uniformly throughout and favours well for larger systems. For larger systems, CRBP has the potential to be used as a pre-processor for a combined CRBP-CSA heuristic.

### **ACKNOWLEDGEMENTS**

The author wishes to express his sincere thanks and gratitude to his supervisor Dr. J. Sheild for his continuous guidance and unending encouragement throughout the course of the research work. The author is also indebted to Dr. S. Datta for his moral and material support especially during the preparation of this thesis.

The financial support of the Association of Commonwealth Universities under whose Commonwealth Scholarships Programme the author was sponsored is gratefully acknowledged. The helpful and sympathetic administration of the above scholarship by The British Council is greatly appreciated.

Last, but not the least, a special heartfelt thanks goes to all the friends and acquaintances whose help, direct or indirect and company certainly made the author's time spent in Loughborough an enjoyable one.

# CONTENTS

| ABSTRACT                                                      | -  |

|---------------------------------------------------------------|----|

| ACKNOWLEDGEMENTS                                              |    |

| CONTENTS                                                      |    |

| CHAPTER 1: Introduction                                       | 1  |

| 1.1 Multiprocessors & Multicomputers                          | 2  |

| 1.1.1 Speed-up in a Multiprocessor                            | 6  |

| 1.1.2 Factors Determining the Performance of a Multiprocessor | 8  |

| 1.2 Application of Multiprocessors in VLSI Design             | 0. |

| 1.2.1 VLSI Design Processes                                   |    |

| 1.2.2 Acceleration of VLSI Design Process                     | .2 |

| 1.2.3 VLSI Circuit Simulation                                 |    |

| 1.3 Multiprocessor Task Scheduling                            | .7 |

| 1.4 Outline of the Dissertation                         |         |

|---------------------------------------------------------|---------|

| References                                              | 20      |

| CHAPTER 2: The Task Scheduling Problem                  | 22      |

| 2.1 Complexity of Task Scheduling Problem               |         |

| 2.1.1 Parallel Algorithms                               | 25      |

| 2.2 Classification of Task Scheduling Algorithms        |         |

| 2.2.1 Static vs. Dynamic Scheduling                     | 28      |

| 2.2.2 Optimal vs. Sub-optimal scheduling                | 29      |

| 2.2.3 Approximate vs. Heuristic Solutions               | 29      |

| 2.2.4 Load Balancing                                    | 30      |

| 2.3 Optimal and Sub-optimal Approximate Techniques      | 31      |

| 2.3.1 Solution Space Enumeration and Search             | 31      |

| 2.3.2 Graph Theoretic                                   |         |

| 2.3.3 Mathematical Programming                          | 31      |

| 2.3.4 Queing Theoretic                                  | 32      |

| 2.4 Heuristic Technique                                 | 32      |

| 2.4.1 Constructive Method                               | 32      |

| 2.4.2 Iterative Improvement Method                      | 33      |

| 2.5 Local Minima and Optimal Solution                   | 35      |

| 2.6 Contribution of this Dissertation                   |         |

| References                                              | 40      |

| CHAPTER 3: The Graph Model                              | 43      |

| 3.1 Graphical Representation: Background                |         |

| 3.2 Concurrent VLSI Timing Simulation                   |         |

| 3.2.1 VLSI Circuit Partitioning Algorithm               |         |

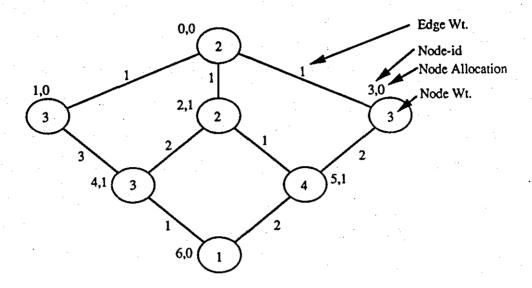

| 3.3 The Graph Model                                     |         |

| 3.4 Communication and Computation                       | 53      |

| 3.5 Formulation of the Cost Function                    |         |

| 3.6 Graph Data Storage & Cost Calculation               | 59      |

| 3.6.1 Graph Data Storage                                |         |

| 3.6.2 Cost Calculation                                  | 65      |

| 3.6.3 Cost Calculation in Iterative Improvement Environ | nment65 |

| References                                              | 69      |

| CHAPTER 4: Graph Partitioning                             | 70         |

|-----------------------------------------------------------|------------|

| 4.1 Graph Bi-Partitioning                                 | 71         |

| 4.1.1 The Modified KL Bi-Partitioning Heuristic           | 73         |

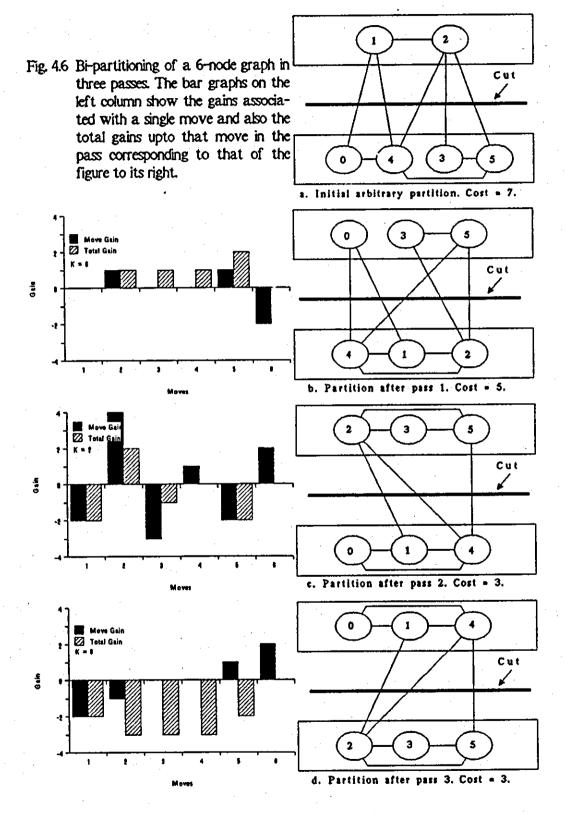

| 4.1.2 The Bi-Partitioning Algorithm in Action             | 35         |

| 4.2 Multiple-way Partitioning                             | 36         |

| 4.2.1 Recursive Binary Partitioning 8                     | 39         |

| 4.2.2 Concurrent Recursive Binary Partitioning            | <b>)</b> 5 |

| 4.2.3 Performance of Recursive Binary Partitioning        | 99         |

| References                                                | )1         |

| CHAPTER 5: The Simulated Annealing Algorithm 10           | )2         |

| 5.1 Combinatorial Optimisation and Simulated Annealing 10 | )3         |

| 5.1.1 The Simulated Annealing Algorithm                   | )3         |

| 5.2 Markov Chain Model of SA                              | )8         |

| 5.3 Cooling Schedule                                      | 13         |

| 5.3.1 A Simple Cooling Schedule                           | 15         |

| 5.3.2 A Polynomial-Time Cooling Schedule                  | 16         |

| 5.4 Implementation of the SA Algorithm                    | 22         |

| 5.4.1 Concise Problem Representation                      | 22         |

| 5.4.2 Transition Mechanism                                | 22         |

| 5.4.3 The Cooling Schedule                                | 23         |

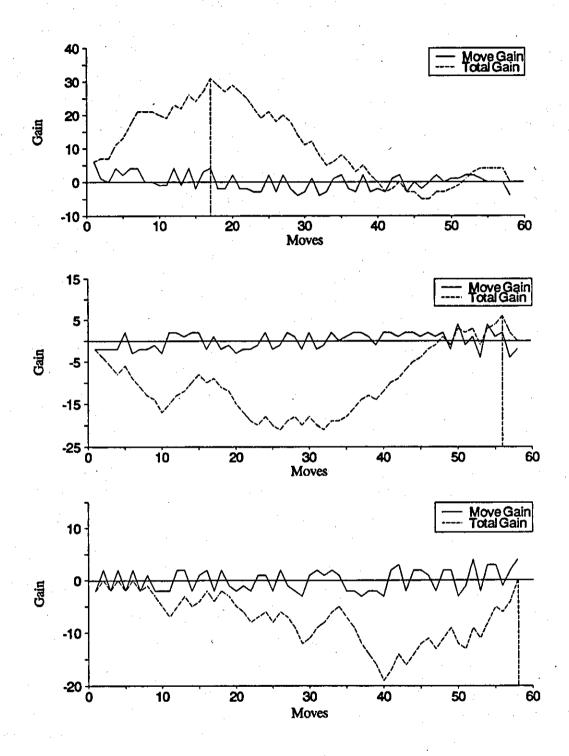

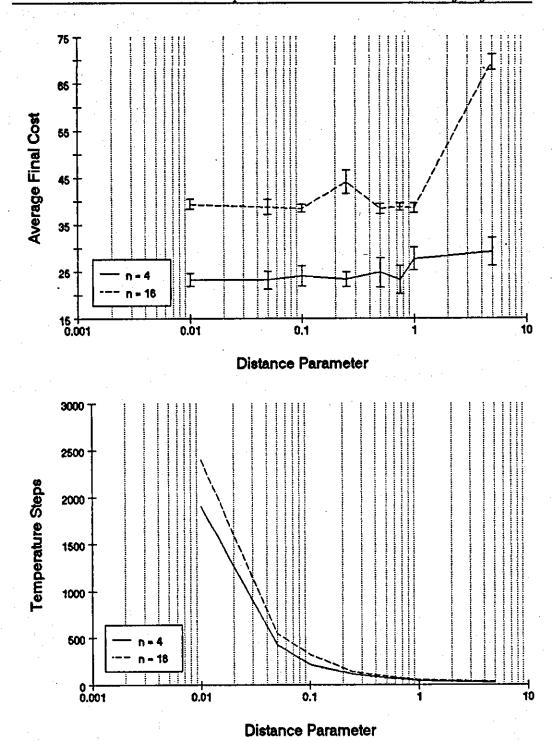

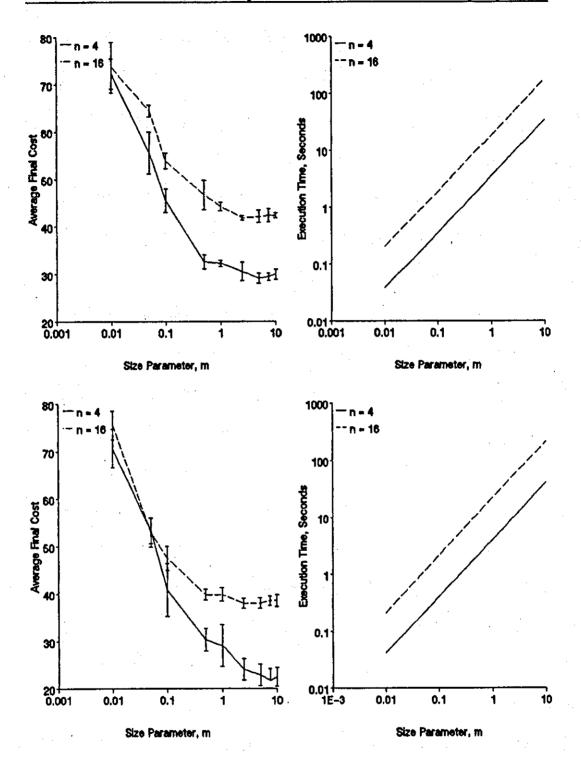

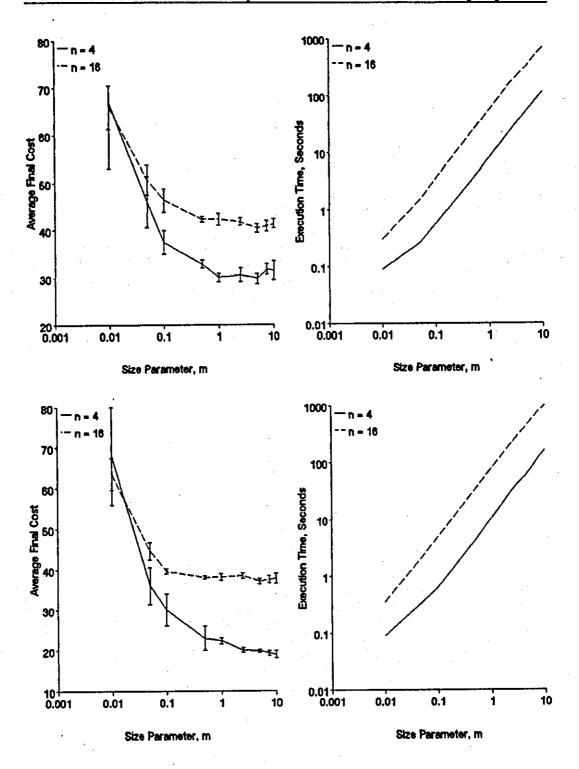

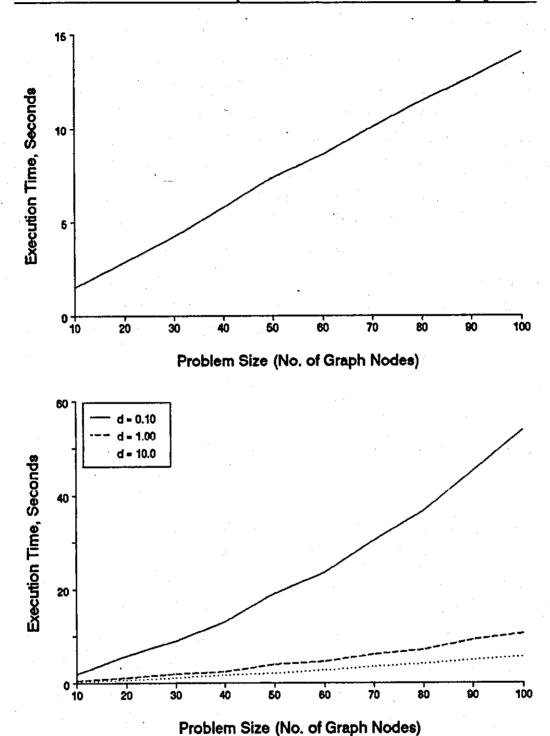

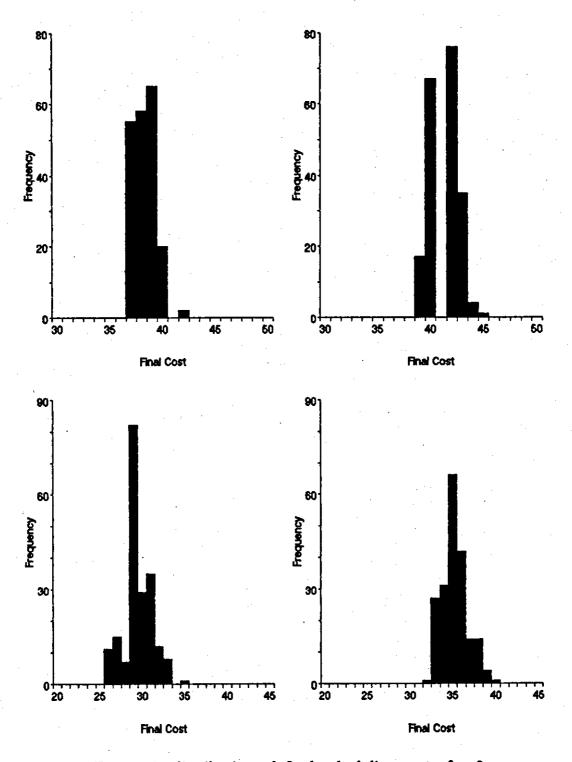

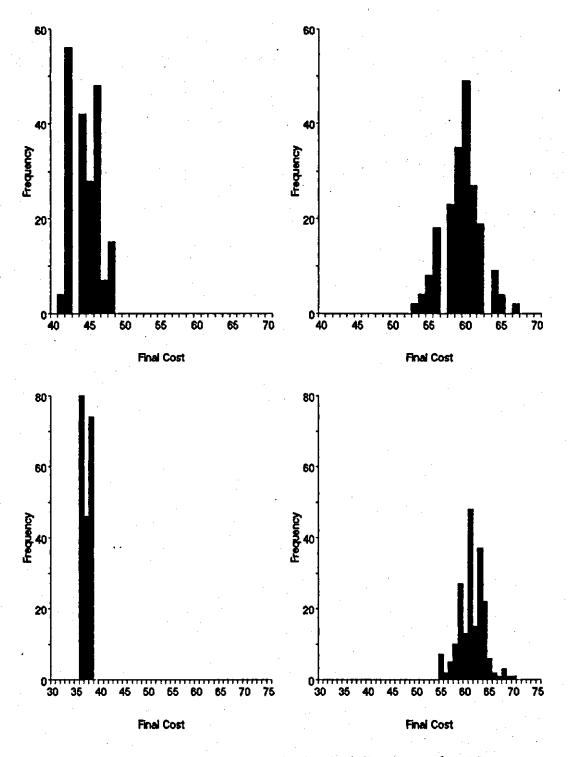

| 5.4.4 Performance Analysis of the SA Algorithm            | 29         |

| References                                                | 15         |

| CHAPTER 6: Concurrent Simulated Annealing 14              | 17         |

| 6.1 Speeding-up the SA Algorithm                          | 18         |

| 6.1.1 Fast Sequential ALgorithm                           | 18         |

| 6.1.2 Hardware Accelerators                               | 19         |

| 6.1.3 Design of Parallel Algorithms                       | 19         |

| 6.2 Parallel Annealing Algorithms                         | 51         |

| 6.3 Concurrent Simulated Annealing                        | 57         |

| 6.3.1 Parallel Moves and Move Interactions15              | 57         |

| 6.3.2 CSA Parallel Move Algorithm                         | 59         |

| 6.3.3 Parallel Accept/Reject Decisions16                  |            |

| 6.3.4 CSA Implementation Models                           | 71         |

| 6.4 Simulation Results                                    | 77         |

### CONTENTS

| References                                              | 179 |

|---------------------------------------------------------|-----|

| CHAPTER 7: Conclusions & Discussion                     | 181 |

| 7.1 Review of Results                                   | 182 |

| 7.2 Recursive Binary Partitioning & Simulated Annealing | 190 |

| 7.3 Conclusions                                         | 192 |

| 7.4 Discussion                                          |     |

| References                                              | 199 |

| APPENDIX A                                              | 200 |

| APPENDIX B                                              | 211 |

# CHAPTER 1

# Introduction

Ever increasing processing demands as encountered in different fields such as image processing, artificial intelligence, finite element analysis problems, weather forecasting, wind tunnel simulations, nuclear system, particle physics etc. have led the researchers to the development of several conventional high performance computers as well as conceptually new architectures namely non von Neumann systems and most importantly multiprocessor systems.

It has been identified quite long ago that the conventional uniprocessor computers are unable to meet the performance requirements of many computing intensive applications. Since, the first electronic digital computer (ENIAC) was built in 1945, the advances in uniprocessor computers can be attributed primarily to development of logic technology. Switching speed fell from one tenth of a second to nano seconds as the logic technology moved from electro-mechanical relays to vacuum tubes to transistors and

then to small, medium and large scale integrated circuits. In the last few years, it has become more difficult to achieve order of magnitude of speed-ups in computers by solely upgrading the logic technology, as the physical laws have been found to be the primary limiting factor. Radically different computer architectures namely Data-Flow Machines [1] have been proposed to overcome the bottleneck associated with the conventional von Neumann computers, but failed to attract wide spread acceptance as initially anticipated. The most obvious solution to the problem to date seems to lie in the exploitation of parallelism in the applications and executing the mutually independent task modules concurrently on a multiprocessor system. MIMD multiprocessors with multiple instruction-streams and multiple data-streams promise to be the general purpose computers of the future. Several commercial MIMD computers have already arrived in the market, e.g. those manufactured by Alliant, BBN, Cray, ELXSI, Encore, IBM, Intel, NCUBE, Sequent etc.

### 1.1 Multiprocessors and Multicomputers

Modern computer architectures can be classified in many different ways. One of the most popular higher level architecture wise classification is due to Flynn [2]. Flynn based his taxonomy of computer architectures on the concepts of instruction stream and data stream. An instruction stream is a sequence of instructions performed by a computer; a data stream is a sequence of data used to execute on instruction stream. Flynn categorised an architecture by the multiplicity of hardware used to manipulate instruction and data streams. Given the possible multiplicity of instruction and data streams, four classes of computers result.

1. SISD (Single Instruction stream, Single Data stream): Almost all single processor computers fall into this category. Although instruction execution may be pipelined, computers in this category can decode only a single instruction in unit time. A SISD computer may also have multiple functional units (e.g. CDC 6600) being governed under the direction of a single control unit.

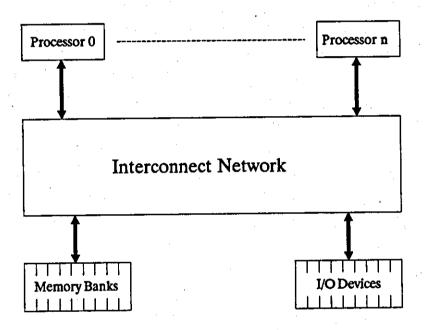

Fig. 1.1 A shared memory multiprocessor.

- 2. SIMD (Single Instruction stream, Multiple Data stream): Processor arrays fall into this category. A processor array executes a single stream of instruction, but contains a number of arithmetic processing units, each capable of fetching and manipulating its own data. Hence, in any time unit, a single operation is in the same state of execution on multiple processing units, each manipulating different data.

- 3. MISD (Multiple Instruction stream, Single Data stream): No computers fall into this category.

- 4. MIMD (Multiple Instruction stream, Multiple Data stream): This is by far the most popular architecture for multiprocessors and well suited for future general purpose computing needs. MIMD computers are composed of a collection of full featured processing elements often with their own local or private memory and are capable of executing their own instructions independent of each other. The term MIMD is generally reserved for multiple CPU computers designed for parallel processing; that is, computers designed to allow interaction among their CPUs.

Flynn's classification scheme has been found to be too vague to allow a clear cut labeling of modern high performance computers. Kuck [3] enhanced Flynn's classification scheme into a more detailed form. Händler's [4] classification however accounts for the organisation of the main functional units of computers and uses some notations for expressing the piplining and parallelism. MIMD designs can be further classified into two major groups [5]:

1. Shared Memory Multiprocessors: Multiprocessors are characterised by a shared memory. Shared memory multiprocessors can be further classified into two, (a) Tightly Coupled and (b) Loosely Coupled. In the case of the tightly coupled multiprocessors, the simplest processor intercommunication pattern assumes that all the processors work through a central switching mechanism to reach a shared global memory (Fig.1.1). There are a variety of ways to implement this switching mechanism, including a common bus to global memory, a crossbar switch and a packet-switched network. Examples include Carnegie-Mellon's C.mmp, Denelcor's HEP, Sequent's Balance and Symmetry.

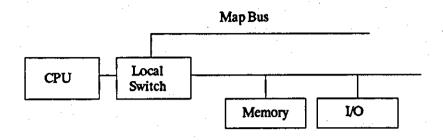

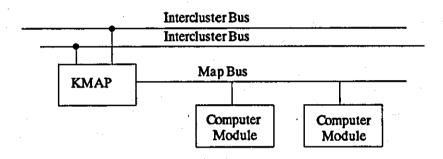

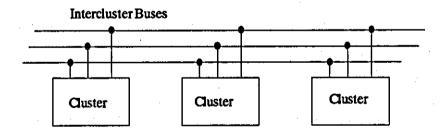

Fig. 1.2 The architecture of CM\*, a shared memeory loosely coupled multiprocessor. Computer module (top), cluster (middle) and network of clusters (bottom).

Like tightly coupled multiprocessors, loosely coupled multiprocessors are also characterised by a shared address space. Unlike tightly coupled multiprocessors, the shared space on a loosely coupled multiprocessor is formed by combining the local memories of the CPUs. Hence, the time needed to access a particular memory on a loosely coupled multiprocessor depends on whether that location is local to the processor. Examples include Carnegie-Mellon's Cm\*, BBN Butterfly.

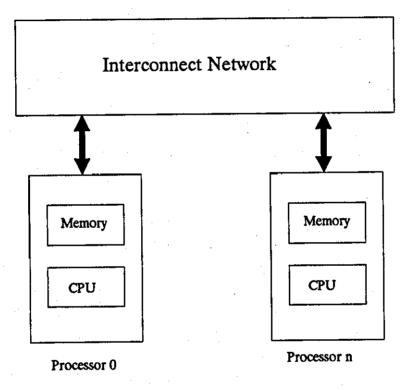

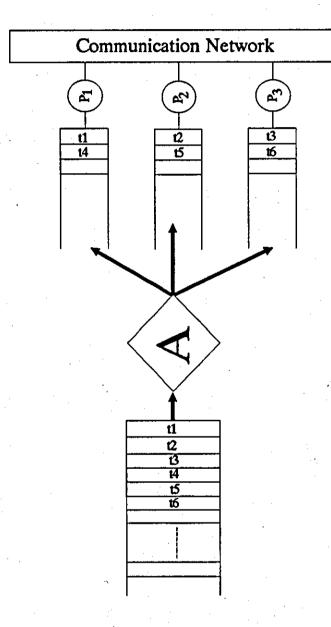

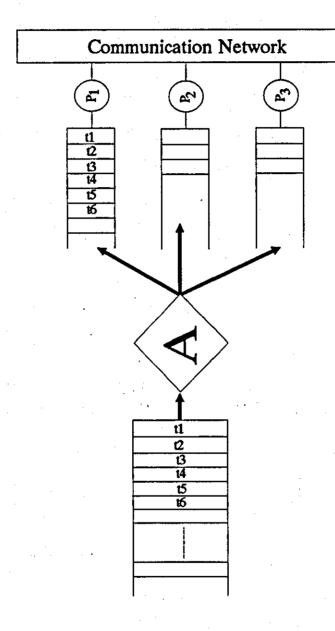

2. Message Passing Multicomputers: Figure 1.3 shows the general structure of a message passing multicomputer. Each processor has its own local memory, and process cooperation occurs either through sending or receiving messages. The performance and scalability of the multicomputer is primarily determined by the interconnection network. The simplest interconnection network for a multicomputer is a bus capable of handling interprocessor messages (i.e. a local area network). Distributed systems have this structure and can indeed be used as a multicomputer for applications with sufficiently large granularity. Intel's iPSC, NCUBE's NCUBE/10, Ametek's S/14 are commercial multicomputers.

# 1.1.1 Speed-up in a Multiprocessor

The speed-up that can be achieved by a multiprocessor with n identical processors working concurrently on a single problem is at most n times faster than a single processor running the same program. In practice, the speed-up is much less, since some processors are idle at a given time because of conflicts over memory access or communication paths, inefficient algorithm that fails to exploit the natural concurrency in the problem etc. Fig.1.4 shows the various estimates of the actual speed-up, where speed-up is defined as the ratio between the time taken by that parallel computer executing the fastest serial algorithm and the time taken by the same parallel computer executing the parallel algorithm using n processors.

The lower bound in Fig.1.4 is known as the *Minsky's Conjecture*, giving a rather pessimistic view. The upper bound  $\left(\frac{n}{\log n}\right)$  can be derived using simple assumptions and approximations [6].

Fig. 1.3 A message passing multicomputer.

# 1.1.2 Factors Determining the Performance of a Multiprocessor

The followings are the factors considered to be associated with the performance capability of a multiprocessor system:

- 1. Granularity: An important issue in multiprocessor performance is the granularity of program execution. The granularity of a parallel program can be defined as the average size of a sequential unit of computation in the program, with no interprocessor synchronisation or communication (e.g. the average task size). For a given multiprocessor, there is a minimum program granularity value below which performance degrades significantly. This threshold value can be termed granularity of the multiprocessor. It is desirable for a multiprocessor to have a small granularity, so that it can efficiently support a wide range of programs. It is also desirable for a parallel program to have a large granularity, so that it can be executed efficiently on a wide range of multiprocessors.

- 2. Scalability: Scalability is another important property of multiprocessors. Scalability is the ability of a multiprocessor to provide a linear speed-up with an increase in the number of processors, assuming that the program being executed has sufficient parallelism and a large enough granularity. A multiprocessor architecture is usually designed to be scalable up to some specific number of processors. There is a fine balance between granularity and scalability in a multiprocessor. Increased scalability is typically achieved at the cost of large granularity. On a general note, tightly coupled systems usually have a smaller granularity and scalability than loosely coupled systems.

- 3. Computation vs. Communication: The introduction of parallelism has led to problems of communication which did not exist in uniprocessor systems. In the multiprocessor environment, one would expect to split the computation and assign the task modules to different processors. Consequently, the processors need to communicate the results of their computations. The more complex the task division, the more complex will be the communication pattern. One has to be more careful not to degrade the system performance by overwhelming the communication.

Fig. 1.4 Various estimates of the speedup of an *n*-processor system over a single processor.

There is a trade-off between communication and computation in parallel systems. Ideally, one would like to reduce the communication overhead and increase the parallelism by further splitting of the computation. It is well established that the communication time in a multiprocessor environment can not be neglected. Agerwala [7] has studied the relationship between communication and computation and concluded that the reason for decreased performance of present multiprocessor systems is insufficient emphasis on the role of communication.

### 1.2 Application of Multiprocessors in VLSI Design

The rapid development of multiprocessors as well as the fall of their prices has opened up many new engineering application areas which have been suffering from heavy computing demand. One of these new application areas is VLSI engineering. In recent years, due to the availability of advanced semiconductor process technologies as well as computer aided design (CAD) systems coupled with ever increasing drive for higher integration, a tremendous growth in chip density is being observed. Already VLSI chips containing more than 1 million transistors has been announced [8]. This very high chip density is forcing an unacceptably long design turn around time. The size and complexity of the design are the main factors responsible for this. Different phases of VLSI design is bestowed with rich inherent parallelism. These can be effectively exploited and their multiprocessor implementation would then provide a much faster design and verification turn around time.

# 1.2.1 VLSI Design Processes

Design methodology in the context of VLSI circuits can be defined as a set of codified techniques that is applicable to the VLSI design process. Design functions of interest in the VLSI design methodology can be categorised as follows [9]:

- 1. Chip specification and partitioning;

- 2. Chip design planning and initial implementation;

- 3. Subcircuit and module synthesis;

- 4. Simulation at different levels:

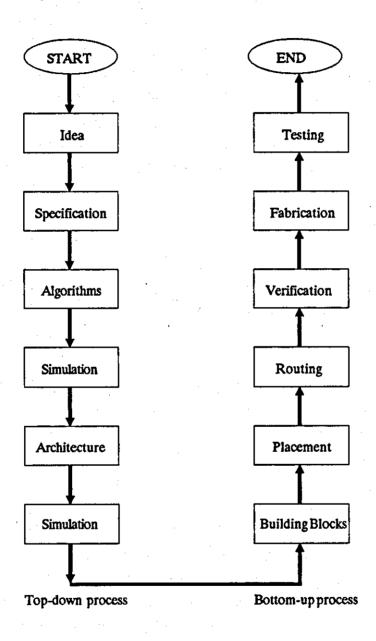

Fig. 1.5 The general design processes of a VLSI circuit.

- 5. IC mask layout;

- 6. Design verification;

- 7. Testability in design and product;

- 8. Test sequence generation;

- 9. Database management;

- 10. Design documentation.

The ultimate objective of studying design methodology is to facilitate the creation of better designs in less time. The prevalent design methodology today, and in the foreseeable future, is hierarchical in nature [10], where a set of universal circuits are designed, optimised, and stored in the library of a CAD system and the library circuits can be repeatedly accessed, modified, and used as building blocks to construct the desired system.

Figure 1.5 presents the overview of a typical VLSI design process. A top-down design flow is normally used to decompose the circuit under design into a network of smaller and simpler functional modules. Once a function implementation strategy has been established, a bottom-up flow is used to complete the physical design of the chip.

The design process begins by converting an idea for a VLSI circuit into more concrete circuit specifications. An algorithm is developed to perform the required operations and a suitable architecture is designed to carry out the chosen algorithm. Simulations are used to verify the correctness and to estimate the performance of both the algorithm and architecture. After the architecture of the circuit has been established, the design process enters the physical layout phase. Copies of the needed building blocks are fetched from the library, placed in some optimal manner, and interconnected as they will be on the chip. The layout is then simulated to verify its operation and performance with respect to the desired specifications. Finally layout mask is sent to a silicon foundry for fabrication.

# 1.2.2 Acceleration of VLSI Design Process

The simulation and verification phases of the design process of Fig.1.5 are composed of logic, timing, electrical and fault simulation and also *Design* Rule Checking (DRC) encompassing physical, thermal and connectivity

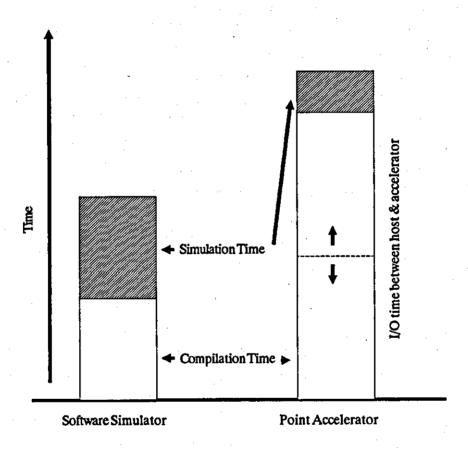

Fig. 1.6 I/O overhead in a typical point accelerator. Adapted from [12].

analysis. In league with the *Placement* and *Routing* phases, simulation is one of the most time consuming phases of a VLSI design. Placement and routing are difficult combinatorial optimisation problems and are known to be NP-Hard [11]. The simulation phase also have voracious appetite for CPU time often taking  $O(n^2)$  to  $O(n^3)$  time.

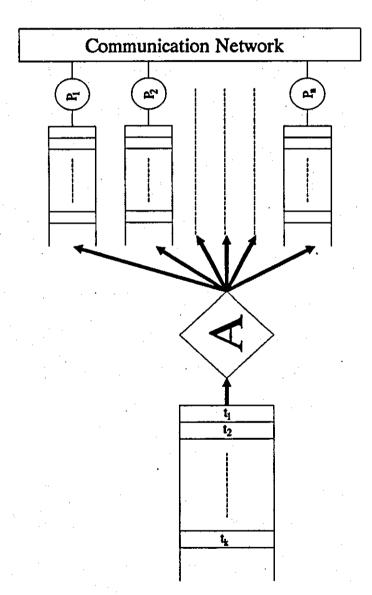

Several attempts have been made to speed-up the VLSI design process [11–19]. Two different approaches can be observed. The first approach is based on the use of dedicated special-purpose hardware device known as *Point Accelerators* [13–17]. These are usually single processor based special-purpose unit where the algorithm is realised in hardware and is attached to a design workstation. They provide very impressive speed-up factors at low cost some times upto a factor of 225 for relatively larger circuits [16]. Their main drawback however is that for smaller circuits the I/O bandwidth with the host workstation is too large to give any significant speed improvement (Fig.1.6). Also, as the algorithm is tied to the hardware, modification and upgrading becomes very difficult and expensive. Furthermore, they fare very poorly in integrating with the other phases of the VLSI design process.

The other approach is based on the exploitation of rich inherent parallelism present in the design phases and employing general-purpose multiprocessor systems [11,12,18,19]. This approach is becoming more attractive with the advancement of computer technology as well as with their falling prices. The design algorithm is almost fully software based. Modification and upgrading can thus be done very easily and inexpensively. Also, the same hardware can be used for the rest phases of the design.

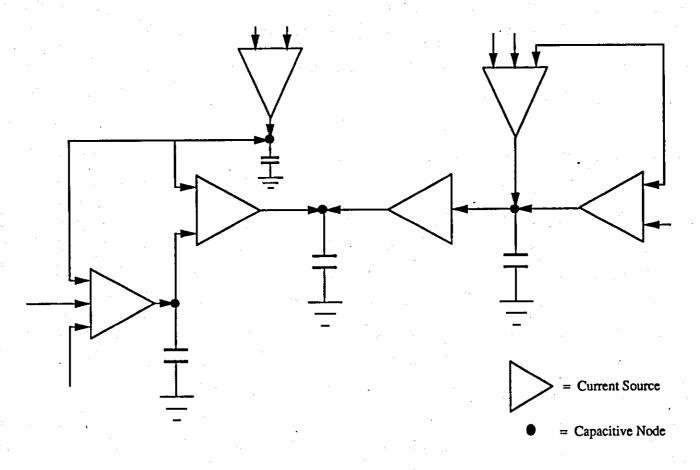

### 1.2.3 VLSI Circuit Simulation

Circuit simulation is one of the most important phases of a VLSI design process. A thorough and detailed analysis of the tentative design analysis is absolutely necessary before a very expensive fabrication begins. Design verification of a custom VLSI circuit takes place at a number of different levels of simulation as the design progresses. These range from logic simulation (using register-transfer level, gate level, or switch level simulation) to electrical simulation.

Electrical simulation usually provides a detailed and accurate analysis of a circuit. But is often too slow for simulation of large circuits. Circuit simulation using direct solutions, as in SPICE [20], is typically a factor of  $10^4$  to  $10^5$  slower than gate level logic simulation [21]. Several techniques for improving the speed of simulation have been proposed [17]. These include the exploitation of circuit latency by integrating only those circuit nodes which are changing voltages, using tearing techniques for matrix manipulations, deriving relaxation-based simulators that eliminate matrix decomposition. These improvements can give a speed-up factor of upto  $10^2$ , but is still inadequate for large circuits.

Switch level simulation, exemplified by RSim [22] and MOSSIM [23], uses event driven techniques and a logic level approximation of the network state. This results a very fast simulation compared to direct electrical simulation. Although the approximations are valid for many circuits, they often fail to produce correct results for many others. Another disadvantage of switch level simulation is that it typically provides only unit-delay timing information, or timing information that can have large errors for common circuits.

Timing simulation is a compromise between direct electrical simulation and switch level simulation. Compared to direct simulation this provides much higher performance at the cost of slightly lower accuracy. Also compared to switch level simulation, timing simulation provides better accuracy with limited analog effects such as rise and fall times, charge and current sharing and feedback. EMU [24] and MOTIS [25] identifies the regular use of driver-load gate structures and uses an approximate series-parallel formulae. Speed improvement techniques like discretisation of voltage into a small number of levels, and the calculation of time step for each node. Timing simulation claims improvements of upto 10<sup>3</sup> compared to direct electrical circuit simulation.

The accuracy of timing simulators can be improved further by decreasing the size of the time step. But, unfortunately, this increases the simulation time and for relatively larger circuits this may become very long. Table 1.1 shows the simulation time for four representative circuits ranging from

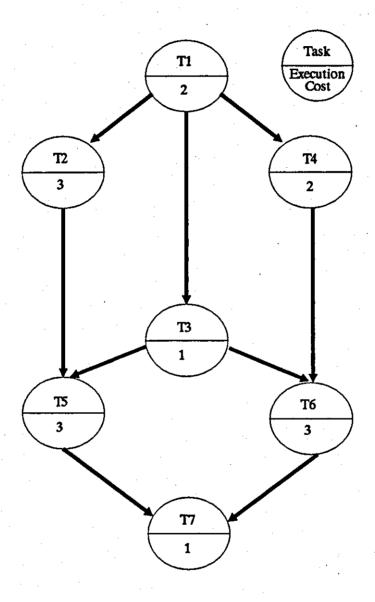

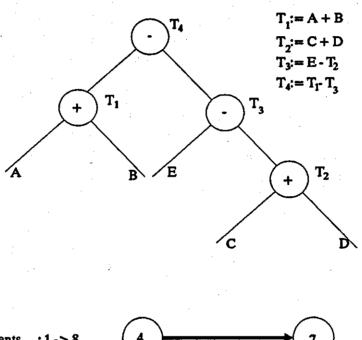

Fig. 1.7 A Computational Flow Graph (CFG), each node represents a subtask to be performed.

small to medium sizes for different time step when simulated with EMU on a conventional uniprocessor system.

|              |             |               | •            | •            |

|--------------|-------------|---------------|--------------|--------------|

| Time Steps   | 4x4         | Phased Locked | 16x16        | Vector       |

| in           | Multiplier  | Loop          | Multiplier   | Coder        |

| pico Seconds | (168 Nodes) | (167 Nodes)   | (2577 Nodes) | (1746 Nodes) |

| 100          | 11.00 Mins. | 18.78 Mins.   | 10.12 Hrs.   | 10.96 Hrs.   |

| 200          | 8.10 Mins.  | 15.78 Mins.   | 7.32 Hrs.    | 10.00 Hrs.   |

| 500          | 6.93 Mins.  | 12.77 Mins.   | 5.84 Hrs.    | 10.11 Hrs.   |

| 1000         | 6.70 Mins.  | 12.62 Mins.   | 5.94 Hrs.    | 10.13 Hrs.   |

Table 1.1 Simulation time with EMU for different time steps.

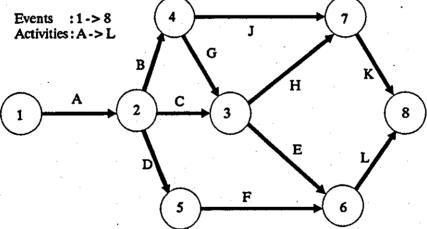

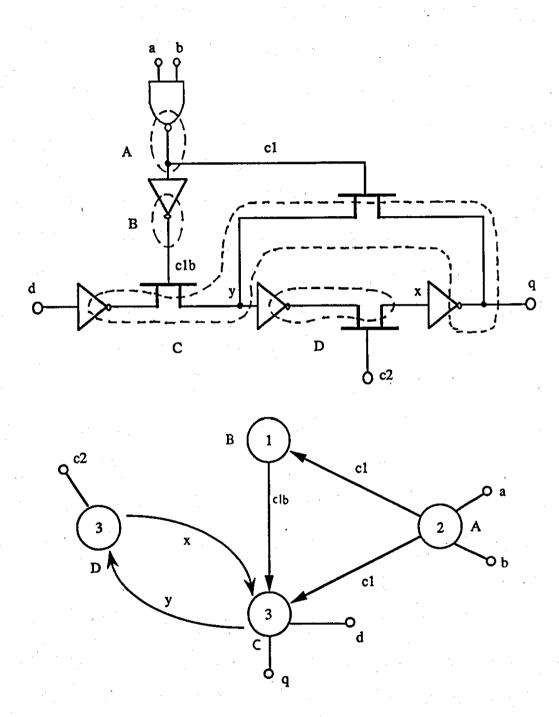

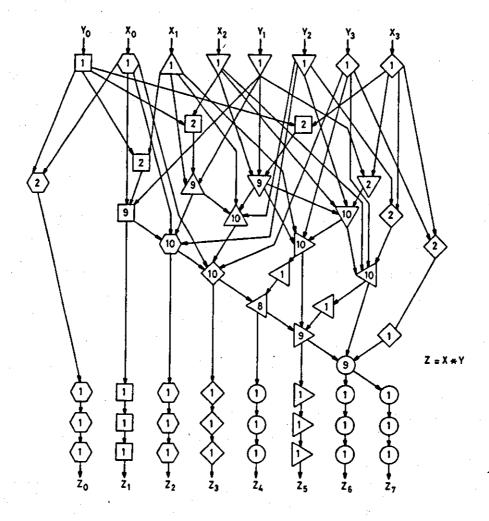

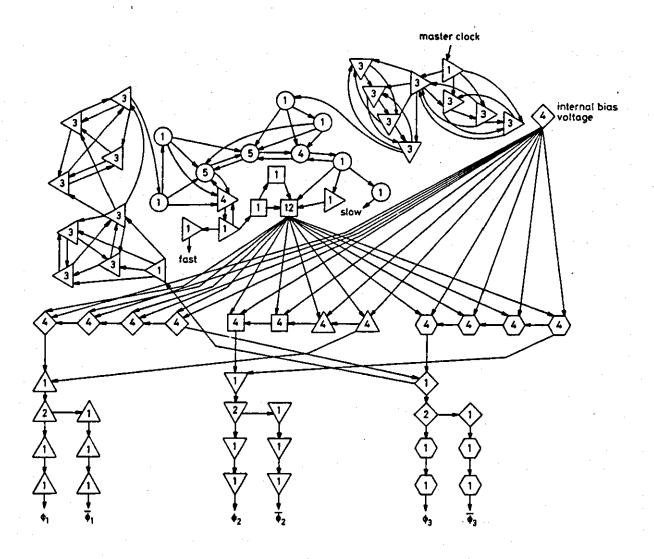

Further improvements in simulation time can be achieved by exploiting the inherent parallelism of a circuit and then running the simulation on a multiprocessor. CEMU [24] is a step in that direction. In CEMU the circuit under investigation is partitioned into a number of regions so that each region can be simulated independent of each other. Each such region which we shall call simulation modules, is composed of a number of voltage controlled current sources (e.g. a transistor) connected together to a capacitive node. The partitioned circuit can then be run on a multiprocessor by assigning each region or module to each of the processors. However, the performance of the multiprocessor implementation of the timing simulation is heavily dependent on the quality of region or module assignment onto the multiprocessor. An optimal assignment or scheduling guarantees higher throughput. However, the process of optimal scheduling or assignment is itself a difficult combinatorial optimisation problem for which no polynomial time optimal algorithm is known to exist [26]. In this dissertation the main theme will be the study of heuristic parallel multiprocessor scheduling algorithms in the context of VLSI timing simulation.

## 1.3 Multiprocessor Task Scheduling

The multiprocessor task scheduling problem can be defined as the process of allocating task modules to processors. The goal is to minimise the

parallel execution time. The parallel execution time depends on processor utilisation and on the overhead of interprocessor communication.

List scheduling algorithms [27] have been found to be quite successful for general task scheduling problems when communication overhead is ignored. They have linear time characteristics with a constant performance bound of 2 [28], meaning that the maximum execution time for a particular schedule generated by the list scheduling algorithm is twice that of the optimal parallel execution time.

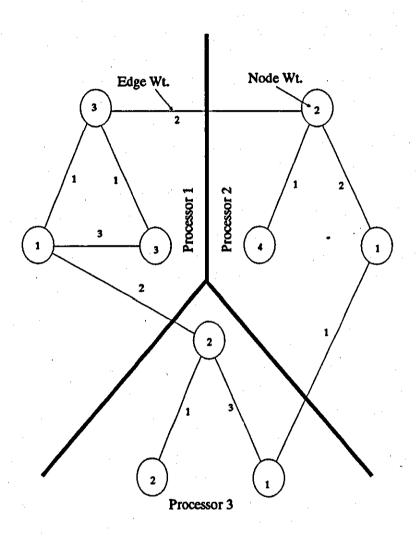

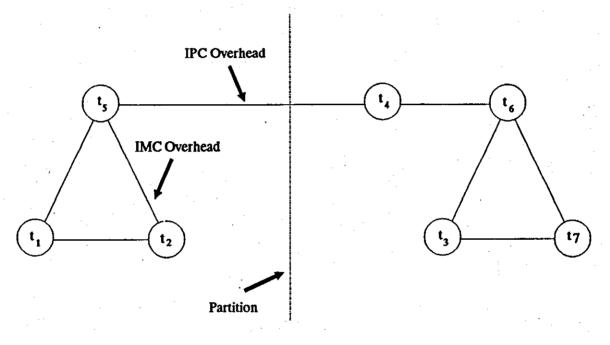

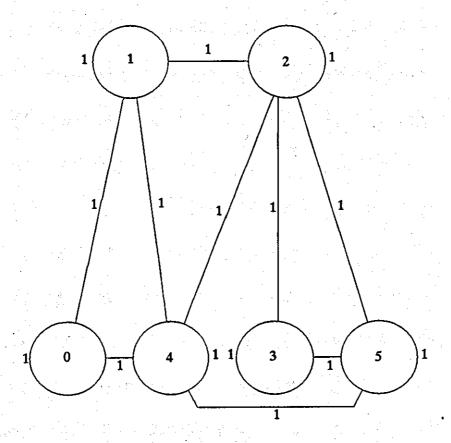

Unfortunately, the scheduling problems become more difficult when communication overhead with arbitrary data sizes are considered. Even quite simple instances of the scheduling problems are often intractable. For example, let us consider the Computation Flow Graph (CFG) as illustrated in Fig.1.7. We are given a set of seven task modules with the direction of flow of information highlighted by the edges of the graph. Furthermore, the execution time needed by each task module is fixed and known in advance. Three processors are available. Scheduling the task modules onto the processors to minimise the time needed to complete all the task modules is an NP-Hard problem, meaning that it is unlikely that a polynomial time algorithm exits that can always find an optimal schedule, given an arbitrary CFG. Therefore, in general, we must resort to a approximate scheduling algorithm that gives a near optimal schedule in acceptable polynomial time.

The term task allocation is often used to describe task scheduling problems. These are almost synonymous terms with the former being posed in terms of resource allocation (from the resources' i.e. processors, memory etc. view point) and the latter from the consumer's view point. Task assignment is also used as an alternate term for task scheduling.

### 1.4 Outline of the Dissertation

The rest of the disseration is organised as follows:

Chapter 2 starts with a proof of the NP-Completeness of the multiprocessor task scheduling problem. An overview of the scheduling problems and different approaches taken in solving these problems are then presented. Section 2.4 briefly describes the available heuristic techniques and finally a summary of the contributions made by this dissertation are presented.

Chapter 3 describes The Graph Model, used to represent the concurrent VLSI simulation system and it's scheduling onto a multiprocessor. It also presents a cost assignment for the task system considered — communication and computation costs are discussed in this respect. A generic multprocessor system is considered. This chapter also contains detailed data structure and various primitives used throughout.

Chapter 4 describes the modified Kernighan-Lin graph partitioning algorithm and it's parallel implementation. A hierarchical partitioning strategy is adopted. Various aspects of the it's implementation are also discussed.

The Simulated Annealing (SA) algorithm is introduced in chapter 5. An implementation suitable for graph partitioning is used. Two different temperature schedules are used and their performances are compared.

Chapter 6 starts with a review of parallel SA algorithms in existence and describes the problems relating to their implementation. The *Concurrent Simulated Annealing* (CSA) algorithm is proposed here and some implementations are suggested. Simulation results are also presented and an overall performance comparison is made.

Chapter 7 wraps up with some general discussion and concluding remarks. Some suggestions for future work are also made.

Appendix A contains the data and statistics for the various data flow graphs used throughout.

Appendix B contains proof of a corollary used in chapter 5.

### References:

- 1. Gurd, J.R., Kirkham, C.C. and Watson, I., The Manchester Proto-type Data Flow Computer, Comm. of ACM, 28(1), Jan 1985.

- 2. Flynn, M.J., Very High-Speed Computing Systems, Proc. IEEE, Vol. 54. No. 12, Dec 1966, pp. 1901-1909.

- 3. Kuck, D.J., The Structure of Computers and Computations, John Wiley, 1978.

- 4. Händler, W., The Impact of Classification Schemes on Computer Architecture, Proc. 1977 Intl. Conf. Parallel Processing, IEEE, August 1977, pp. 7-15.

- Quinn, M.J., Designing Efficient Algorithms for Parallel Processing, McGraw-Hill Book Co., 1987.

- 6. Hwang, K. and Briggs, F.A., Computer Architecture and Parallel Processing, McGraw-Hill Book Co., 1985.

- 7. Agerwala, T., Communication, Computation and Computer architecture, in Proc. Intl. Comm. Conf., June 1977, pp. 209-215.

- 8. Perry, T.S., Intel's Secret is Out, IEEE Spectrum, Vol. 26, No. 4, April 1989, pp. 22-28.

- 9. David, M.E. and Gwyn, C.W., CAD Systems for IC Design, IEEE Trans. CAD, Vol. CAD-1, No. 1, Jan 1982, pp. 2-12.

- Wallich, P., The One-Month Chip Design, IEEE Spectrum, Vol. 21,

No. 9, Sept. 1984, pp. 30-34.

- Kravitz, S.A., Multiprocessor Based Placement by Simulated Annealing, M.Sc. Thesis, Carnegie-Mellon Univ., USA, 1986.

- 12. Ambler, A.P., An Overview of CAD Acceleration, IEE Colloquium: Hardware Accelerators for VLSI CAD A Tutorial,' Sept. 1988.

- Schmid, R. and Batinger, U., A Hardware Accelerator to Support Effective Chip Floorplanning, Intl Workshop on Hardware Accelerators, Oxford, England, 1987.

- Bayer, J., Application of a Pipelined Processor for Fast and Economic Design Rule Checking and Circuit Routing, Intl. Workshop on Hardware Accelerators, Oxford, England, 1987.

- 15. Sieler, S.D., A Hardware Assisted Methodology for VLSI Design Rule Checking, Ph.D. Thesis, MIT, USA, 1985.

- Blank, T., A Survey of Hardware Accelerators Used in Computer Aided Design, IEEE Design & Test, Vol. 1, No. 3, Aug 1984.

- Lewis, D.L., Hardware Accelerators for Timing Simulation of VLSI

Digital Circuits, IEEE Trans. CAD, Vol. CAD-7, No. 11, Nov 1986,

pp. 1134-1149.

- 18. Deutsch, J.T. and Newton, A.R., A Multiprocessor Implementation of Relaxation Based Electrical Circuit Simulation, ACM-IEEE Design Automation Conf., USA, June 1984.

- Coleman, N. and Ambler, A.P., A Multiprocessor for General VLSI design Acceleration, Intl. Workshop on Hardware Accelerators, Oxford, England, 1987.

- Vladimirescu, A. and Lui, S., The Simulation of MOS Integrated Circuits Under SPICE2, Elec. Research Lab., Univ. of Calif. Berkley, USA, ERL Memo M80/7, 1980.

- 21. Kleckner, J.E., Saleh, R.A. and Newton, A.R., Electrical Consistency in Schematic Simulation, in Proc. IEEE Conf. on Computer Aided Design, Nov 1984.

- 22. Terman, C.J., Simulation Tools for Digital LSI Design, Lab. for Computer Science, MIT, USA, Tech. Rept. MIT/LCS/304.

- 23. Bryant, R.A., A Switch-Level Model and Simulation for MOS Digital Systems, Calif. Inst. of Tech., USA, tech. Rept. 5065:TR:93, 1983.

- Ackland, B.D., Ahuja, S.R., Linstrom, T.L. and Romero, D.J., CEMU

— A Concurrent Timing Simulator, in Proc. IEEE Intl. Conf. Computer Aided Design, 1985.

- Chawla, B.R., Gummel, H.K. and Kozak, P., MOTIS A MOS Timing Simulator, IEEE Trans. Circuits & Syst., Vol. 22, No. 12, Dec 1975, pp. 751-756.

- Garey, M.R. and Johnson, D.S., Computers and Intractability: A

Guide to the Theory Of NP-Completeness, Freeman, San Fransisco,

USA, 1979.

- Helmbold, D.P., Parallel Algorithms for Scheduling and Related Problems, Ph.D. Thesis, Stanford Univ., USA, 1987.

- Graham, R.L., Bounds on Multiprocessor Timing Anomalies, SIAM J. of App. Math., 17(2), March 1969.

## CHAPTER 2

# The Task Scheduling Problem

Scheduling problems are combinatorial optimisation problems. Each instance consists of task modules to be scheduled on a certain number of processors. The solution is a *schedule* indicating when and where each task module is to be executed. A schedule of task modules to processors can formally be described by a function from the set of task modules to the set of processors,  $f: T \to n$ . In a system of T task modules and n processors there are  $n^T$  possible schedules of tasks to processors. The difficulty, is therefore, to pick out an optimal schedule from the exponentially many different possibilities. A performance criterion in the form of a function is thus used to compare the  $n^T$  possible schedules and to associate a cost with each schedule. An optimal schedule is one which minimises the cost function.

## 2.1 Complexity of Task Scheduling Algorithms

The complexity of an algorithm can be given by a function  $f: \mathbb{N} \to \mathbb{N}$ (where IN is the set of all natural numbers), which characterises the execution time of the algorithm in terms of the size of its input. Algorithmic characterisation of  $f(\cdot)$  (i.e., constant, logarithmic, linear, polynomial, exponential etc.) are used to identify the complexity of the associated algorithm. Let, P be the set of all problems  $\pi$  for which there exists a deterministic polynomial time algorithm to solve the problem  $\pi$ . Likewise, let NP be the set of all problems which have non-deterministic polynomial time algorithmic solutions. The term, NP-Complete is used to describe problems that are the hardest ones in NP. A problem  $\pi$  is said to be NP-Complete if i)  $\pi \in NP$ , and furthermore ii)  $\pi \in P$  implying P = NP. Since, it is widely believed that  $P \neq NP$ , a proof that a problem  $\pi$  is NP-Complete is equivalent to showing that  $\pi$  can not be solved efficiently and that probably the best deterministic algorithm to solve  $\pi$  is at least of exponential time complexity. NP-Complete problems are posed in the form of a decision problem and the corresponding optimisation problem is know to be in the class of NP-Hard problems.

Vairavan and DeMillo [1] using a synchronous parallel computation model showed that any algorithm designed to generate an optimal n-processor (n fixed) schedule of a loop free computer program, when such a schedule exists, would demand exponential time. We here also present a proof of the NP-Completeness of the multiprocessor task scheduling problem using the reducibility property of NP-Complete problems. This is a two part proof, where in Part I we show that the problem is in NP. In the second part, the scheduling problem is shown to be polynomially transformable to a quadratic assignment problem which is NP-Complete.

Theorem (2.1). The above mentioned multiprocessor task scheduling problem is NP-Complete.

#### Proof:

#### Part I:

We consider a non-deterministic Turing machine (NDTM). The NDTM would make a first guess at picking a processing element (PE)

out of n such PEs and assign it to the first node of the task graph. In the next step another PE would be selected for allocation. This process would continue until all the nodes of the task graph are allocated. A guess should be such that the communication overhead of the resulting schedule is minimised and computational loads are evenly balanced among the PEs. This would take O(n) time on the NDTM, which proves that the problem is in NP.

#### Part II:

We define an assignment matrix X[T,n] with components,

$$x_{iq} = \begin{cases} 1 & ; & \text{if task } i \text{ is assigned to PE } q, \\ 0 & ; & \text{Otherwise.} \end{cases}$$

(2.1)

Then.

$$\sum_{q=1}^{n} x_{iq} = 1 \quad ; \qquad 1 \le i \le T, \tag{2.2}$$

since each task must be assigned to exactly one processor. Also, for cases  $T \ge n$ , each processor can have more than one task assigned to it.

Therefore,

$$\sum_{i=1}^{T} x_{iq} \ge 0 \quad ; \qquad 1 \le q \le n. \tag{2.3}$$

We now define,

$e_{ij}$  = Amount of data transfer from node i to node j of the task graph.  $w_{iq}$  = computational load of node i of the task graph on pressor q.

It can be easily seen from the above that the total communication cost may now be expressed as,

$$C_c = \sum_{\substack{i,j=1\\i\neq i}}^{T} \sum_{\substack{q,r=1\\q\neq r}}^{n} e_{ij} x_{iq} x_{jr}, \qquad (2.4)$$

and the total execution cost,

$$C_e = \max_{q=1\cdots n} \left\{ \sum_{i=1}^T w_{iq} x_{iq} \right\}. \tag{2.5}$$

Therefore, the scheduling problem is transformed to the following optimisation problem,

$$minimise\{\alpha|C_c| + \beta|C_e|\}$$

(2.6)

subject to,

$$\sum_{q=1}^{n} x_{iq} = 1 \quad ; \qquad 1 \le i \le T, \tag{2.7}$$

and

$$\sum_{i=1}^{T} x_{iq} \ge 0 \quad ; \qquad 1 \le q \le n. \tag{2.8}$$

This is equivalent to a quadratic assignment problem. Since, the quadratic assignment problem is NP-Complete[2,3], the present multiprocessor task scheduling problem is also NP-Complete.

Q.E.D.

#### 2.1.1 Parallel Algorithms

The major driving force behind the research and development of parallel computers is to speed-up the solution process of difficult algorithmic problems. But, surely an undecidable problem can not be solved by a parallel computer no matter how large or complex it is. The reason being that every parallel computer can be simulated by a sequential processor, running around and doing every processor's work in an appropriate order. In this sense, the Church/Turing thesis also applies to parallel models of computation too: the class of solvable problems is insensitive even to the addition of parallelism.

But, can parallelism turn intractable problems into tractable ones? In other words, is it possible to have a polynomial time algorithm for a problem having exponential time sequential solution? To answer this, we recall that all problems in NP have reasonable (polynomial) solutions that are non-deterministic. If a correct guess is made out of a large possibilities, it would lead to a positive solution. Now, if we have an unlimited number of processors, we can employ each processor to explore each possibility. If one of the processors finds a correct solution then indeed a polynomial time

parallel solution exists. On the other hand, if none of the processors find a solution then the problem can be thought of as truly intractable.

It is, therefore, seen that reasonable parallel solutions for intractable problems are theoretically feasible. But, in reality many practical problems exist. NP-Complete problems are not known to be intractable — they are merely conjectured to be so. Thus, the possibility of simulating NP-Complete problems in parallel in polynomial time does not imply that parallelism can get rid of a problem of its inherent intractibility, since we do not know whether or not NP-Complete problems are actually intractable. Furthermore, the number of processors required to solve an NP-Complete problem in reasonable time is itself exponential, requiring billions or trillions of processors in some cases. Even, if it is possible to have that many processors in a multiprocessor system with the advent of technology, the communication overhead would be too large to cope with. The algorithm to control the communication links and channels would also be of exponential complexity. With all this overhead, a super-polynomial number of processors would require a super-polynomial amount of real time to carry out even a polynomial number of instructions. In practical terms, therefore, it is not possible to have a reasonable parallel counterpart for an unreasonable (exponential) sequential algorithmic solution.

Nonetheless, a practical multiprocessor system, both coarse and fine grained, are of immense importance for many real world applications. In many cases an almost linear speed-up is possible. Again, for the solution of difficult NP-Complete problems, a heuristic algorithm can be chosen over an exact algorithm, which when properly implemented on a parallel machine, would give reasonably good solution within a time of practical value.

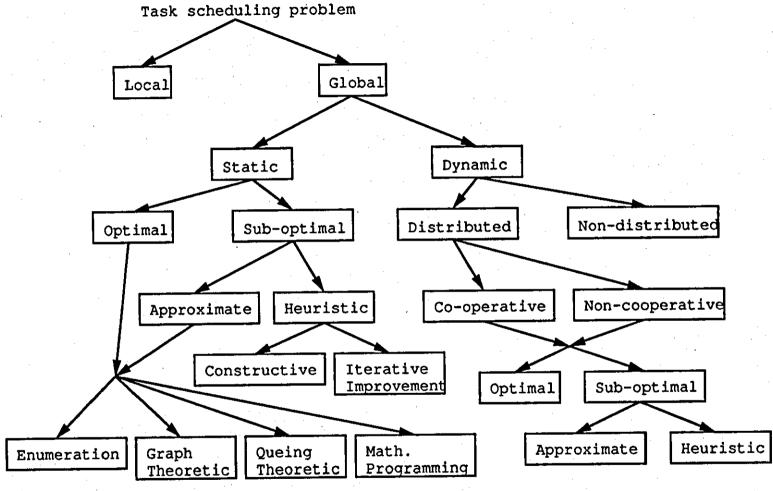

## 2.2 Classification of Task Scheduling Algorithms

The multiprocessor task scheduling problem bears a close resemblance to the classical job sequencing problems as encountered in production management. These types of problems have been described a number of times and in a number of different ways in the literature [1,4-6]. In this classification, however, we take a slightly different view and concentrate on the mechanism or policy of efficient and effective management of the access to and on the

Adaptive vs. Non-adaptive Load Balancing vs. Minimum Interprocessor Communication (IMC) Policy Mechanism vs. Bidding

Fig. 2.1 Classification of different task scheduling approaches.

use of various resources by its various consumers. Obviously, in this scenario, the processors form part of the resources and the program tasks constitute the consumers waiting to be executed on the processors.

In this short classification, the goal here is to familiarise with a commonly accepted set of terms and also to present a means to compare past works in the area of multiprocessor task (or distributed process) scheduling in a qualitative way. A hierarchical classification proceeds first, to be followed by a flat classification scheme which is felt necessary as some choices of characteristics may be made independent of previous design choices and thus require different attention. The classification tree is presented in Fig. 2.1. This classification however does not take into consideration the different possible strategies for the parallelisation of the scheduling algorithms itself. In the following sections we present some of the selected and pertinent categories of the classification tree. The selected classification presented here is based on Casavant and Kuhl's taxonomy [7] which can be consulted for detailed study.

#### 2.2.1 Static vs. Dynamic Scheduling

In the case of static scheduling also known as deterministic scheduling [4], the task modules are preassigned to the processors before the execution actually begins. Hence, each executable task in a system has a static assignment to a particular processor, and each time that task is submitted for execution, it is assigned to that same processor. Static scheduling can be successful only when a priori knowledge of the execution behaviour of the tasks is available. This includes the input-output profile as well as the computational load of each task. Static scheduling is attractive because it eliminates scheduling overhead entirely at run time. Further, there is a greater opportunity to optimise the interprocessor communication. The disadvantage is that the execution behaviour estimate may be inaccurate leading to inefficient schedule and that also static schedule is tied to a particular hardware configuration and a new schedule is thus necessary every time there is a change in hardware architecture or topology.

On the other hand, in the case of dynamic scheduling the assignment of tasks to processors is left till the run time. The assignment procedure takes place dynamically along with the actual processing of the tasks. This leads to a heavy run time scheduling problem. Nevertheless, this approach is favoured when execution behaviour of the tasks is not available or difficult to ascertain. Dynamic scheduling can again be grouped into distributed and non-distributed (or centralised) scheduling. As the names suggest, in the case of non-distributed scheduling the task of global dynamic scheduling should reside in a single processor and in the other case it is physically distributed among the processors.

#### 2.2.2 Optimal vs. Sub-optimal Scheduling

In some cases of multiprocessor task scheduling, where all the information regarding the state of the system as well as the execution behaviour of the tasks are known, an *optimal* assignment is feasible [6, 8-9]. These optimal assignments are based on some simple criterion functions and results of their appropriate optimisations. Examples include minimising total process completion time, maximising utilisation of resources in the system, or maximising system throughput. In the event that a more robust and accurate criterion function is used resulting the solution computationally infeasible, *sub-optimal* solutions may be more desired [10-11]. As shown in section 2.5 an optimal solution for the multiprocessor task scheduling problem is very difficult to achieve and as such a sub-optimal solution is more realistic and desirable.

## 2.2.3 Approximate vs. Heuristic Solutions

In the approximate method, use of the same computational model for the algorithm is used. However, instead of searching the whole solution space which is deemed very time expensive, search is stopped when a good solution is found. This is taken as the *sub-optimal approximate* solution. The difficulty, however, arises in the determination of a good solution. In the cases where a metric is available for evaluating a solution, this technique can be used to decrease the time taken to find an acceptable solution.

Heuristic methods are favoured for the solution of many combinatorial optimisation problems due to its ability to provide near-optimal solutions

in reasonable time. Different heuristic scheduling algorithms have been proposed [5, 10-14]. This method is best suited when a good and realistic assumption about a priori knowledge concerning the execution behaviour of the tasks can be made. Heuristic schedules often use an indirect rather than direct approach to monitor the system performance and this indirect approach is much simpler to implement and calculate. For example, clustering of tasks [5] can be employed so that heavily communicating tasks are grouped together and assigned to the same processor and also physically separating the tasks which would benefit from parallelism. This directly decreases the overhead involved in passing information between processors while reducing the interference among tasks which may run without synchronisation with one another.

#### 2.2.4 Load Balancing

Load balancing has received a great deal of attention [14-17]. This is more of a design choice than a separate algorithmic approach and as such placed under the flat classification in the classification tree of Fig. 2.1. This brings fairness to the hardware resource utilisation. The basic idea is to attempt to balance (in some sense) the load on all processors in such a way as to allow progress by all tasks on all processing elements to proceed at approximately the same rate. This approach is best suited for homogeneous multiprocessor system since this allows all processors to know a great deal about the structure of the other processors.

Incorporation of load balancing criterion in the cost function of a heuristic algorithm is very important and brings higher processor utilisation. A heuristic algorithm which minimises the interprocessor communication in a schedule totally ignoring load balancing, would assign all the tasks to a single processor as the communication overhead between tasks assigned to the same processor is considered negligibly small. As a result the schedule though an optimal one for the criterion considered would be taken as highly inefficient.

# 2.3 Optimal and Sub-optimal Approximate Techniques

For both optimal and sub-optimal approximate solutions of static multiprocessor scheduling there are four basic categories of algorithms that can be used. These are described in the following sub-sections:

#### 2.3.1 Solution Space Enumeration and Search

A complete enumeration and search for the optimal solution can be very time expensive and of exponential time complexity. However, the problem can be transformed into a simpler one and state-space search can then be used to arrive at an optimal or acceptable sub-optimal solution. Shen and Tsai [9] restated the problem as weak homomorphic graph matching problem and used the A\* algorithm after collecting relevant heuristic informations for an optimal solution.

#### 2.3.2 Graph Theoretic

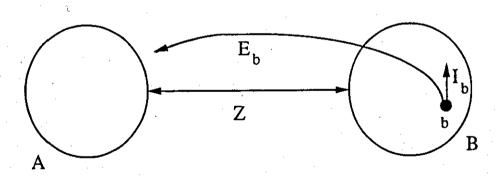

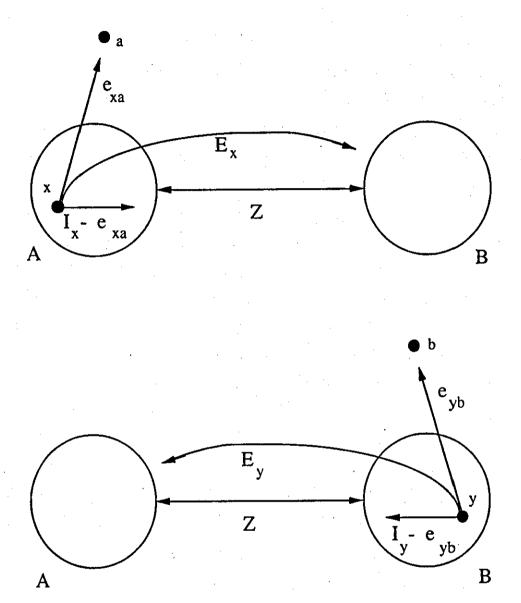

In graph theoretic approach the scheduling problem is modelled as a network with undirected edges and an attempt is then made to find the maximum flow across a cut, resulting in an optimal solution. Stone [18] used Ford-Fulkerson's Max Flow Min Cut [19] algorithm to find an optimal schedule. However, his algorithm is applicable for 2-processor systems only. Stone and Bokhari [20] used this idea for n-processor homo/heterogeneous systems. However, this works only when the intertask communication pattern is constrained to be tree structured. Lo [10] also proposed a three stage algorithm composed of graph theoretic and heuristic method for a near optimal n-processor schedule. The two main drawbacks of graph theoretic approach is its lack of mechanism to accommodate load balancing and to incorporate various resource constraints into the model.

## 2.3.3 Mathematical Programming

Various mathematical programming techniques like branch-and-bound, backtracking, 0-1 integer programming etc. can be successfully applied to solve multiprocessor scheduling problems. Chu [21] used 0-1 integer

programming technique for optimal file allocation in a multiprocessor system which bears close resemblance to our problem in hand. Ma et. al [6] used branch-and-bound method to minimise the interprocessor communication and also for balanced processor utilisation. Kasahara and Narita [22] used a combination of branch-and-bound and critical path methods. Though mathematical programming techniques are flexible enough to incorporate many system constraints, they are still of exponential time complexity. These techniques can be used in some cases, but their generalisation is reduced by their demand for large time and space.

#### 2.3.4 Queing Theoretic

Queing theory can also be applied for the solution of multiprocessor scheduling problems [15, 19]. Klinrock and Nilsson [23] considerd a M/G/1 queing system model. Their cost function is based on task waiting time and their required service time. The problem is posed as an optimisation problem and mathematical programming technique is used to optimise the total cost. However, the solution is found to be sub-optimal. Generalisation for a n-processor model is also found difficult.

## 2.4 Heuristic Technique

Heuristic algorithms by their very nature can adopt many different possible approaches. However, for the multiprocessor task scheduling and also for many other similar combinatorial optimisation problems a simple classification can be attempted. Two different basic approaches can be thought of. These are:

- 1. Constructive Method

- 2. Iterative Improvement Method.

#### 2.4.1 Constructive Method

The constructive scheduling algorithm begins with the assignment of one or a few seed task modules and then gradually builds up the total schedule by assigning a new free task module in succession each to a processor, always taking the best momentary decision for any particular assignment. The

approach is however greedy in nature as the decision at each instant is based on the current effect and not on the global effect. As a result the resulting solution often turns out to be rather inferior.

Still, there are many combinatorial optimisation problems where greedy constructive algorithms can be used to produce good solutions with high probability. For many such problems an exhaustive search is far too impractical and in the absence of other fast heuristic algorithms, greedy constructive algorithms are the only real and wise choice. One classical example is for the solution of Travelling Salesman Problem (TSP), where greedy constructive algorithms have been found very effective. For the multiprocessor task scheduling problem a good use of the constructive algorithm can be made whereby heavily connected task modules are grouped together and assigned to the same processor. This would help to minimise the communication cost component of the objective function.

#### 2.4.2 Iterative Improvement Method

The iterative improvement method is of special interest in this dissertation. As mentioned earlier, the task scheduling problem falls into the class of combinatorial optimisation problems involving large solution space. Though, theoretically it is possible to find the best solution by generating and evaluating all possible solutions, in practical terms it turns out to be an impossible task due to the exponential growth of complete enumeration algorithms.

Heuristic algorithms provide much promise to find a good solution in reasonable time. Due to the greedy nature, the constructive heuristic algorithms often fail to keep up to this promise. The iterative improvement method is a viable alternative which can be thought of made up of two phases.

For the solution of task scheduling problem, an initial schedule is generated in the first phase either by a constructive algorithm or by random method. This initial schedule is then iteratively improved in the second phase. A new schedule is generated at each step by introducing some

Schedule (Configuration)

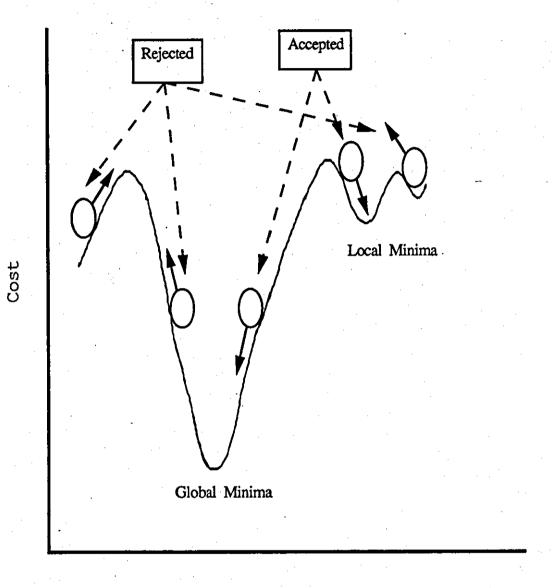

Fig. 2.2 The local minima traps of a cost function.

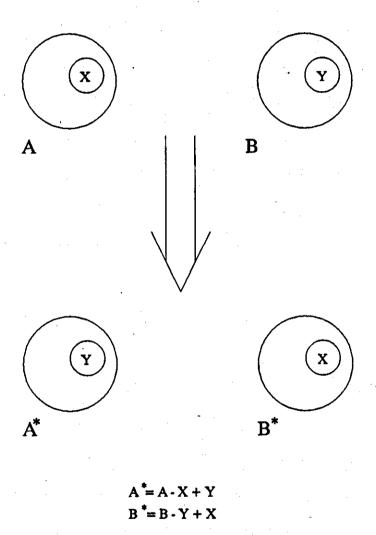

modifications to the present schedule (configuration). The modifications that can be made are:

- 1. Changing the assignment of a task module to a new processor.

- 2. Swapping the assignments of two task modules.

A cost (objective) function is defined to guide the heuristic search in a direction that will improve the schedule. If the cost of a new schedule is lower than that of the previous one, the new one is accepted and further modifications are inflicted upon it. Otherwise, if the cost is increased in the new schedule, it is rejected and the previous one is retained for further modifications. The iterative improvement process is continued until no further improvement can be obtained or any other predefined stopping criterion is satisfied.

#### 2.5 Local Minima and Optimal Solution

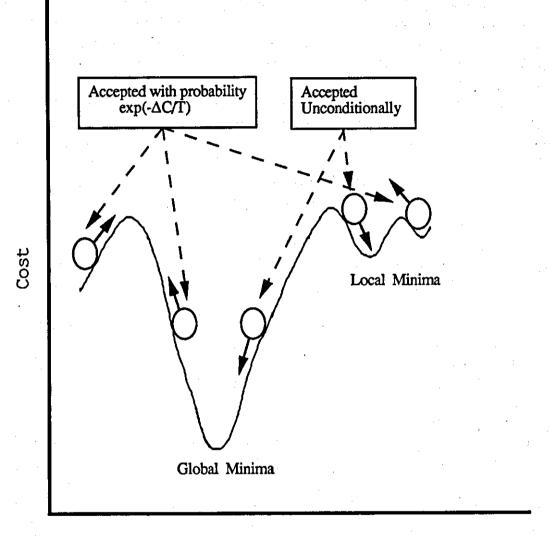

Most heuristic algorithms search for a solution only in the direction that improve the cost functions. One inherent drawback of this type of heuristic search is that it can be easily trapped into a local minimia of the cost function. The example presented in Fig. 2.2 is used to demonstrate this problem.

The curve in Fig. 2.2 may be considered as the cost function of an iterative improvement process and the circles can be used to indicate the costs of certain schedules. Since a new schedule is generated by introducing small modifications to the present schedule, its corresponding location on the curve is most likely to be somewhere near that of the present schedule. The traditional iterative improvement algorithm only accepts schedules that have reduced the cost. This criterion of schedule acceptance implies that the process can only go downhill into a local minima and any uphill movement is forbidden. Thus, the search process can not climb over the peak of the curve to reach the global minima.

Different alogorithmic solutions have so far been proposed [24–26] that gives a certain degree of hill climbing capability to the basic iterative improvement heuristics. This ensures a good near optimal solution for NP-Hard problems. As an illustration we here present a brief introduction of the

Schedule (Configuration)

Fig. 2.3 The hill climbing capability of simulated annealing algorithm.

Simulated Annealing [24] algorithm which is recently being successfully used for the solution of many difficult problems including network partitioning, VLSI cell placement, numerical problems using Monte-Carlo method as well as task scheduling problem. An analogy is made with the statistical mechanics which deals with the behaviour of systems with many degrees of freedom in thermal equilibrium at a finite temperature, to combinatorial optimisation which finds the minimum of a given function depending on many parameters. Simulated annealing brings minor but, vital modification to the traditional iterative improvement method. Instead of rejecting outright a new schedule (or configuration in general case) which results in an increase in the cost function  $(\Delta C)$ , the modified algorithm accepts this new configuration with a certain probability,

$$P_{(S_i)} = e^{(-\Delta C_{(S_i)})/t}, \tag{2.9}$$

where  $S_i$  represents a certain configuration at any instant i.

This conditional probability is dictated by the Maxwell-Boltzmann statistics of statistical physics. The parameter t, an analog of temperature in the physical process is a very important control parameter. This control parameter t, also known as temperature, is slowly reduced from an initial high value to a final very low value, where the solution is thought to be frozen (converged). A configuration has a high probability of being accepted at high temperature for the same cost increase. On the other hand, when the temperature is lowered, the probability of accepting a cost increasing configuration is smaller. This is equivalent to high hill climbing capability at the initial high temperature which is necessary to explore the overall solution space as much as possible without being trapped into a local minima. A slow reduction to a very low temperature over a good number of steps, ensures the configuration to settle down either to the global minima or somewhere very near to it. Fig. 2.3 shows the effect of simulated annealing algorithm.

#### 2.6 Contribution of this Dissertation

Static scheduling is favoured over dynamic scheduling. The main reason being that a detailed a priori knowledge about the execution and input-output behaviour of the VLSI simulation modules can be easily obtained.

Apart from this, in a typical VLSI design, the same circuit may have to be simulated a few times, each time with a new set of parameters to test all the possible eventualities. The cumulative scheduling overhead of dynamic scheduling would be much too high to render this almost impractical.

The item that is conspicuously absent from the classification tree of Fig. 2.1 is the distributed static scheduling algorithm and its siblings. A parallel or distributed static scheduling algorithm is much desired for practical applications. Apart from the obvious speed-up advantage, a parallel scheduling algorithm would definitely improve the machine utilisation of the available hardware system. In the VLSI design environment the same hardware can then be used for a variety of purposes including electrical/logic/timing simulation, floor plan design, wire routing, fault analysis etc.

Unfortunately not much research has been addressed to the problem of parallel static scheduling algorithm, although some research into parallel heuristic algorithm for the VLSI cell placement problem has been reported [27–29]. The VLSI cell placement problem bears a close similarity with the multiprocessor task scheduling algorithm. In this dissertation, the main theme is concentrated on the design and performance study of various parallel heuristic task scheduling algorithms. In addressing the general problem of parallel task scheduling this dissertation makes the following specific contributions:

- 1. The definition of a problem and system independent graph representation of the simulation task. With appropriate modification this can be used to represent parallel programs waiting to be executed on a multiprocessor.

- 2. The definition of a cost model for the task assignment. This model is general and flexible enough to represent a wide range of VLSI simulation problems and also different multiprocessor architecture.

- 3. The scheme for the incorporation of both execution and communication load on the target system.

- 4. Use of simple hierarchical partitioning method which can be easily implemented in a parallel environment. This, coupled with Kernighan-Lin's 2-way partitioning algorithm [25] has been found to be favourable for smaller multiprocessor system.

- 5. A parallel implementation of the simulated annealing heuristic with optimal number of parallel moves. this is thought to achieve faster convergence than other similar approach.

#### References:

- Vairavan, K. and DeMillo, R.A., On the Computational Complexity of Generalised Scheduling Problem, IEEE Trans. Comp., Vol. 2-25, No. 11, Nov, 1976, pp. 1067-1073.

- 2. Garey, M.R. and Johnson, D.S., Computers and Intractability: A Guide to the Theory of NP-Completeness, Freeman Press, 1979.

- 3. Sahni, S. and Gonzalez, T., P-Complete Approximation Problems, J. ACM, Vol. 23, March 1976, pp. 555-565.

- 4. Gonzalez, Deterministic Processor Scheduling, ACM Computing Surveys, Vol. 9, No. 3, Sept. 1979, pp. 173-204.

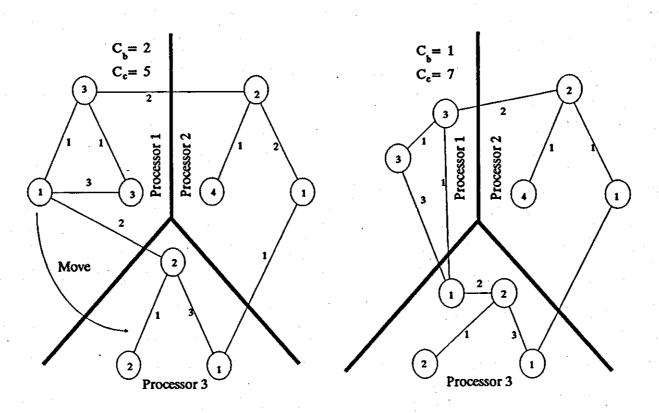

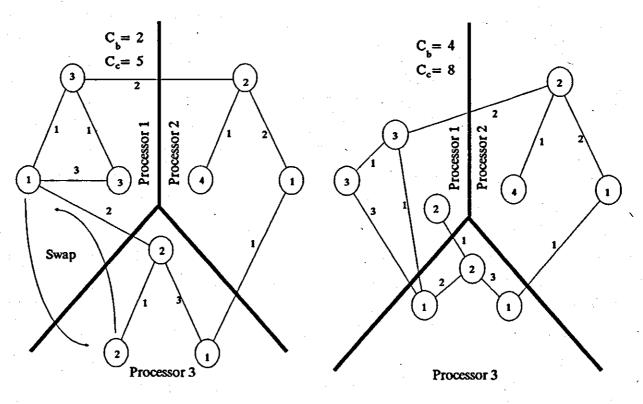

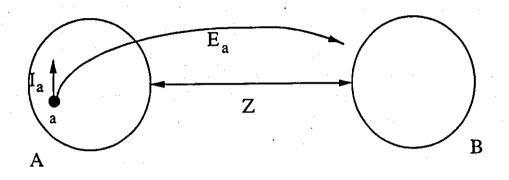

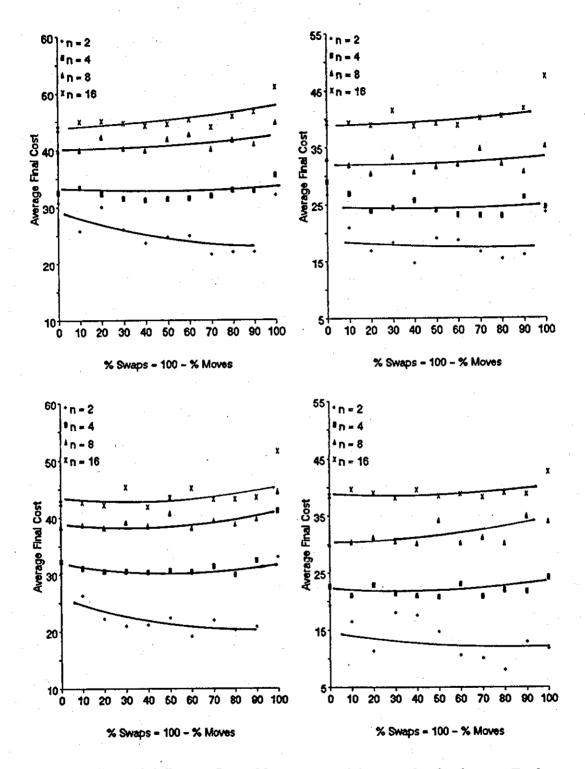

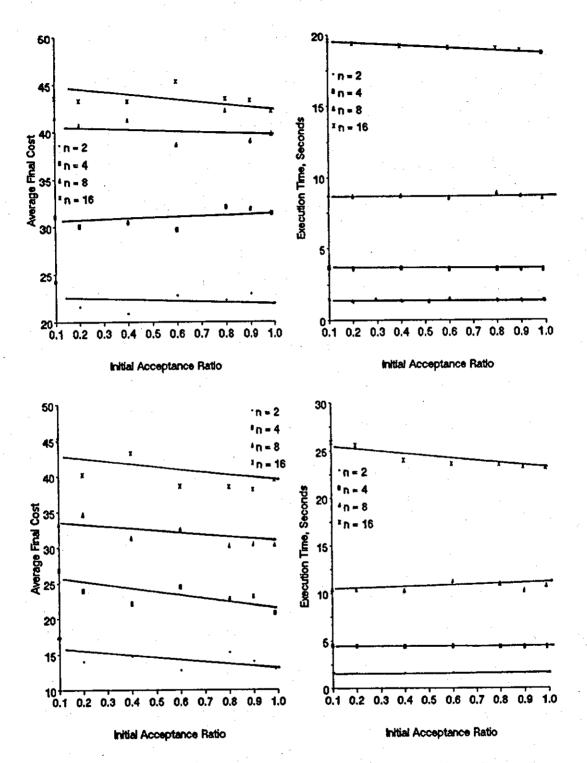

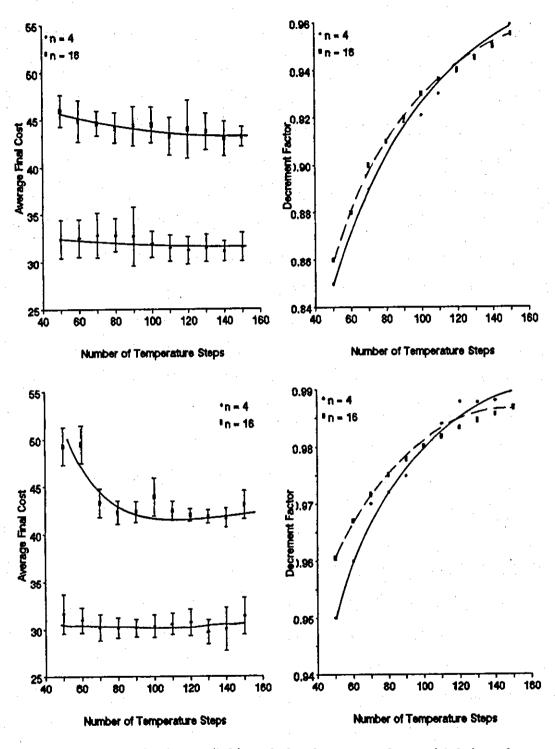

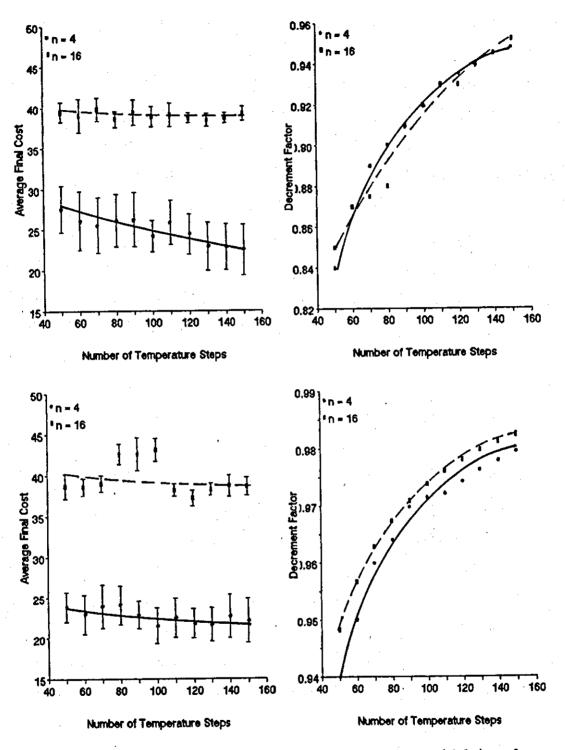

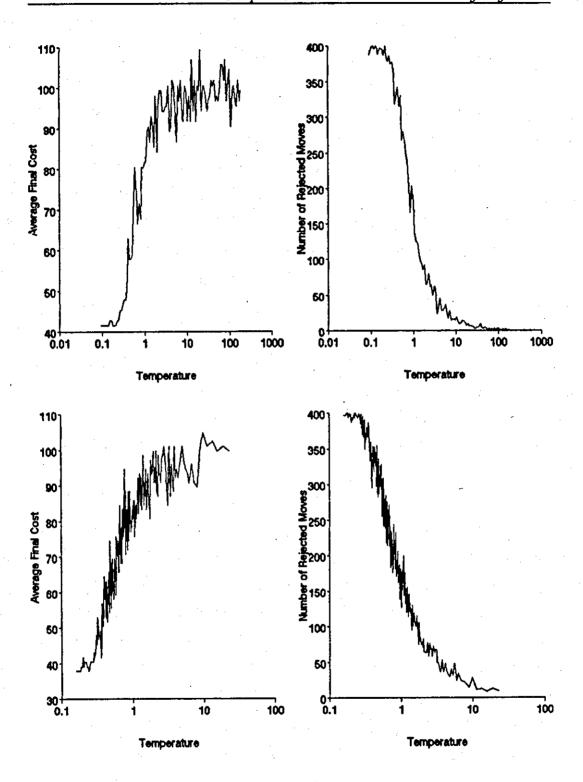

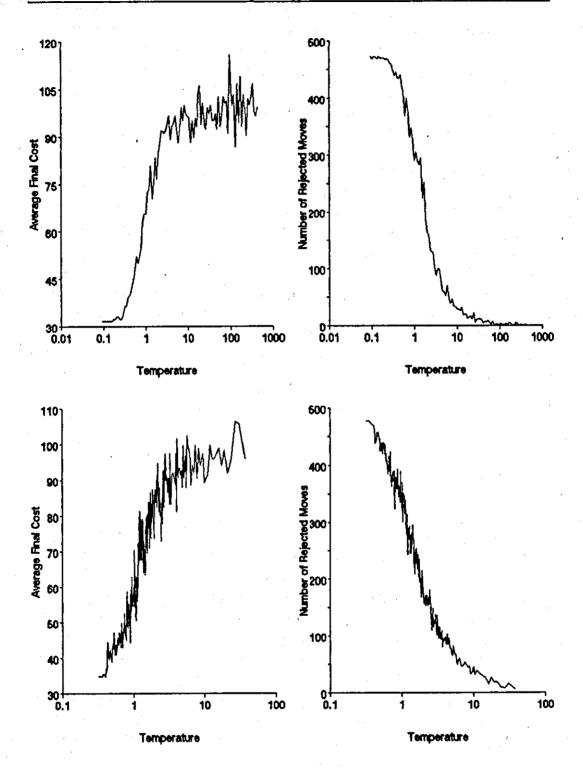

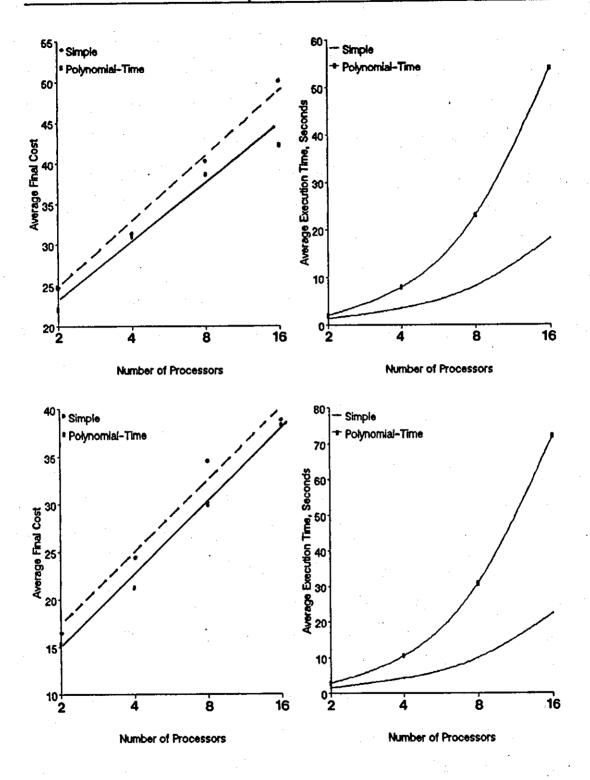

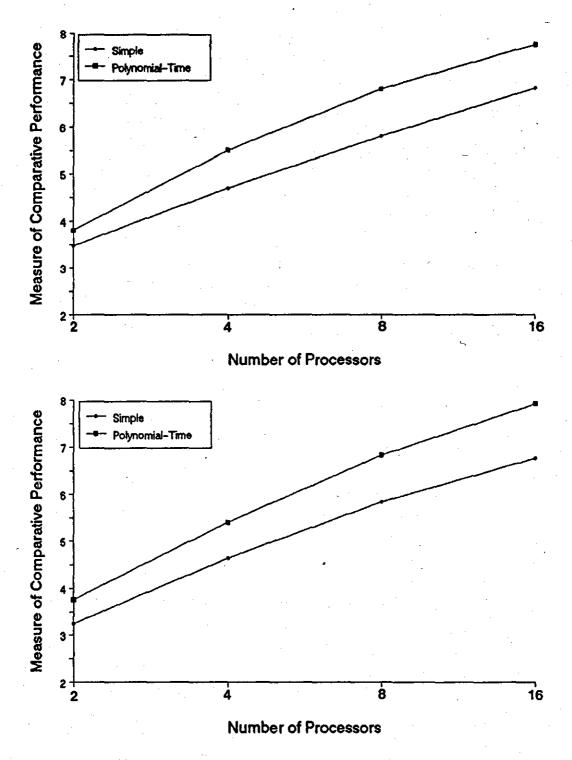

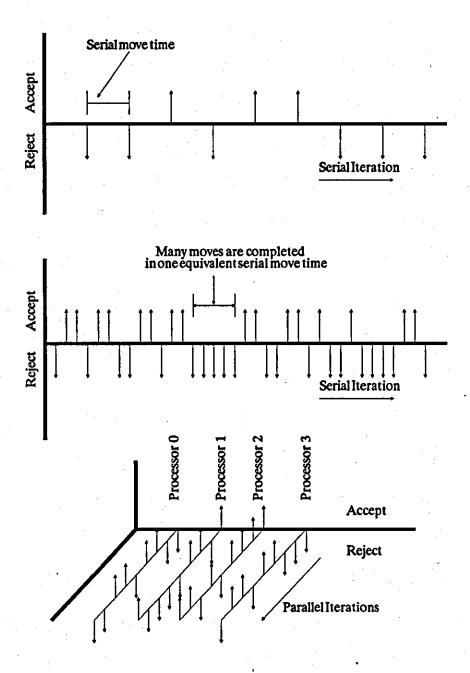

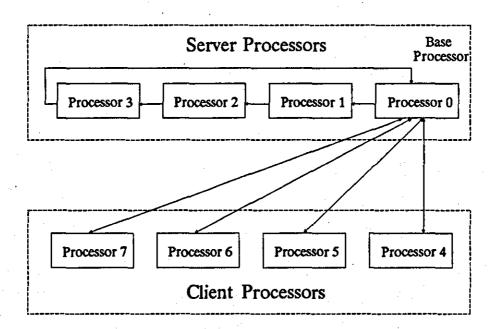

- Chu, W.W., Holloway, L.T., Lan, M. and Efe, K., Task Scheduling in Distributed Data Processing, Computer, Vol. 13, No. 11, Nov. 1980, pp. 57-67.