# SYSTEM ON FABRICS UTILISING DISTRIBUTED COMPUTING

by

Partheepan Kandaswamy

A Doctoral Thesis submitted in partial fulfilment of the requirements for the award of Doctor of Philosophy of Loughborough University

June 2018

© by Partheepan Kandaswamy

# To my parents Shanthi and Kandaswamy

#### **ABSTRACT**

The main vision of wearable computing is to make electronic systems an important part of everyday clothing in the future which will serve as intelligent personal assistants. Wearable devices have the potential to be wearable computers and not mere input/output devices for the human body. The present thesis focuses on introducing a new wearable computing paradigm, where the processing elements are closely coupled with the sensors that are distributed using Instruction Systolic Array (ISA) architecture.

The thesis describes a novel, multiple sensor, multiple processor system architecture prototype based on the Instruction Systolic Array paradigm for distributed computing on fabrics. The thesis introduces new programming model to implement the distributed computer on fabrics. The implementation of the concept has been validated using parallel algorithms.

A real-time shape sensing and reconstruction application has been implemented on this architecture and has demonstrated a physical design for a wearable system based on the ISA concept constructed from off-the-shelf microcontrollers and sensors. Results demonstrate that the real time application executes on the prototype ISA implementation thus confirming the viability of the proposed architecture for fabric-resident computing devices.

#### **ACKNOWLEDGEMENTS**

I would like to thank my supervisors Dr. James Flint and Dr. Vassilios Chouliaras for their continuous support, guidance, exceptional advice and shared knowledge throughout my PhD. I would also thank Dr. David Mulvaney for his shared knowledge during my PhD.

I would like to acknowledge Mr. Peter Godfrey from Wolfson School Electronic workshop for his support in building the prototype board.

I would like to thank Mr. Ben Clark for his shared knowledge and support throughout my research and also for his patience in reading my manuscript.

Finally, I would like to thank my parents for their encouragement, support and funding me throughout my University education.

## **CONTENTS**

| LIST O | F AB  | BREVIATIONS AND SYMBOLSviii                              |

|--------|-------|----------------------------------------------------------|

| LIST O | F FIC | GURESx                                                   |

| LIST O | F TA  | BLESxii                                                  |

| СНАРТ  | ER 1  | : INTRODUCTION1                                          |

| 1.1    | Are   | a of Research                                            |

| 1.1    | .1    | Distributed Computing                                    |

| 1.1    | .2    | Distributed Sensor Networks                              |

| 1.1    | .3    | Wearable Electronics                                     |

| 1.1    | .4    | Smart Fabrics6                                           |

| 1.2    | Res   | earch Aim9                                               |

| 1.3    | Obj   | ectives9                                                 |

| 1.4    | Nov   | vel contribution of the thesis                           |

| 1.5    | The   | esis Outline                                             |

| Refer  | ence  | s12                                                      |

| СНАРТ  | ER 2  | 2: A NOVEL PARALLEL DISTRIBUTED ARCHITECTURE14           |

| 2.1    | Intr  | oduction to Multiple sensors, Multiple Processor Systems |

| 2.1    | .1    | Comparison between the concepts                          |

| 2.2    | Cla   | ssifications of Parallel Computer Architectures          |

| 2.2    | .1    | Flynn's Taxonomy                                         |

| 2.2    | 2     | Duncan's classification                                  |

| 2.2    | 3     | VLSI processor arrays                                    |

| 2.2    | .4    | Conclusion                                               |

| 2.3    | Sys   | tolic Array25                                            |

| 2.3    | .1    | Features of systolic arrays                              |

| 2.3    | .2    | Types of systolic array structures                       |

| 2.4    | The   | Instruction Systolic Array                               |

| 2.4    | 1     | Dringiples of ISA                                        |

Contents

| 2.4             | 1.2   | ISA Architecture                                             | 33 |    |

|-----------------|-------|--------------------------------------------------------------|----|----|

| 2.4             | 4.3   | Programming and Execution of ISA                             | 35 |    |

| 2.4             | 1.4   | Applications of ISA                                          | 36 |    |

| 2.5             | Ad    | aptation to ISA                                              | 37 |    |

| 2.6             | Sys   | stola 1024                                                   | 37 |    |

| 2.7             | Co    | nclusion                                                     | 38 |    |

| Refe            | rence | es                                                           | 39 |    |

| CHAPT<br>FOR SI |       | 3: IMPLEMENTATION OF INSTRUCTION SYSTOLIC ARRA<br>T FABRICS  |    | 41 |

| 3.1             | A r   | novel architecture for on-fabric parallel processing         | 41 |    |

| 3.2             | Imj   | plementation of novel architecture                           | 44 |    |

| 3.2             | 2.1   | Candidates for bus systems                                   | 44 |    |

| 3.2             | 2.2   | Serial bus protocols                                         | 46 |    |

| 3.3             | De    | tails of the Inter-Integrated Circuit (I <sup>2</sup> C) Bus | 48 |    |

| 3.3             | 3.1   | Bus Signals                                                  | 50 |    |

| 3.4             | Pro   | ototype Design                                               | 52 |    |

| 3.5             | Sel   | ection of Microcontroller for the Processing Element         | 55 |    |

| 3.6             | Pov   | wer and programming interface for the array                  | 57 |    |

| 3.7             | Co    | nclusion                                                     | 60 |    |

| Refe            | rence | es                                                           | 61 |    |

| CHAPT<br>SYSTC  |       | 4: PROGRAMMING AND VALIDATION OF THE INSTRUCT                |    | 62 |

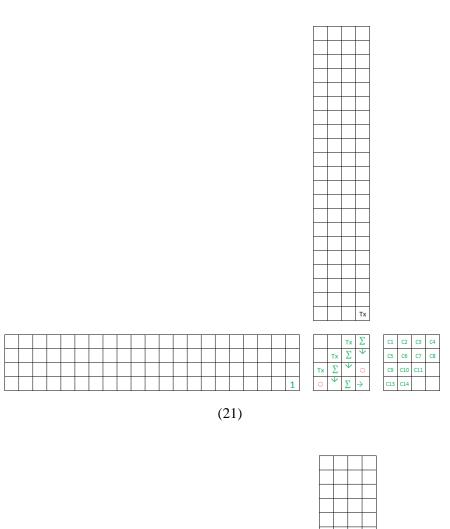

| 4.1             | Pro   | ogramming the Instruction Systolic Array                     | 62 |    |

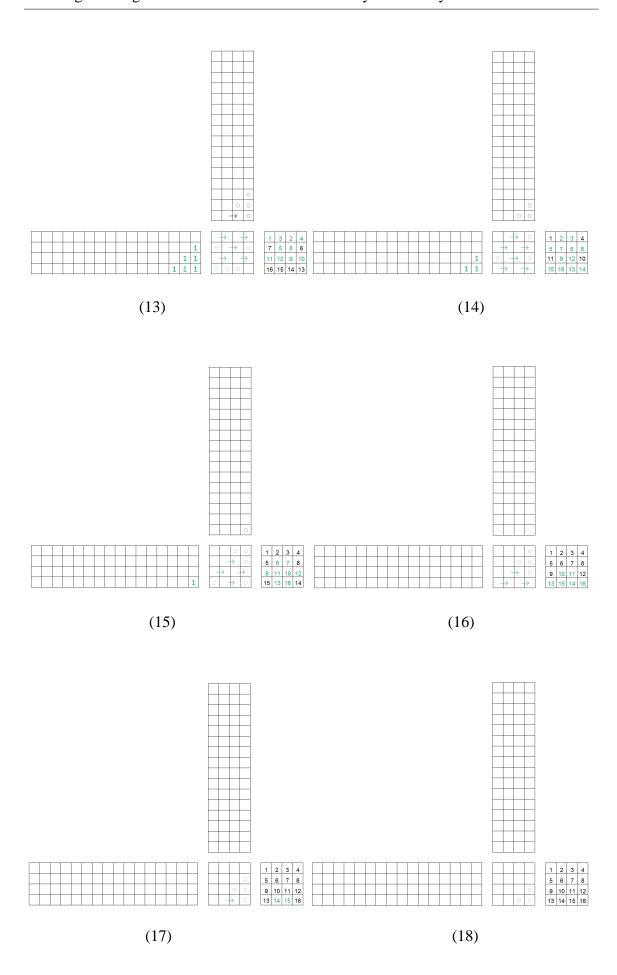

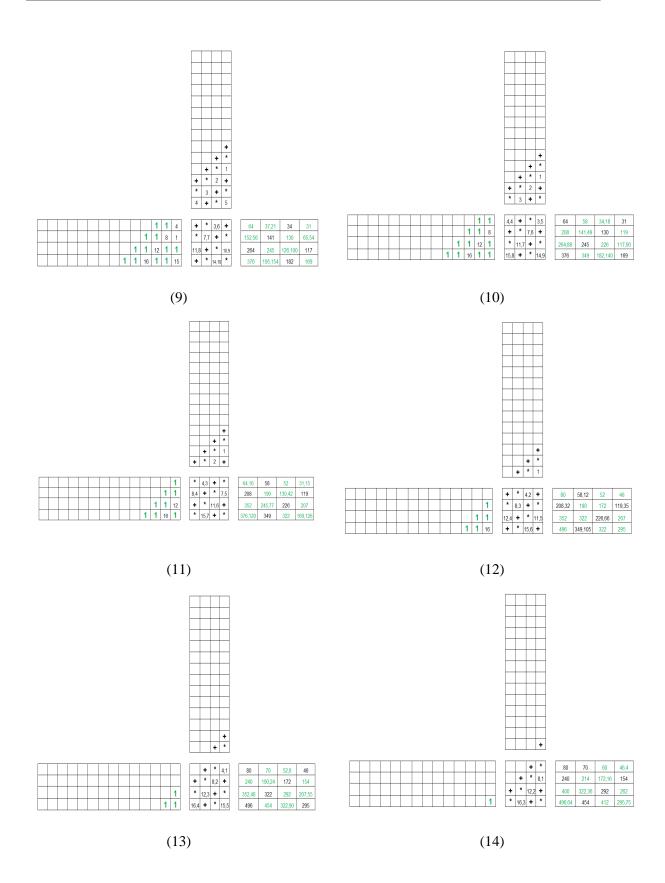

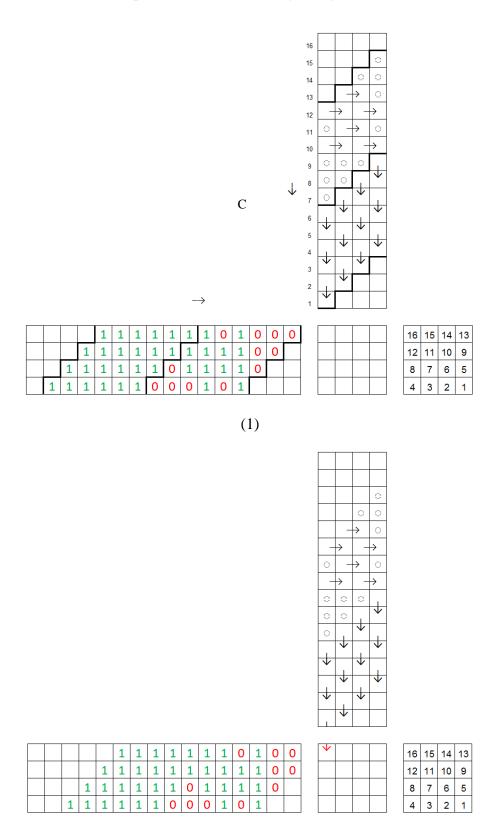

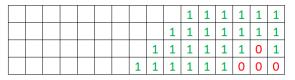

| 4.2             | Me    | rge Algorithm Validation                                     | 65 |    |

| 4.2             | 2.1   | Algorithm                                                    | 65 |    |

| 4.2             | 2.2   | Program                                                      | 66 |    |

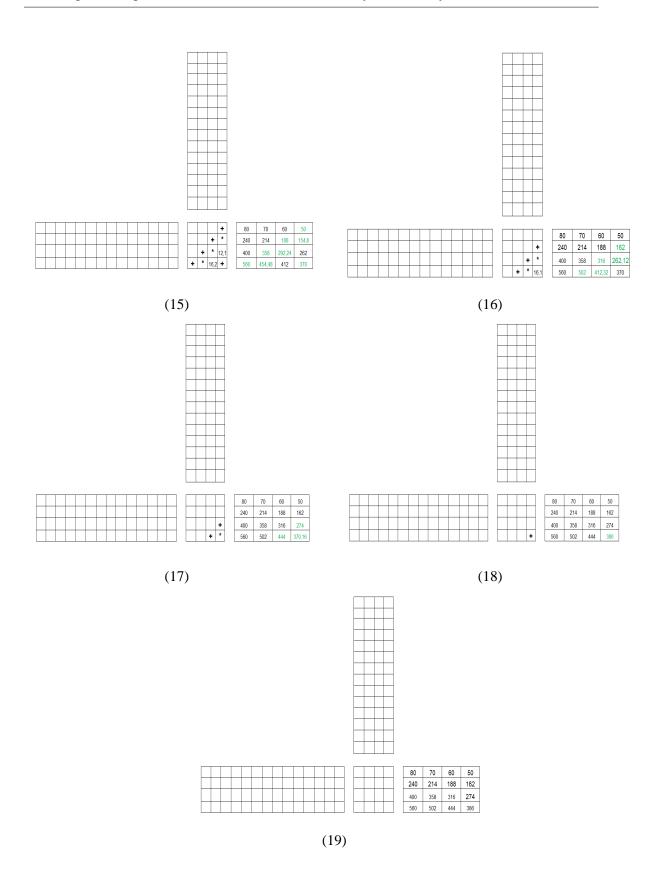

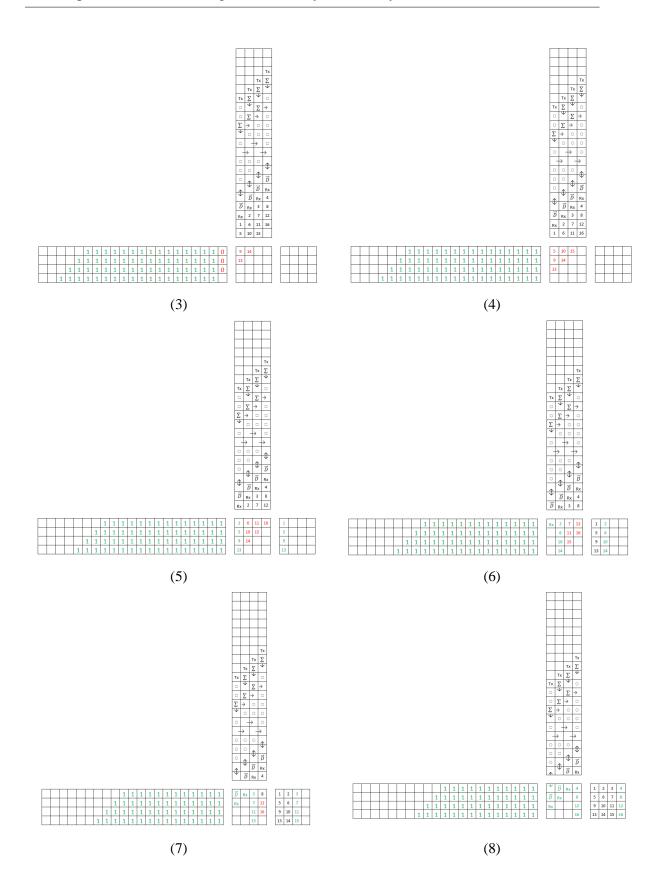

| 4.2             | 2.3   | Numerical example                                            | 67 |    |

| 4.2             | 2.4   | Result from the processor array                              | 71 |    |

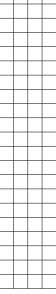

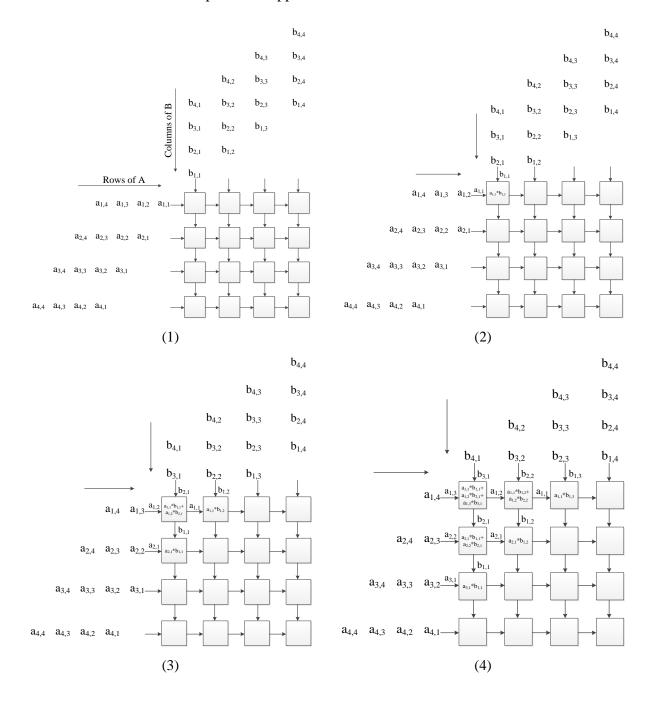

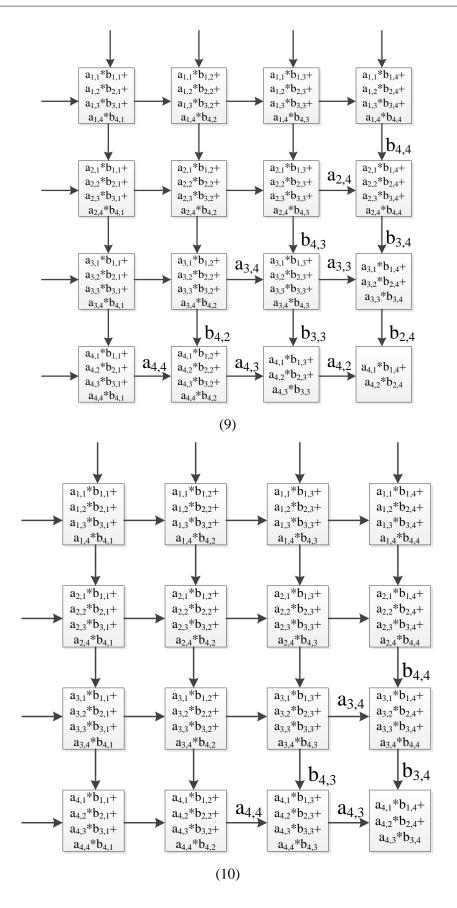

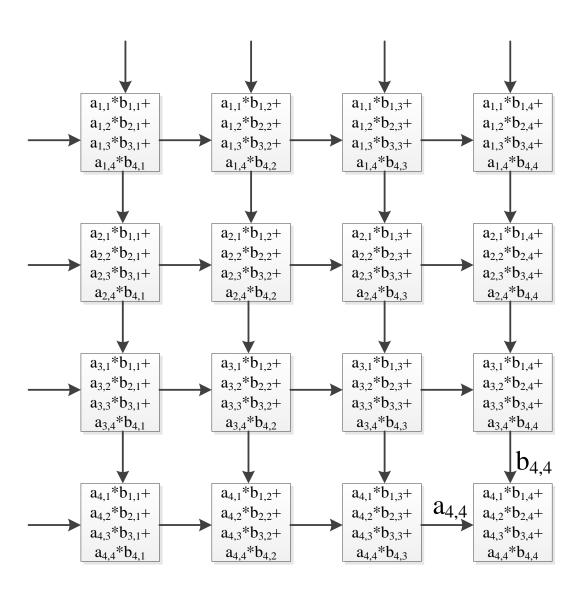

| 4.3             | Ma    | trix Multiplication Validation                               | 72 |    |

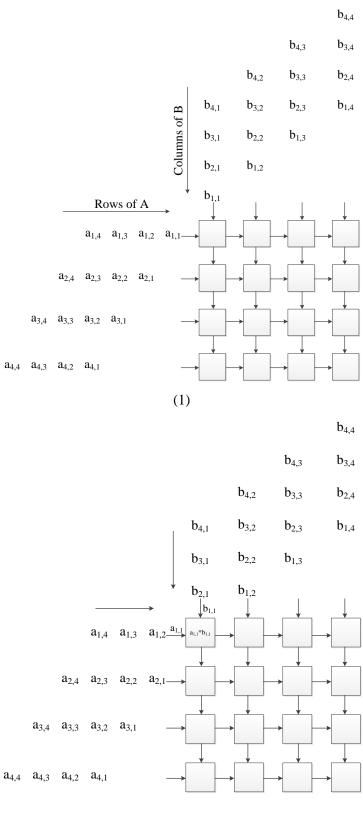

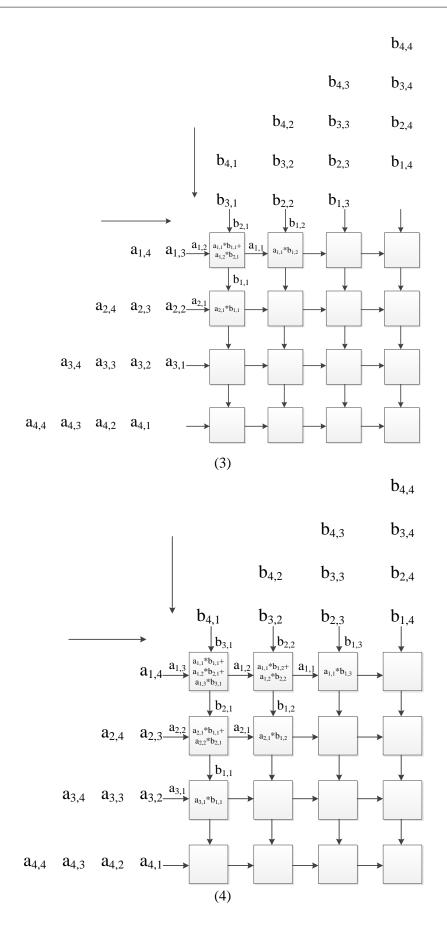

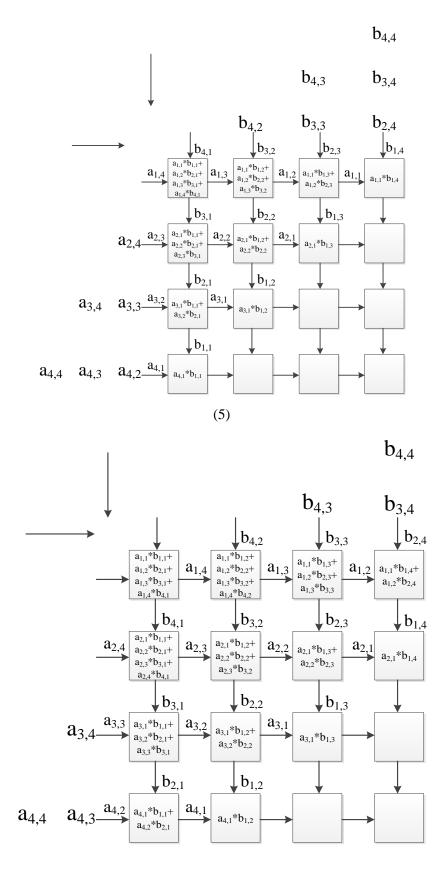

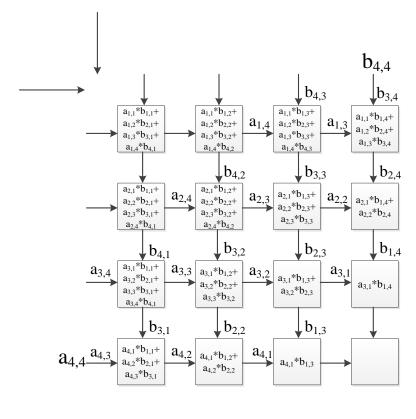

| 4.3             | 3.1   | Algorithm                                                    | 72 |    |

| 4.3             | 3.2   | Program                                                      | 76 |    |

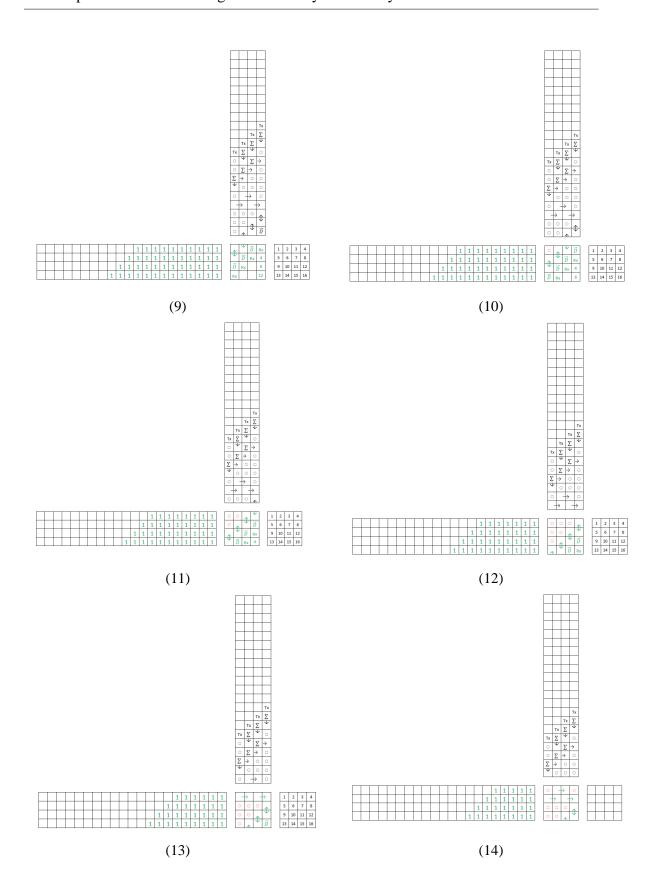

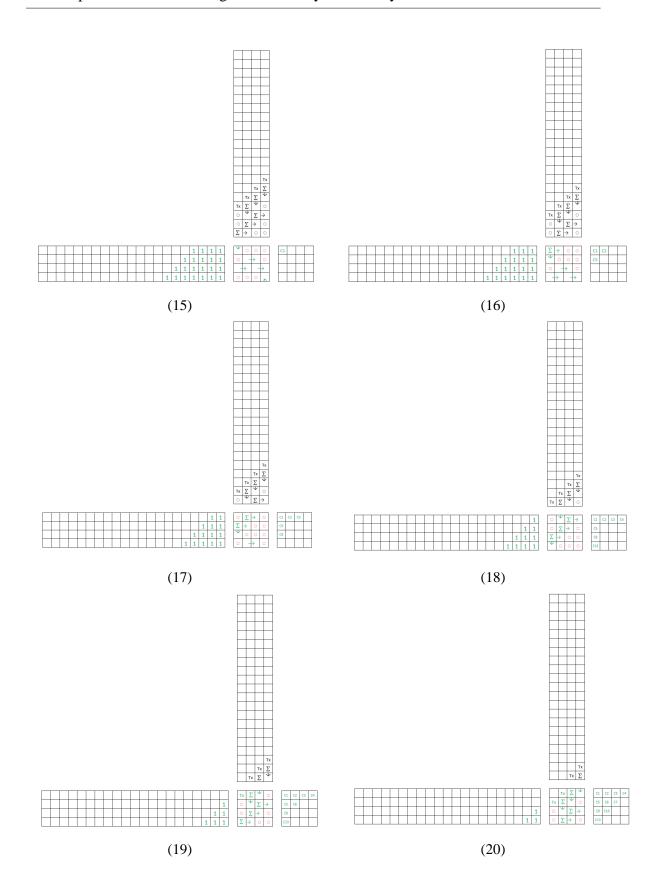

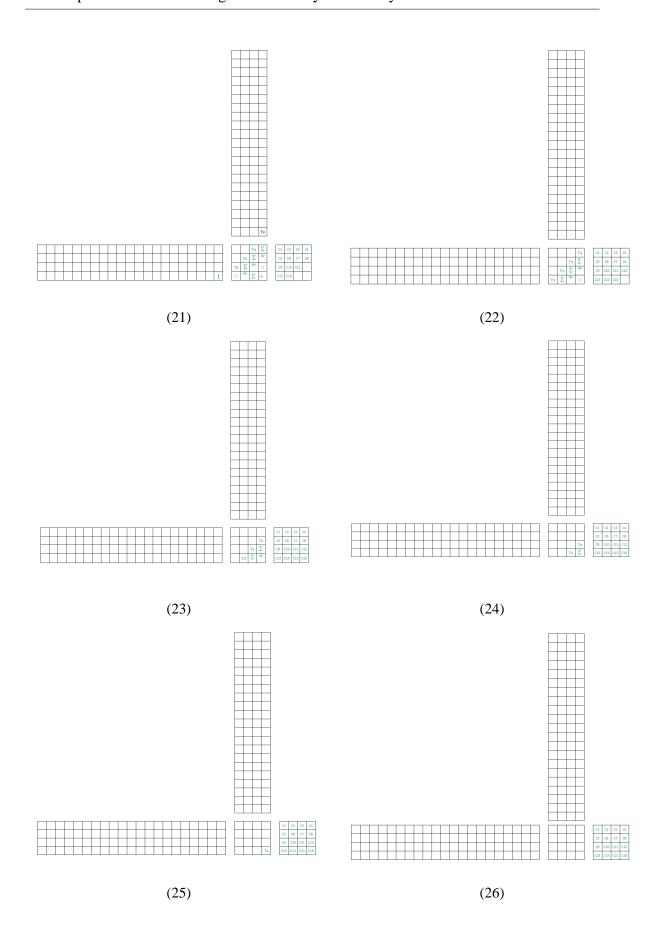

| 4.3             | 3.3   | Numerical example                                            | 77 |    |

| 4.3             | 3.4   | Result from the processor array                              | 81 |    |

Contents

| 4.4            | Conclus  | sion                                                                | 81    |

|----------------|----------|---------------------------------------------------------------------|-------|

| Refer          | ences    |                                                                     | 83    |

| CHAPT<br>ARRAY |          | SHAPE RECONSTRUCTION USING INSTRUCTION SYSTOR 84                    | LIC   |

| 5.1            | Introduc | ction                                                               | 84    |

| 5.2            | Backgro  | ound                                                                | 85    |

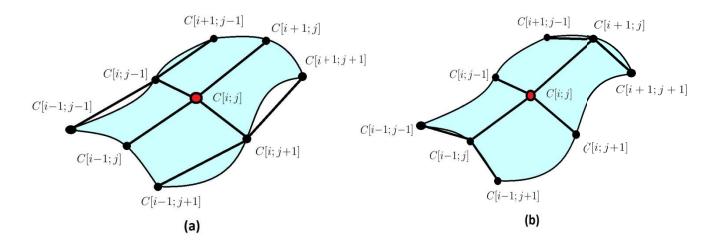

| 5.2            | .1 Sha   | ape Reconstruction algorithm                                        | 85    |

| 5.2            | .2 Sha   | ape Reconstruction from sensor orientation data                     | 87    |

| 5.3            | Experin  | nental Setup                                                        | 92    |

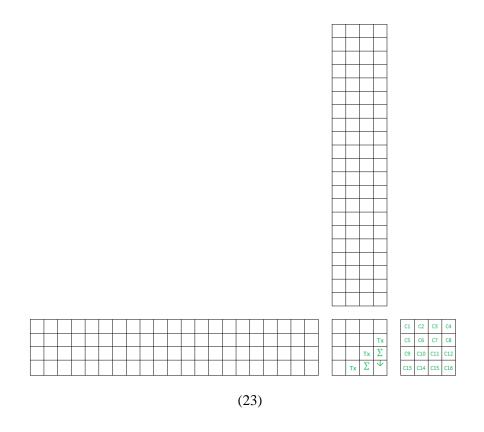

| 5.4<br>array   | _        | nming the shape reconstruction algorithm using Instruction systolic |       |

| 5.5            | Experin  | nental Results                                                      | . 101 |

| 5.6            | Conclus  | sion                                                                | . 105 |

| Refer          | ences    |                                                                     | . 106 |

| СНАРТ          | ER 6:    | CONCLUSION AND FUTURE WORK                                          | 107   |

| 6.1            | Contrib  | ution of this thesis                                                | . 107 |

| 6.2            | Suggest  | tions for future research                                           | . 108 |

| 6.2            | .1 Coi   | mputational performance                                             | . 108 |

| 6.2            | .2 Sca   | alability                                                           | . 108 |

| 6.2            | .3 Pro   | ogramming techniques                                                | . 108 |

| 6.2            | .4 Des   | signing                                                             | . 109 |

| 6.2            | .5 App   | plications                                                          | . 109 |

| 6.3            | Summar   | ry                                                                  | . 109 |

| Refer          | ences    |                                                                     | . 111 |

| LIST O         | FPUBLI   | CATIONS                                                             | A     |

| APPEN          | DIX      |                                                                     | 1     |

### LIST OF ABBREVIATIONS AND SYMBOLS

### **ABBREVIATIONS**

| Abbreviation | Expansion                                    |

|--------------|----------------------------------------------|

| 2D           | Two Dimension                                |

| 3D           | Three Dimension                              |

| ACK          | Acknowledgement                              |

| ASIC         | Application Specific Integrated Circuit      |

| C            | Control Unit                                 |

| CAN          | Controller Area Network                      |

| Cm           | Centimeter                                   |

| DIP          | Digital Image Processing                     |

| I            | Instruction                                  |

| $I^2C$       | Inter Integrated Circuit                     |

| ISA          | Instruction Systolic Array                   |

| MEMS         | Micro Electro Mechanical Systems             |

| MIMD         | Multiple Instruction Multiple Data           |

| MISD         | Multiple Instruction Single Data             |

| Ms           | Milliseconds                                 |

| P            | Processing Element                           |

| PCB          | Printed Circuit Board                        |

| R/W          | Read/Write                                   |

| S            | Sensor                                       |

| SCL          | Serial Clock Line                            |

| SDA          | Serial Data Line                             |

| SIMD         | Single Instruction Multiple Data             |

| SISD         | Single Instruction Single Data               |

| SPI          | Serial Peripheral Interface                  |

| SQS          | Surface Quality Scanner                      |

| UART         | Universal Asynchronous Receiver/ Transmitter |

| USB          | Universal Serial Bus                         |

| VLSI         | Very Large Scale Integration                 |

### **SYMBOLS**

| Symbol                    | Denotes                         |

|---------------------------|---------------------------------|

| $E_{\mathrm{g}}$          | Earth gravity field vector      |

| $E_{m}$                   | Earth magnetic field vector     |

| $M_{e}$                   | Global Earth reference matrix   |

| $M_s$                     | Sensor measurement matrix       |

| R                         | Rotational matrix               |

| $R_P$                     | Pull-up Resistance ( $\Omega$ ) |

| $\mathbf{S}_{\mathrm{g}}$ | Sensor gravity field vector     |

| $S_{m}$                   | Sensor magnetic field vector    |

| $V_{\mathrm{dd}}$         | Supply Voltage (V)              |

## LIST OF FIGURES

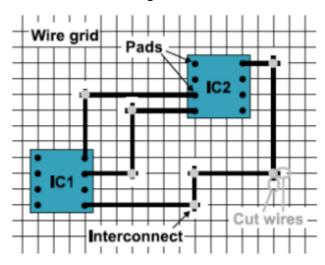

| Figure 1.1: Partitioning of a wearable system from a technological point of view  | 5      |

|-----------------------------------------------------------------------------------|--------|

| Figure 1.2: Circuit incorporated in a textile with wire grid [1.15]               | 6      |

| Figure 1.3: Smart fabric in healthcare [1.15]                                     | 8      |

| Figure 1.4: Muscle Activating Smart suit [1.15]                                   | 8      |

| Figure 1.5: Networked Jacket [1.15]                                               | 9      |

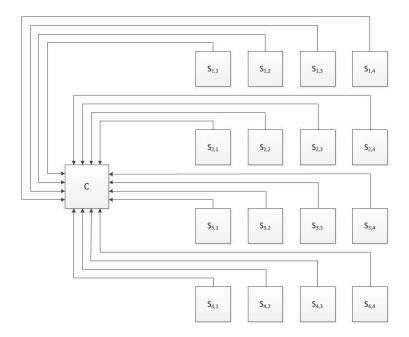

| Figure 2.1: Concept 1 showing Control unit C and Sensors S <sub>n,m</sub>         | 15     |

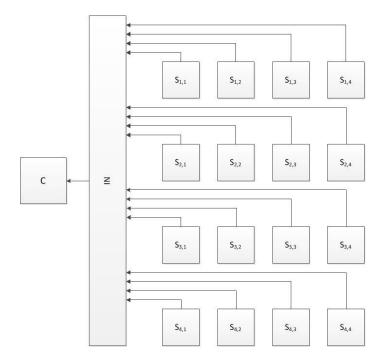

| Figure 2.2: Concept 2 where IN shows an interconnection such as bus               | 15     |

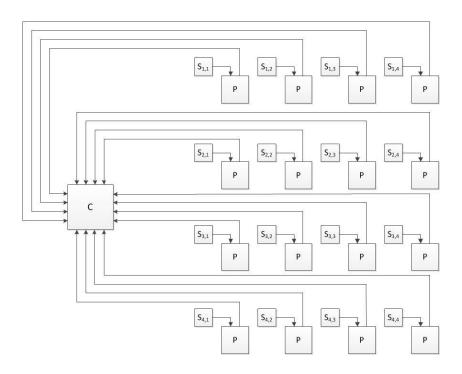

| Figure 2.3: Concept 3 showing the inclusion of individual processing elements P.  | 16     |

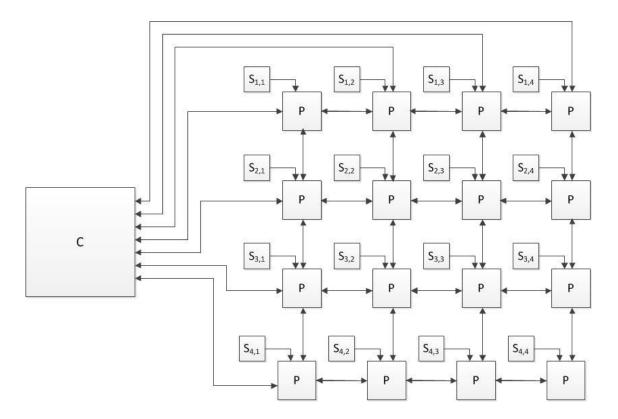

| Figure 2.4: Concept 4 showing communication between neighbouring P's              | 17     |

| Figure 2.5: Flynn's taxonomy of computer architectures: a) SISD, b) SIMD, c) M    | ISD,   |

| and d) MIMD (C: Control unit, P: Processor, M: Memory, I N: Interconnection       |        |

| Network (Bus))                                                                    | 21     |

| Figure 2.6: Duncan's taxonomy of parallel computer architectures                  | 22     |

| Figure 2.7: General systolic organization                                         | 27     |

| Figure 2.8: Linear systolic array                                                 | 28     |

| Figure 2.9: Orthogonal systolic array                                             | 29     |

| Figure 2.10: Hexagonal systolic array                                             | 29     |

| Figure 2.11: Triangular systolic array                                            | 30     |

| Figure 2.12: Execution of an ISA instruction                                      | 32     |

| Figure 2.13: Instruction cycle                                                    | 33     |

| Figure 2.14: Execution of an ISA diagonal (I - Instruction, S - Selector bit, + - |        |

| Execution)                                                                        | 34     |

| Figure 2.15: Execution of ISA program                                             | 36     |

| Figure 2.16: Systola 1024 from [2.21]                                             | 37     |

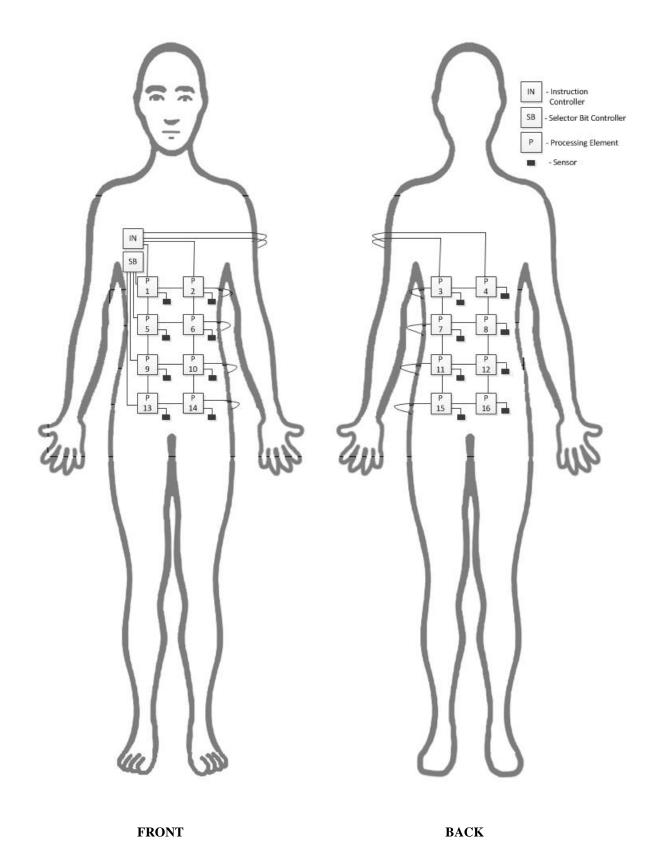

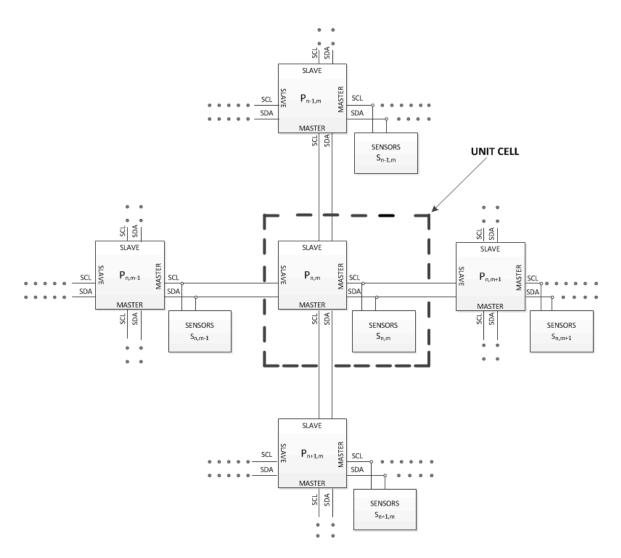

| Figure 3.1: System concept                                                        | 42     |

| Figure 3.2: General concept of a sensor system with integrated processing elemen  | ts for |

| human body applications                                                           | 43     |

List of figures xi

| Figure 3.3: Different methods for transfer of information                                  | 45    |

|--------------------------------------------------------------------------------------------|-------|

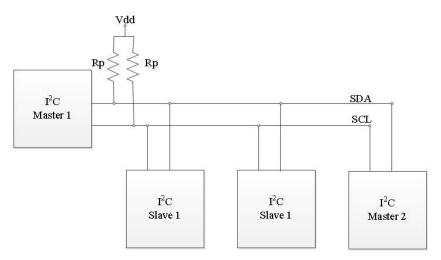

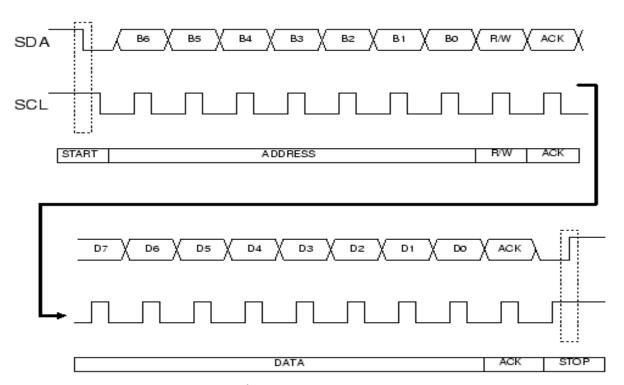

| Figure 3.4: Typical I2C bus                                                                | 49    |

| Figure 3.5: Basic Mechanism in I2C from NXP Semiconductors adapted from [3.7]              | 51    |

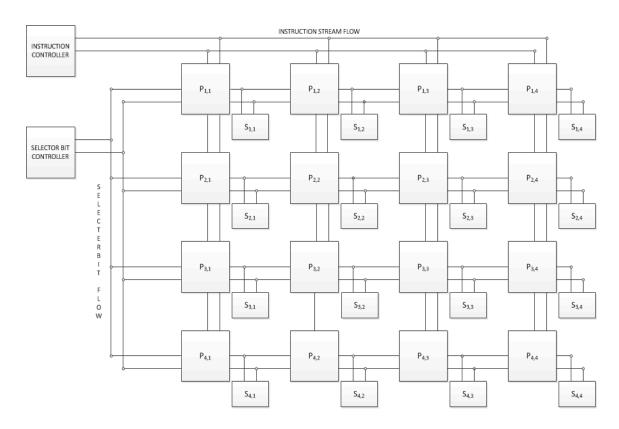

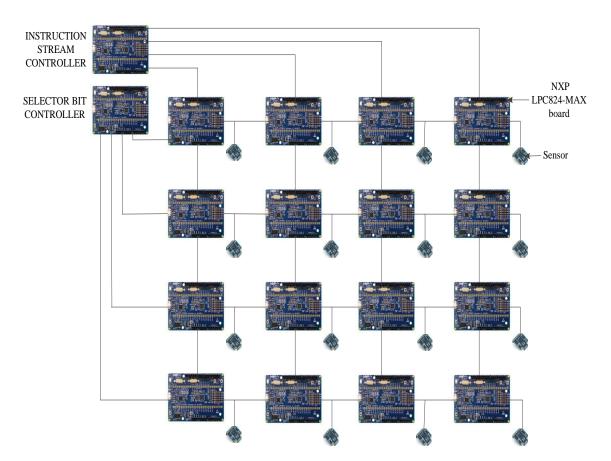

| Figure 3.6: Processor array showing grid arrangement                                       | 53    |

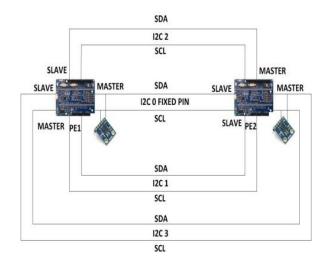

| Figure 3.7: Detail of I2C bus connections                                                  | 54    |

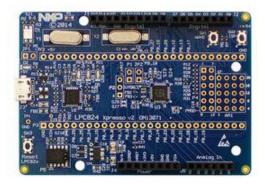

| Figure 3.8: Microchip PIC16F1829                                                           | 55    |

| Figure 3.9: 32-bit ARM Cortex-M0+ LPC824 microcontroller mounted on NXP                    |       |

| LPC824-MAX board                                                                           | 55    |

| Figure 3.10: Processor Array with peripherals                                              | 56    |

| Figure 3.11: I2C connection between two microcontrollers with sensor                       | 57    |

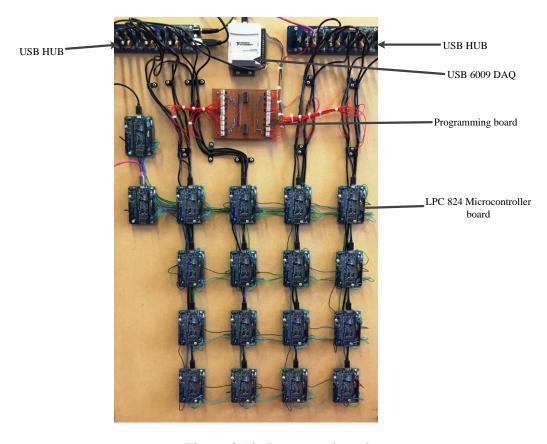

| Figure 3.12: Prototype board                                                               | 57    |

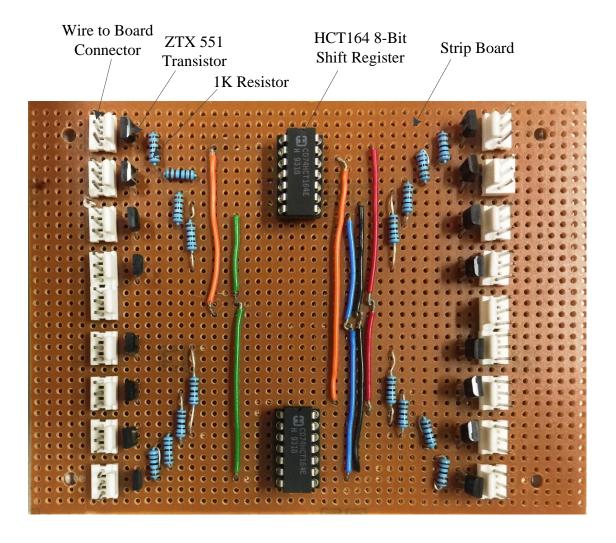

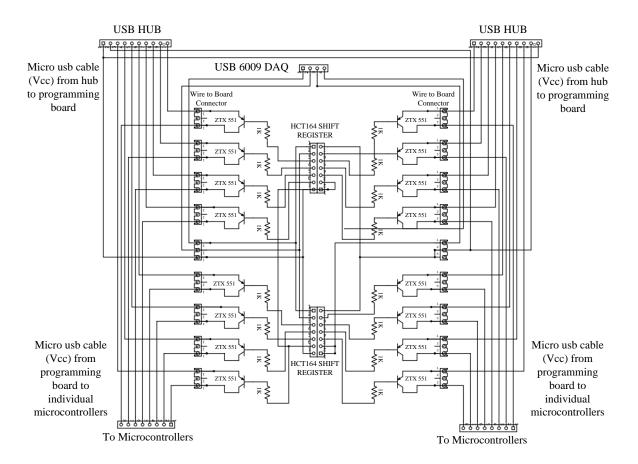

| Figure 3.13: Programming board (switching circuit)                                         | 58    |

| Figure 3.14: Schematic for the switching circuit                                           | 59    |

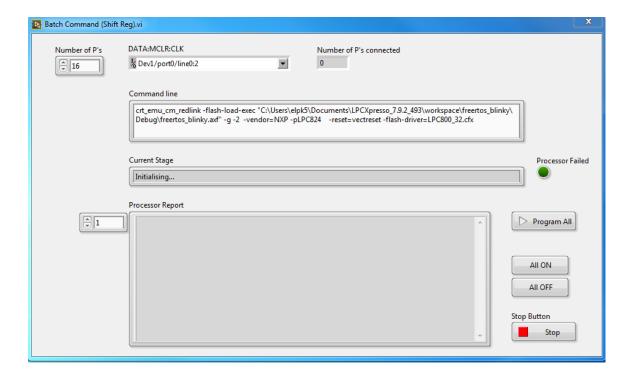

| Figure 3.15: Application for programming the microcontrollers                              | 60    |

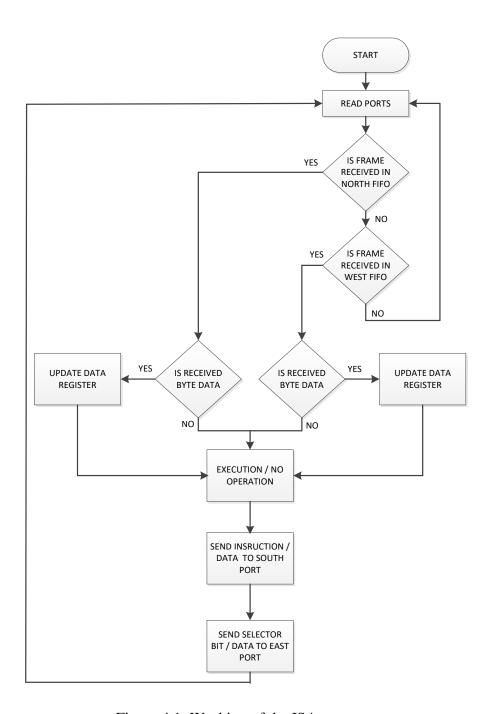

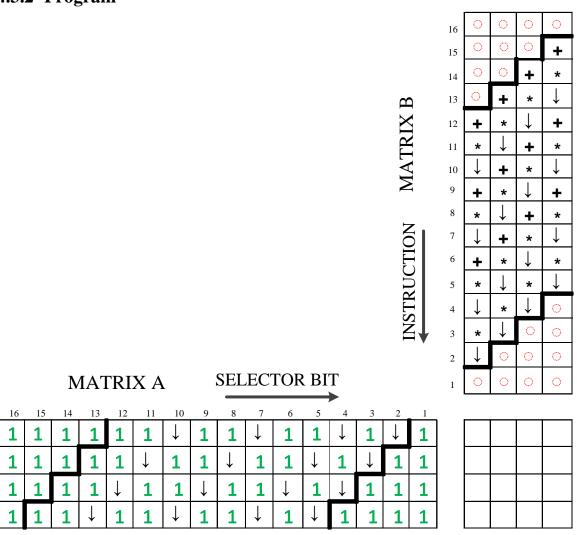

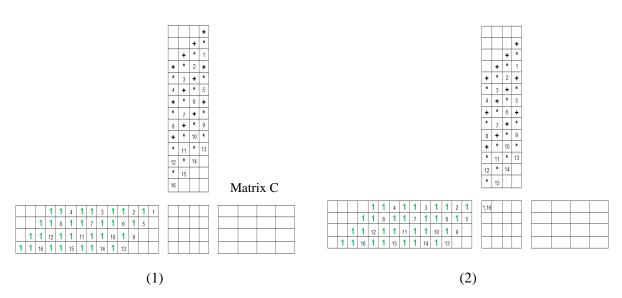

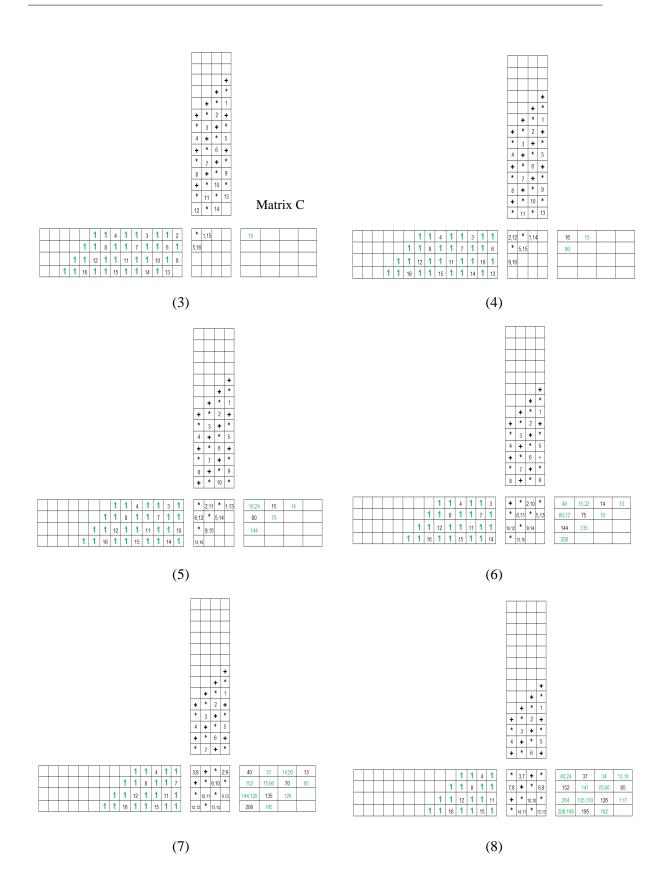

| Figure 4.1: Working of the ISA program                                                     | 64    |

| Figure 4.2: ISA program for merge algorithm                                                | 66    |

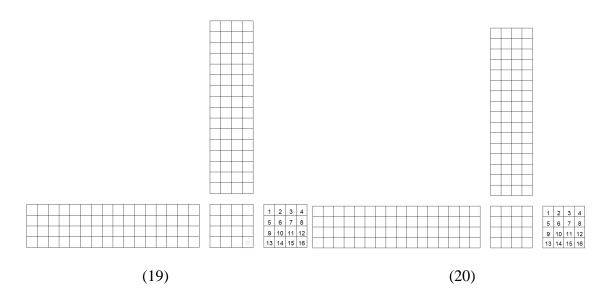

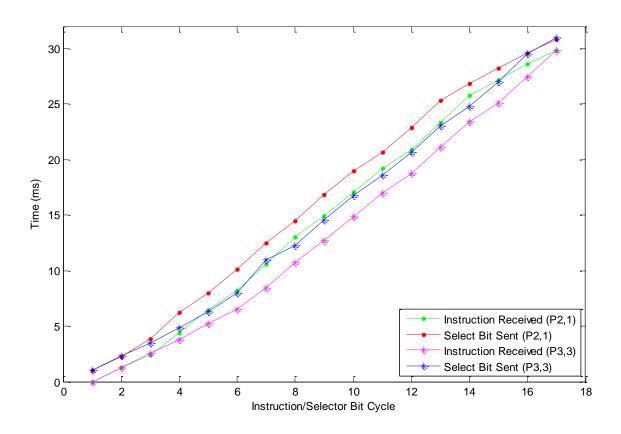

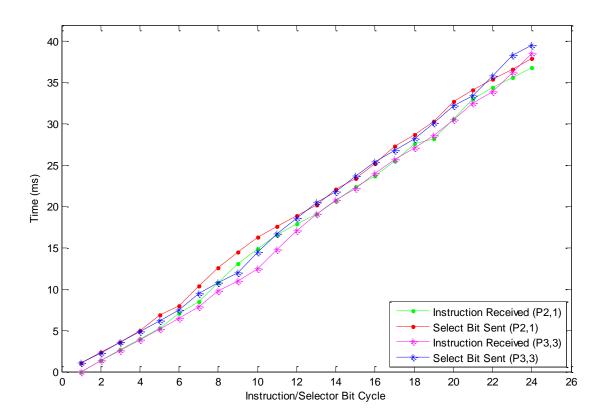

| Figure 4.3: Performance analysis for P(2,1) and P(3,3)                                     | 72    |

| Figure 4.4: ISA Program for Matrix Multiplication                                          | 76    |

| Figure 4.5: Performance analysis for P(2,1) and P(3,3)                                     | 81    |

| Figure 5.1: Surface segment structure. Each segment consists of center C and four          |       |

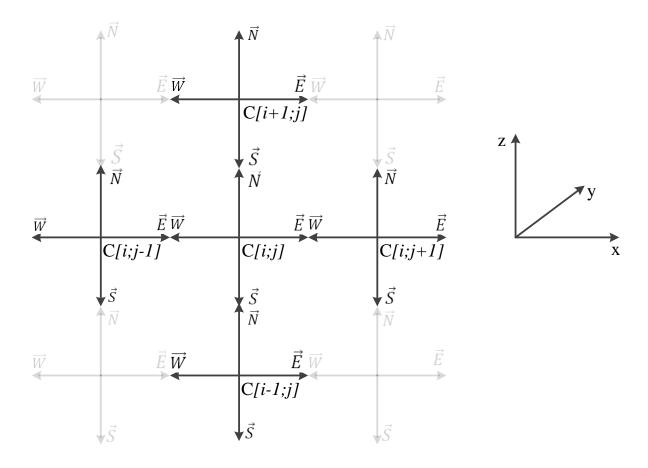

| direction vectors $N$ , $E$ , $S$ and $W$ [5.1]                                            | 88    |

| Figure 5.2: Structure of control point connections. $C[i; j]$ - reference point. (a) Sing- | le    |

| reference row is obtained, then all other points are calculated with column method.        | (b)   |

| Single reference column is obtained, then all other points are calculated with row         |       |

| method adapted from [5.1]                                                                  | 89    |

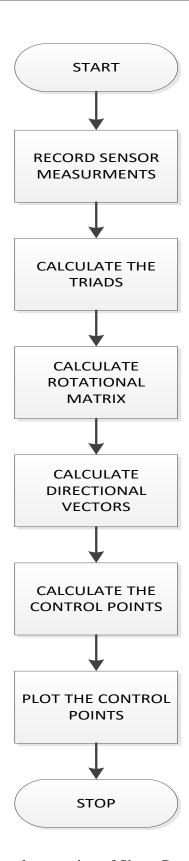

| Figure 5.3: Step wise implementation of Shape Reconstruction Application                   | 91    |

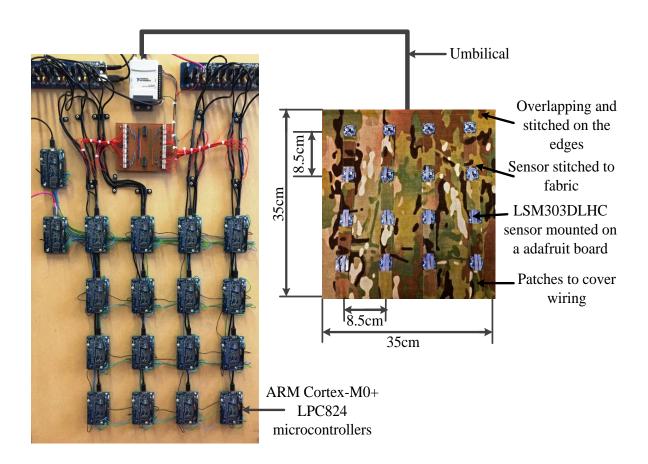

| Figure 5.4: LSM303DLHC mounted on Adafruit board                                           | 92    |

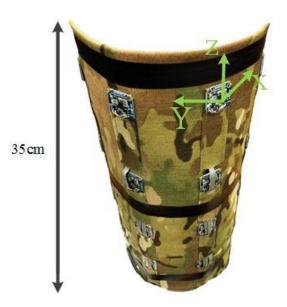

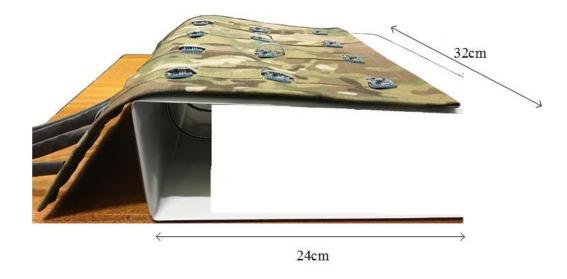

| Figure 5.5: Sensors embedded with fabric                                                   | 93    |

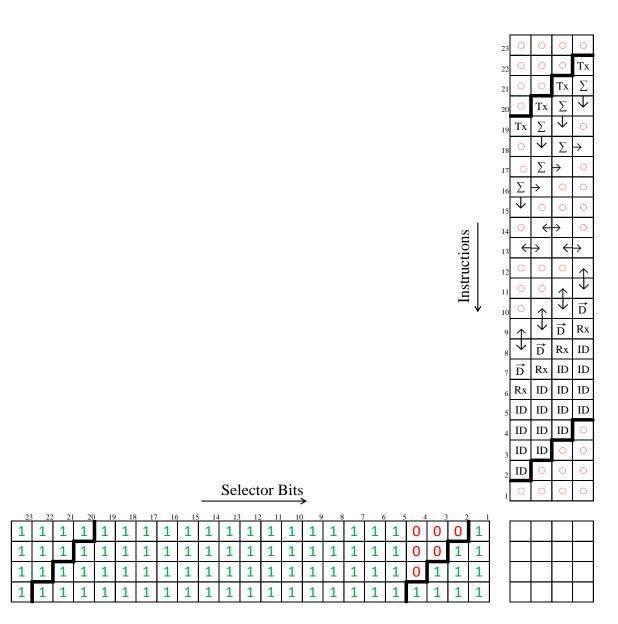

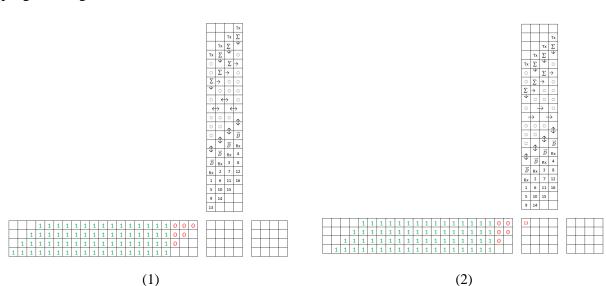

| Figure 5.6: ISA firmware for shape reconstruction application                              | 95    |

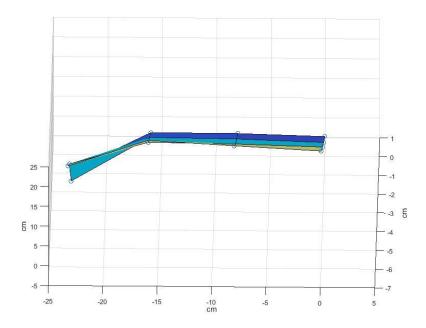

| Figure 5.7: Fabric wrapped on a cylindrical object                                         | . 101 |

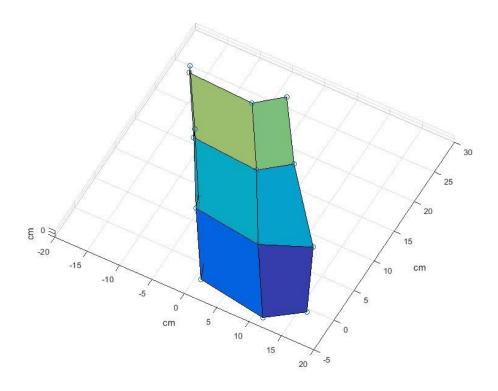

| Figure 5.8: Reconstructed shape of the object                                              | . 102 |

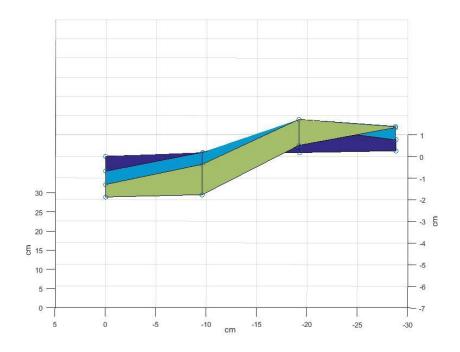

| Figure 5.9: Fabric placed on the object                                                    | 102   |

List of figures xi

| Figure 5.10: : Reconstructed shape of the object        | 103 |

|---------------------------------------------------------|-----|

| Figure 5.11: Fabric placed on the object                | 103 |

| Figure 5.12: Reconstructed shape of the object          | 104 |

| Figure 5.13: Performance analysis for P(2,1) and P(3,3) | 105 |

## LIST OF TABLES

| Table 2.1: Comparison between concepts                          | 17 |

|-----------------------------------------------------------------|----|

| Table 3.1: Difference between serial and parallel communication | 45 |

| Table 3.2: Comparison of different bus system                   | 46 |

| Table 4.1: Instruction symbol definition                        | 67 |

# CHAPTER 1: INTRODUCTION

In today's technological era, wearable electronics has become a crucial part of day to day activities. There has been a lot of development in the field of wearable electronics due to continuous quest of innovation by industrial and academic researchers. In earlier days, communication, electronics, and computing devices used were mainly non-portable because of their large size and complexity. Next introduced were smaller and lighter portable devices along with integration of some additional functions. Due to continuous improvements, now we have multi-purpose micro devices which can be embedded into wearables and are better in terms of many criteria such as communication, weight, energy management, durability, comfort and size [1.1].

In application-oriented research, the concept of wearable computing is a fast-growing area. Wearable technology can be used in various sectors like healthcare, military applications, gaming, sports, music and emergency services [1.2]. Wearable electronics can take the form of a discrete device such as a watch or arm band or it may be integrated into clothing opening an entirely new field of applications. As wearable devices increase in the level of complexity and become more integrated the opportunities to integrate more sophisticated functionality also increase [1.3]. NASA 3D printed space [1.4] fabric could potentially be used for large antennas and other deployable devices, because the material is foldable and its shape can change quickly. The fabrics could also eventually be used to shield a spacecraft from meteorites, for astronaut spacesuits, or for capturing objects on the surface of another planet. Currently, this development is in the early stages but it is easy to see how electronics may need to be incorporated.

The remarkable progress in miniaturization of microelectronics and progress in the invention of new materials have made it possible to integrate the functionality into clothing [1.5]. The main vision of wearable computing is to make electronic systems an

important part of everyday clothing in the future which will serve as intelligent personal assistants. Wearable devices have the potential to be wearable computers and not mere input/output devices for the human body. The present thesis focuses on introducing a new wearable computing paradigm which can improve the performance of a highly human-integrated computer.

As a result of remarkable innovations in embedded systems over a period of last thirty years, the value of microprocessors and communication technology have reduced significantly in terms of cost in real terms. Due to this, distributed computer systems have become a feasible substitute for uni-processor and centralised systems in various application areas of embedded systems.

The research challenge is to address the problems of low bandwidth sensors in wearable electronics. One of the solutions to high bandwidth sensor is the use of parallelism.

#### 1.1 Area of Research

This thesis will focus on a distributed computing platform for wearable electronics. A brief introduction to the mainly used technologies in the current thesis is discussed in the following sub-sections.

#### 1.1.1 Distributed Computing

A distributed computing system is a collection of processor-memory pairs connected by a communications subnet and logically integrated into varying degrees by a distributed operating system or distributed database system[1.6]. The communications subnet may be a widely geographically dispersed collection of communication processors or a local area network. The widespread use of distributed computer systems is due to the price-performance revolution in microelectronics the development of cost effective and efficient communication subnets (which is itself due to the merging of data communications and computer communications), the development of resource sharing software, and the increased user demands for communication, economical sharing of resources, and productivity[1.5]. A distributed computing system potentially provides significant advantages, including performance, reliability, resource sharing, and extensibility[1.6].

The study of distributed computing has grown to include a large range of applications[1.7],[1.8]. However, at the core of all the efforts to exploit the potential power of distributed computation are issues related to the management and allocation of system resources relative to the computational load of the system. One measure of the usefulness of a general-purpose distributed computing system is the system's ability to provide a level of performance corresponding with the degree of multiplicity of resources present in the system. This is particularly true of attempts to construct large general-purpose multiprocessors[1.7].

An interesting area for research which is increasingly getting noticed is decentralized processing [1.9]. As compared with centralised processing approach, the main advantage it provides is increased robustness. The entire system would never fail resulting from the malfunctioning of processors or sensors or other components. Nodes can be more flexible in distributed networks because nodes need not be reinitialized when nodes are introduced, moved and removed from the network for new topology [1.10].

There are also potentials of avoiding the fusion of a multitude of sensor data at once and adding more units would have potential of cost saving because mostly same design only needs to be duplicated. These are other benefits of processing the data in a distributed manner [1.11].

#### 1.1.2 Distributed Sensor Networks

In detection applications, distribution of a large amount of simple sensing devices is increasingly getting more interest, mainly inspired from its perception in biological systems [1.11]. Focus on fusion of sensor signals instead of strong analysis algorithms, and a scheme to distribute sensors, results in new paradigm. Especially in wearable computing, where sensor data continuously changes, and clothing provides an ideal supporting structure for simple sensors [1.11].

The justification for using sensors in a wearable computing architecture ranges from use in intelligence augmentation to automating tasks depending on particular features of the environment. Regardless of whether these applications would be sought after by a large

community, one trend that can be observed is that sensors are gradually becoming part of mobile and wearable devices [1.11].

Wearable computers are no exception to this concept either, since large surfaces of clothing are an ideal supporting platform for a multitude of sensors, provided they are miniaturized so that they do not obstruct the wearer. This size constraint often means that the quality of the sensor itself is compromised as well, which leads to the concept of many simple sensors [1.11].

#### 1.1.3 Wearable Electronics

Wearable Electronics is a new technological concept that integrates electronics with clothing and opens up a whole array of well designed, multi efficient and wearable electro textiles which can sense and monitor various functions of the body, can transfer data, can offer individual environment control and are able to provide communication facilities along with various other major applications[1.3]. The potential of wearable electronics is widespread when looking at so many innovatory advancements that are happening at an extraordinary rate in many fields of science and technology. These developments have the capability to change the world and they will very rapidly pervade into commercial products[1.12], [1.13]. Expert high-quality clothing will be available to make it possible to observe the important life signs of new born babies, clothing that can record the routine of an athlete's muscles and technique efficient clothing that can call even a rescue team for victims of accidents that occur due to bad weather conditions and there are limited options for help[1.13].

As described by I.Loacher [1.3], system-on-textile is the equipped clothing that combines electrical functions with apparel and at the same time maintains the wearing comfort. Another name for this is Smart Fabrics. The main aim is not to mix large electronic devices into clothing but rather small and committed electrical devices, for e.g. sensors along with their signal conditioning components taking the comfort of clothing into consideration. The sensors can be placed into positions where they can accomplish their sensing task in best possible way by integrating them directly into clothing such as accelerometers at joints. In contrast to this, chips that are having hundreds of pads and relatively high power dissipation, for e.g. high-speed microcontrollers are favourably placed into stiff enclosures such as belt buckles and

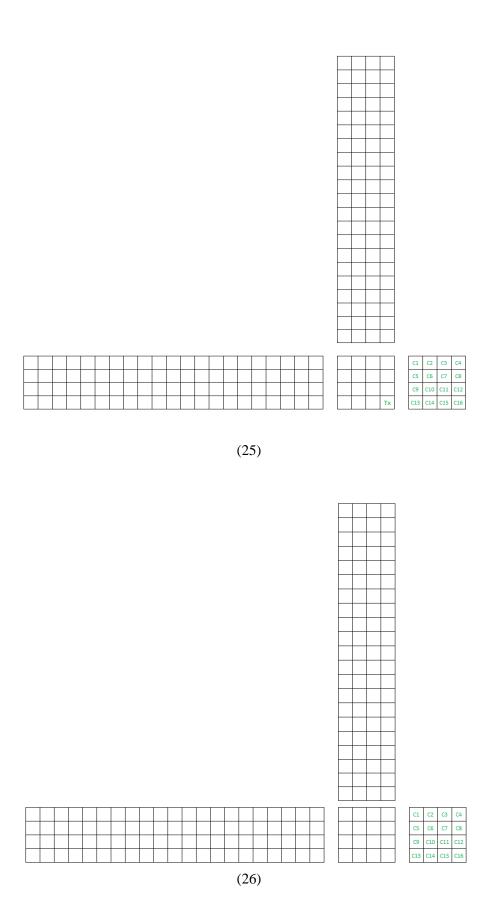

accessories. By keeping them there, circuits take advantage of the properties of Printed Circuit Board (PCB) technology like high-density wiring, multilayer and precisely controlled impedances. Fig 1.1 shows the partitioning of a wearable system from a technological point of view.

Figure 1.1: Partitioning of a wearable system from a technological point of view

The fabrics containing electronics as well as interconnections integrally woven into them are called as Electronic Textiles or e-textiles [1.14]. Electronic textiles provide physical flexibility and typical size which is hard to obtain from other existing electronic manufacturing techniques. electronic As the components interconnections are woven into fabric, they are less visible and there are less chances of getting tangled in objects nearby. One important feature of E-textiles is their easy adaptation to any particular application requiring fast changes in computational and sensing requirements making them attractive for power management and context awareness. The vision of wearable computing is to make the electronic systems an important part of everyday clothing in the future. Although, these electronic devices should meet certain criteria to be wearable. The main feature of wearable systems will be their capability to identify the activity and the behavioural status of the person using them and the situations and environment around and then to further utilize this information to adapt the functionality and systems configuration [1.14].

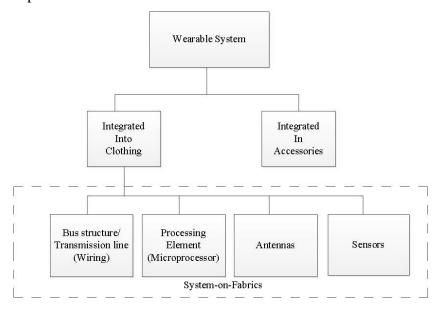

There are different ways to produce electrically conductive fabrics. A technique is to incorporate conductive yarns directly into a textile structure, for instance, through weaving [1.14]. However, the incorporation of conductive yarns in a textile structure is complex and rarely a uniform process as the electrically conductive fabric has to be soft in touch or comfortable to wear rather than rigid and hard. Fig 1.2 shows an approach to incorporate circuits in a textile with wire grid [1.15].

Figure 1.2: Circuit incorporated in a textile with wire grid [1.15]

#### 1.1.4 Smart Fabrics

Electronics and Clothing were considered to be two different sectors of industries till now but now they are working together to produce some integrated and new innovative products[1.16], [1.17].

From Lymberis and Paradiso [1.18], since last 10-15 years, considerable advancements in the terms of data processing, miniaturization, functionality, seamless integration, comfort and communication have made Wearable Technology and integrated systems as well established fields. The textile industry is also increasingly interested by the potential for new value-added clothing products such as smart clothing and functionalised apparel and this is also driving the development of wearable systems.

In [1.17] Smart Fabrics are considered as the integrated systems into textiles and includes sensors, a power source, actuators and computing, forming a complete package for an interactive communication network. This type of smart systems can only be imagined by combining the innovative advances in fields like fibre and polymer research, microelectronics, embedded systems, advanced material processing,

telecommunication, signal processing and nanotechnologies. The most common platform to integrate smart materials in the form of fibres is textile. In textiles, by combining the chemical surfaces processes, the properties of the materials can be improved efficiently and also the structure of fabrics permits to exercise redundant sensor configurations.

One of the advantages of wearable application is that the smart fabrics provide a natural interface with the body considering comfort clothing with the help of precise and reproductive positioning of the sensors [1.18]. Bearing in mind comfort, the sensors are covered within the layers of fabric such as fibre optic or sometimes the fabric itself is used as a sensor or a distributed network of sensors.

Fabric computing includes designing a computing fabric which contains interconnected nodes but when observed from some distance, it seems like a fabric [1.19]. The two key components of fabrics are nodes and links. Nodes are processor(s), peripherals and memory whereas links can be described as the functional interconnection between nodes. Mainly it indicates towards a merged high-performance computing system that contains parallel processing functions, storage and networking linked with each other via high bandwidth interconnects.

Smart textiles or smart fabrics refer to clothing having integral electronics and interconnections woven into the fabrics itself [1.15]. This arrangement provides physical flexibility which is not attainable with other electronic manufacturing techniques. The electronic components and interconnections have low visibility and are less prone of getting tangled as they are embedded and woven with fabric [1.15]. The vision is to make smart textiles a part of day to day clothing. The main features of smart textiles include their ability to identify the activities around them as well as of their owner automatically and then to use the collected information to adjust functionality [1.15].

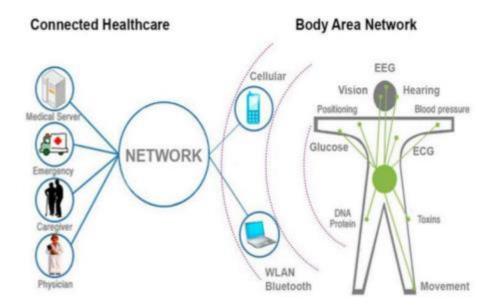

Medicine is a major area which has benefitted immensely in the applications developed from the combination of smart textiles and wearable computers in the form of Telemedicine. Fig 1.3 shows the overview of the use of smart fabrics and wearable computers in healthcare [1.15].

Figure 1.3: Smart fabric in healthcare [1.15]

In sports generally, important monitoring functions such as body temperature, heart rate, breathing, and other physiological parameters such as number of steps taken and total distance travelled can be achieved using smart devices embedded on sport clothing. Smart textiles in sports also help in protection against injury of athletes. Fig 1.4 shows an athlete wearing muscle activation smart suit [1.15].

Figure 1.4: Muscle Activating Smart suit [1.15]

The jacket shown in Fig 1.5 helps in the tracking of the location of the wearer using a GPS and project the map onto a flexible display screen on the sleeve of the jacket. It also displays the moods of the wearer via colour changes and signs [1.15].

Figure 1.5: Networked Jacket [1.15]

The Ohio State University researchers under the guidance of John Volakis have taken the next step toward the design of functional textiles clothes that gather, store, or transmit digital information [1.21]. This technology can result in lots of applications with further developments like sports equipment that monitors athletes performance, even a flexible fabric cap that senses activity in the brain, workout clothes that monitor your fitness level, a bandage that tells your doctor how well the tissue beneath it is healing, shirts that act as antennas for your smart phone or tablet [1.21].

#### 1.2 Research Aim

The overall aim of this work is to advance the field of sensor networks by embedding parallel processing concepts. The application that the thesis will address is in human monitoring.

#### 1.3 Objectives

The specific objectives of this thesis are:

- To propose a new sensor networking paradigm that exploits processor level parallelism and introduces the concept of on-fabric computation.

- To validate the method and produce parallel program that can be used on the sensor network array.

- To produce a physical demonstrator for a specific measurement scenario that has relevance to human monitoring.

#### 1.4 Novel contribution of the thesis

- To propose a new concept for distributed on-fabric processing.

- To implement a parallel computing architecture optimised for fabric mounting.

- To apply the architecture to a physical demonstrator containing an array of computing nodes.

- A present a set of measurements obtained from a physical demonstrator.

#### 1.5 Thesis Outline

#### **Chapter 2: A Novel Parallel Distributed Architecture**

The purpose of the chapter is to consider the concepts for attaching sensors to processing elements. This chapter will review the state of the art in parallel computer architectures and will identify a suitable architecture for a wearable computer system. The chapter also considers alternative architectures and how they interconnect with the physical local sensors.

# **Chapter 3: Implementation of Instruction Systolic Array for Smart Fabrics**

An implementation of a prototype design of the novel architecture proposed in chapter 2 is given. The chapter also explains the challenges of implementing the design using commercial off-the-shelf components. The prototype has been designed using the concept of the Instruction Systolic Array. This chapter also discusses the bus systems and an off-the-shelf microcontroller that has been used to implement the prototyped concept.

#### Chapter 4: Programming and validation of Instruction Systolic Array

This chapter of the thesis describes the programming of the instructing systolic array and implementing the instruction systolic array on an array of off-the-shelf microcontrollers. To illustrate some of the basic definitions of the previous chapter, parallel algorithm examples are presented.

# Chapter 5: Shape Reconstruction Application using Instruction Systolic Array

This chapter introduces a 2D mesh architecture prototype based on the Instruction systolic array paradigm for distributed computing on fabrics. A real-time shape sensing and reconstruction application executing on ISA architecture and demonstrates a physical design for a wearable system based on the ISA concept constructed from off-the-shelf microcontrollers and sensors.

#### **Chapter 6: Conclusion**

This chapter summarizes the contributions of the thesis and discusses the future work that can be conducted.

#### References

[1.1] S. Lam Po Tang, "Recent developments in flexible wearable electronics for monitoring applications," Transactions of the Institute of Measurement and Control, vol. 29, no. 3-4, pp. 283-300, July 2016

- [1.2] Wearable Devices [Online]. [Accessed: 12August 2017]. Available from: http://www.wearabledevices.com/what-is-a-wearable-device

- [1.3] J. McCann and D. Bryson, "Smart cloths and wearable technology", First Edition, pp.1, Woodhead Publishing Limited, 2009

- [1.4] NASA [Online]. [Accessed: 22 August 2017]. Available from: https://www.nasa.gov/feature/jpl/space-fabric-links-fashion-and-engineering

- [1.5] I. Locher, "Technologies for system-on-textile integration," Doctoral Thesis (PhD), Swiss Federal Institute of Technology, 2006

- [1.6] J. A. Stankovic, "A Perspective on Distributed Computer Systems," IEEE Transactions on Computers, vol. C-33, no. 12, pp. 1102-1115, December 1984

- [1.7] T. L. Casavant and J. G. Kuhl, "A Taxonomy of Scheduling in General-Purpose Distributed Computing Systems," IEEE Transactions on Software Engineering, vol. 14, no. 2, pp. 141-154, February 1988

- [1.8] A. Burns and A. Wellings, "Concurrency of Ada", Second Edition, pp. 1, Cambridge University press,1999

- [1.9] A. Cerpa and D. Estrin, "Ascent: Adaptive Self-Configuring Sensor Network Topologies", UCLA Computer Science Department Technical Report UCLA/CSD-TR-01-0009, May 2001

- [1.10] A. Lim, "Distributed Services for Information Dissemination in Self-Organizing Sensor Networks", Special Issue on Distributed Sensor Networks for Real-Time Systems with Adaptive Reconfiguration, Journal of Franklin Institute, Elsevier Science Publisher, Vol. 338, pp. 707-727, 2001

- [1.11] K. Van Laerhoven, A. Schmidt, H. Gellersen, "Multi-sensor context aware clothing", Proc. 6th Int. Symp. Wearable Computers, pp. 49-56, 2002

- [1.12] D. Trossen and D. Pavel, "Sensor networks, wearable computing, and healthcare applications," Pervasive Computing, IEEE, vol. 6, no. 2, pp. 58– 61, 2007

[1.13] B. Burchard, S. Jung, A. Ullsperger, and W. D. Hartmann, "Devices, software, their applications and requirements for wearable electronics," ICCE, pp. 224–225, 2001

- [1.14] M. Stoppa and A. Chiolerio, "Wearable Electronics and Smart Textiles: A Critical Review", *Sensors* 2014, Vol. 14, 11957-11992, 2014

- [1.15] Yinka-Banjo Chika, and Salau Abiola Adekunle, "Smart Fabrics Wearable Technology", International Journal of Engineering Technologies and Management Research, Vol. 4, pp. 78-98, 2017

- [1.16] S. I. Woolley, J. W. Cross, S. Ro, R. Foster, G. Reynolds, C. Baber, H. Bristow, and A. Schwirtz, "Forms of wearable computer," in IEE Eurowearable, IET, pp. 47-52, 2003

- [1.17] K. V. Laerhoven, A. Schmidt, and H-W. Gellersen, "Multi-Sensor Context Aware Clothing," in ISWC, IEEE Computer Society, pp.49-56, 2002

- [1.18] C. L. Cathey, J. D. Bakos, and D. A. Buell, "A reconfigurable distributed computing fabric exploiting multilevel parallelism," in FCCM, IEEE Computer Society, pp. 121–130, 2006

- [1.19] A. Lymberis and R. Paradiso, "Smart Fabrics and Interactive Textile Enabling Wearable Personal Applications: R&D State of the Art and Future Challenges," in 30th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, pp. 5270–5273, 2008

- [1.20] Y. Yu, C-L. Hui, T-M. Choi, and R. Au, "Intelligent Fabric Hand Prediction System with Fuzzy Neural Network," IEEE Transactions on Systems, vol. 40, no. 6, pp. 619–629, 2010

- [1.21] Computers in your cloths a milestone for wearable electronics [Online].

[Accessed: 20 February 2018]. Available from: https://news.osu.edu/news/2016/04/13/computers-in-your-clothes-a-milestone-for-wearable-electronics

#### **CHAPTER 2:**

# A NOVEL PARALLEL DISTRIBUTED ARCHITECTURE

THE purpose of the chapter is to consider a series of possible concepts for attaching sensors to processing elements. This chapter will review the state of the art in parallel computer architectures and will identify a suitable architecture for a wearable computer system. The chapter also considers alternative architectures and how they interconnect with the physical local sensors.

#### 2.1 Introduction to Multiple sensors, Multiple Processor Systems

The classification of parallel computer systems is usually based on their constituent hardware components. Once sensors are introduced into the parallel system there are a number of possible options for attaching them to the individual Processing elements.

Suppose that we have a rectangular sensor matrix of N by M sensors, each capturing analogue data with an upper-frequency f and we wish to continuously process data, producing a result. The application area is assumed to require processing of data from multiple sensors. An example of this is contained in a later chapter.

In Concept 1 shown in Fig 2.1 it can be seen that the single Control unit, C, which processes all the sensor data needs to process samples at a rate of 2.N.M.f. That processing may be assisted by specialist hardware on particular processors but ultimately the control unit must handle this and perform its calculations at an appropriate speed.

Figure 2.1: Concept 1 showing Control unit C and Sensors  $S_{n,m}$

Concept 2 shown in Fig 2.2 is similar in terms of performance, however, although the wiring may well be more convenient it uses a shared bus system which may bring additional implementation cost and complexity. The interconnection IN shown in Fig 2.2 could be a bus communication used for the purpose to transfer data.

Figure 2.2: Concept 2 where IN shows an interconnection such as bus

Concept 3 shown in Fig 2.3 has a control unit and many processing elements. All the processing elements are connected to the control unit. The sensors are attached to the processing elements using their own individual buses. Here the processing elements are required to process samples at 2f samples/second and after preprocessing may be subsequently passed to the control unit. However, this offers a limited advantage if the purpose is to process data which involves fusing information from adjacent sensors.

Figure 2.3: Concept 3 showing the inclusion of individual processing elements P

Concept 4 shown in Fig 2.4 has many processing elements. Each processing element is physically connected to the neighbouring processing elements. Every processing element is attached to its own sensors using an individual bus. The processing can be carried out locally at each processing element. Alternatively, the whole network of processing elements and sensors can be thought of as a form a distributed computer unit. This concept has inherent advantages as it means that co-located sensor data can be processed locally and independently by the distributed processors. Selected preprocessed data can also be communicated reducing bandwidth. It is worth emphasising that this is different to a conventional parallel concept because the processing elements are physically spaced out to coincide with their local sensors. Indeed, it may be possible

for the processing elements and sensors to be manufactured as one single integrated circuit. Each one of these integrated units would still be connected by physical bus wires which may be constructed using conductive thread or printed conductive wires on the fabric.

Figure 2.4: Concept 4 showing communication between neighbouring P's

#### 2.1.1 Comparison between the concepts

The advantages and disadvantages of all four concepts are listed in the table below:

**Table 2.1: Comparison between concepts**

| Concept | Advantages                                                                                                                | Disadvantages                                                                                                                               |

|---------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | <ul> <li>Simple architecture.</li> <li>Independent bus connection and no requirement for complex bus protocol.</li> </ul> | <ul> <li>Single control unit handling all the data.</li> <li>Physical wiring for all sensors which returns to the single control</li> </ul> |

|   |                                                                                                                                                                                                                                                                                            | unit.                                                                                                                                                                                 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Fewer physical connections.                                                                                                                                                                                                                                                                | <ul> <li>The bus can only be occupied by a single sensor at any one time.</li> <li>Bus protocol required and sensor addressing must be implemented.</li> </ul>                        |

| 3 | Some pre-processing<br>may be done at the<br>processing elements.                                                                                                                                                                                                                          | <ul> <li>More processing elements required.</li> <li>Depending on the application, it may not be better than concept 1 or 2, where the application requires less sampling.</li> </ul> |

| 4 | <ul> <li>May be able to exploit parallel processing paradigm to achieve improved performance.</li> <li>Scalability may be achievable without reducing computing speed.</li> <li>Buses are between adjacent processing elements and are not all routed back to the control unit.</li> </ul> | <ul> <li>Programmer's model is very complex.</li> <li>Requires selection of suitable parallel processing concept and strategy for the control unit.</li> </ul>                        |

The Concept 4 looks promising as the architecture is distributed and has the potential to have the better performance compared to other concepts. It also has the benefit of

processing the data locally because it will resolve the high bandwidth problem and is not reported in the current literature. For example we can implement an FFT and then just export very small amount of data. This thesis takes the challenge of developing the concept and designing and implementing a wearable system based on this concept. The next section considers parallel architectures which may be suitable for such a system.

#### 2.2 Classifications of Parallel Computer Architectures

Based on major methodologies that were created in the 1960s and 1970s, a wide range of computer architectures have been invented with huge development in VLSI technology over last 30 years. With expanding number of computer architectures, the classification of the architectures should be done efficiently. The classification should be done in such a way that it distinguishes the structures with considerable differences and meantime also discloses the similarities between noticeably divergent designs [2.1].

Various definitions have been proposed for a range of parallel architectures. Many authors have worked on the classification of computer architectures. The most widely accepted classifications among all are Flynn's taxonomy [2.2] which is based on instruction and data stream. One of the disadvantages of Flynn's classification is it does not clearly differentiate between various multiprocessor architectures. Some of these disadvantages from Flynn's classification have been resolved in Duncan's taxonomy [2.3]. These two taxonomies [2.2], [2.3] showing different points of view of parallel architectures have been briefly explained in the next sections.

#### 2.2.1 Flynn's Taxonomy

Flynn's taxonomy, which is one of the earliest classification systems for parallel computers, was developed by Michael J. Flynn in 1966. This classification has been used as a tool in designing modern processors and their functionalities. Flynn mainly used two criteria for the classification of programs and computers, first being whether they were working using a single set or multiple set of instructions and second was whether or not those instructions were using a single set or multiple sets of data [2.1].

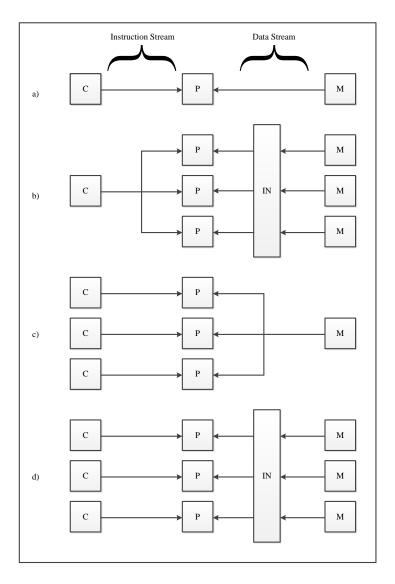

#### 2.2.1.1 Flynn's classification

Based on the presence of either single or multiple streams of instructions and data, four groups according to Flynn's taxonomy are SISD, SIMD, MISD and MIMD. Flynn's classification is briefly described below:

- SISD (Single Instruction Single Data); which mainly describes serial computers.

- SIMD (Single Instruction Multiple Data); which works with multiple processors executing the same instruction simultaneously on different data.

- MISD (Multiple Instruction Single Data); which works with multiple processors

executing different instructions to a single data stream. This is more uncommon

architecture.

- MIMD (Multiple Instruction Multiple Data); which works with multiple processors simultaneously executing multiple instructions on multiple data.

These four categories along with their architectural differences are shown in Fig. 2.5. The major representatives of SISD category are single processor computers. The next one is SIMD category, which includes vector computers as well as array computers. It is also known as synchronous parallelism. MISD is an uncommon category which is even referred as non-existent by various authors. Bräunl [2.4] classified pipeline computers under this category. The last one is MIMD category which includes multi processor distributed computer systems. It is also known as asynchronous parallelism, which is opposite to SIMD.

Flynn's taxonomy provides useful information for characterising computer architectures. Many structures have been found that do not clearly show any of these characteristics and hence do not fit in any of these four groups. So, Flynn's classification became inadequate when it comes to the classification of many modern computers like pipelined processors, systolic arrays, etc. [2.3].

Figure 2.5: Flynn's taxonomy of computer architectures: a) SISD, b) SIMD, c) MISD, and d) MIMD (C: Control unit, P: Processor, M: Memory, I N: Interconnection Network (Bus))

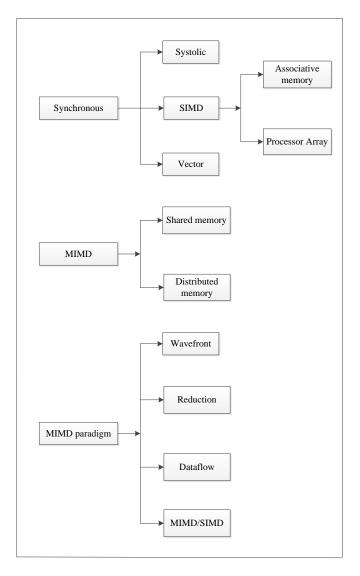

#### 2.2.2 Duncan's classification

The latest architecture innovations were positioned in a broader framework of parallel architectures by Duncan's taxonomy. According to Duncan, the classification should satisfy the following important points [2.3]:

- It should maintain the elements of Flynn's classification based on instruction and data streams;

- It should exclude the architectures which incorporate just a low-level parallel mechanism which has become a general feature of modern computers;

It should include pipelined vector processors and other architectures which intuitively looks as parallel architectures but hard to properly classify under Flynn's taxonomy.

If the above conditions are satisfied, a parallel architecture can be described as a high level, the explicit framework used to develop parallel programming solutions with the help of multiple processors that work together through simultaneous execution to solve the problems. The processors can either be simple or complex.

The classification of processor structures according to Duncan's classification is shown in Fig. 2.6.

Figure 2.6: Duncan's taxonomy of parallel computer architectures

#### 2.2.3 VLSI processor arrays

Most of the architectures are termed as Very-Large-Scale Integration (VLSI) processor arrays. The data is pipelined through the processors simultaneously with processing in systolic arrays and wavefront arrays. Wavefront arrays use data driven potential, whereas systolic arrays utilise local instructions synchronised globally. Both SIMD and MIMD utilise global data and control instead of using pipelined data. It permits broadcasting from a memory and a control unit. The main features of four computer structures are explained briefly in the segment below.

#### 2.2.3.1 SIMD architectures

Normally, the SIMD architectures utilise a central control unit, multiple processors and an interconnection network, which establishes processor-to-processor or processor-to-memory communications. The central control unit broadcasts a single instruction to all processors. The processors, in turn, execute the instruction on local data. The main function of the interconnection network is to communicate the instruction results calculated at one processor to another processor to be used as operands in a subsequent instruction.

#### 2.2.3.2 MIMD architectures

MIMD architectures use multiple processors which execute independent instruction stream utilising local data. These kinds of architectures are capable of supporting parallel solutions, in which processors are required to function in a largely autonomous manner. MIMD architectures are asynchronous computers that are mainly characterised by decentralised hardware control. The software processes executed on MIMD architectures are typically synchronised by either passing messages via an interconnection network or by accessing data stored in shared memory. High-level parallelism is supported by MIMD computers at sub program and task level.

#### 2.2.3.3 Systolic architectures

Kung and Leisserson [2.8] were the first to introduce systolic architectures in 1978. Systolic arrays are typically defined as high-performance, special-purpose VLSI computer systems. They are appropriate for specific application requirements which

require a balance of intensive computations along with demanding input/output bandwidths. Systolic architectures also called as systolic arrays are organised as networks that contain a large number of identical, locally connected Elementary processing elements. Data in systolic arrays is pulsed from memory through processing elements before returning to memory in a rhythmic fashion. The system is synchronised using a global clock and explicit timing delays. For a diverse range of special purpose systems, modular processors united by regular and local interconnections act as basic building blocks. The performance requirements of special-purpose systems are handled using systolic arrays by achieving considerable parallel computations and by avoiding input/output and memory bandwidth restrictions.

#### 2.2.3.4 Wavefront array architectures

Systolic data pipelining and asynchronous data flow execution paradigm, both are combined in wavefront array processors. Wavefront array and systolic architectures, both are designated by modular processors and regular, local interconnection networks. However, in wavefront array architectures, the global clock and explicit time delays used for synchronising systolic data pipelining are replaced with asynchronous handshaking to be used as the mechanism for coordinating inter-processor data movements. So, when a processor is finished doing its computations and wants to pass the data to its successor processor, it sends the data when successor signals that it is ready. An acknowledgement is sent by successor after receiving the data. The computational wavefronts pass smoothly through the array without intersecting using the handshaking mechanism because the processors of the array behave as a wave propagating mechanism. In this way, the correct timing of systolic architectures is replaced by correct sequencing of computations.

#### 2.2.4 Conclusion

After evaluating all the available parallel architectures, the systolic architecture has been chosen as being suitable implementing Concept 4 chosen from the previous section. The systolic mode of parallel processing has gained a tremendous interest due to the elegant exploitation of data parallelism inherent in computationally demanding algorithms from different fields of research. In order to explain a little more about how this can be

applied to a smart fabric system, the fundamental theory behind the systolic arrays will be presented. Research into systolic arrays has been dormant for some years however there is no prior work using these arrays in the physically distributed wearable system. The application that has been chosen to be implemented was human body monitoring thus we need a distributed architecture to implement such an application. There appears to be some potential merit in using systolic array design to implement Concept 4 where a sensor is closely coupled with the processing element.

# 2.3 Systolic Array

The term systolic array in the computer science was introduced in 1978 by Kung et al. [2.8]. Conventionally, a systolic array is made up of a large number of similar processing elements interconnected in an array. The interconnections are local, which means each processing element can communicate only with a limited number of neighbouring processing elements. There are two types of systolic arrays, data systolic array and instruction systolic array.

In data systolic array, the data moves at a constant velocity passing from one processing element to the next processing element. Every processing element performs computations, in this way contributing to the overall processing that is required to be done by the array. Data systolic array is generally called as systolic array.

In contrast to the data systolic array, an instruction systolic array (ISA) is a gridconnected network of very simple computation units (processing elements), which is characterized by the instructions being pumped from a corner in a systolic manner.

Systolic arrays are synchronous systems. The exchange of data between directly communicating processing elements is synchronised using a global clock. The data can only be exchanged at the tick of the global clock. In between two consecutive clock ticks, each processing element performs computation on the data which it has received upon the last tick and then generates the data which is to be sent to neighbouring processing elements at the next clock tick. The processing element is also capable of holding data stored in the local memory of the processing element.

# 2.3.1 Features of systolic arrays

Different authors have given different definitions for systolic arrays. A well-known definition according to Kung and Leiserson [2.8] is:

"A systolic system is a network of processors which rhythmically compute and pass data through the system."

A more reliable definition of systolic arrays is presented in terms of bullet points below. A systolic array can be defined as a computing system having the following characteristics [2.4]:

- **Network:** It is a computing network having a number of processing elements or cells with interconnections.

- **Rhythm:** The data is computed and passed throughout the network in a rhythmic and repetitive manner.

- Regularity: The interconnections between the processing elements are

consistent and regular. The numbers of interconnections for processing

elements does not depend on the size of the problem because the numbers of

interconnections between the processing elements are almost the same for

any size of array.

- **Synchrony:** The execution of instructions and the communication data is synchronised using a global clock.

- **Locality:** The interconnections are local, which means that only neighbouring processing elements can communicate directly with each other.

- Modularity: The network may contain one or more types of processing elements. The systolic array can typically be decomposed into different parts with one processor type, in case there is more than one type of processors.

- Extensibility: The computing network has the feature of being extended indefinitely.

- Pipelineability: All data is transferred using pipelining, which means that at least one delay element (register) is present between each two directly connected combinatorial processing elements.

• **Boundary:** Only processing elements in the network which are at the boundary can communicate with the outside world.

To summarise the characteristics discussed above, it can be seen that a large number of processing elements operate in parallel on different parts of the computational problem. Data enters into the systolic array through the boundary. Once the data enters into the systolic array, it can be used many times before it is output to the outside world. Typically, various data streams flow through the array at constant velocities while interacting with each other in the course of this movement. Meanwhile, processing elements execute one and the same function in a repeated manner. The systolic array does not transfer the intermediate results to the control unit. The control unit and the systolic array carry out the exchange of only the initial data and the final results [2.1].

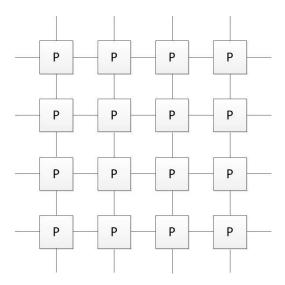

A systolic array is a form of parallel computing method in which the processors are interconnected to each other in the form of a matrix and typically called as cells [2.9]. Each processing element has a special feature that it is capable of storing and computing data independently of other processing elements and eventually processing the data. It can share the information swiftly with its neighbouring processing elements. The major advantage of systolic arrays is that the data can flow in multiple directions. Fig 2.7 shows the general systolic array organisation. In systolic arrays, the input/output rate between the processing elements is generally very high, making them suitable for intensive parallel operations [2.10].

Figure 2.7: General systolic organization

#### 2.3.2 Types of systolic array structures

This section of the chapter discusses the four different types of systolic arrays structures and their applications which are Linear systolic array, Orthogonal systolic array, Hexagonal systolic array and Triangular systolic array.

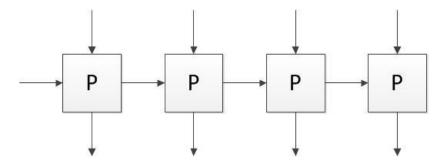

#### 2.3.2.1 Linear systolic array

The processing elements are organised in one dimension in case of a linear systolic array as shown in Fig 2.8. The processing elements have interconnections only with their nearest neighbours. Linear systolic arrays distinguish themselves in terms of a number of data flows along with their relative velocities. One-dimensional convolution (FIR filtering) is one of the representatives of linear systolic arrays [2.1].

Figure 2.8: Linear systolic array

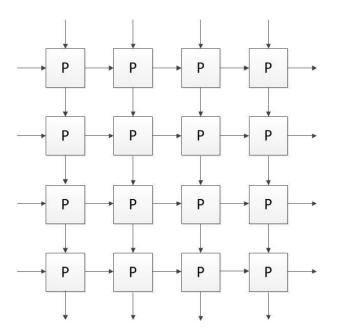

# 2.3.2.2 Orthogonal systolic array

The processing elements are organised in a two-dimensional grid in an orthogonal systolic array as shown in Fig 2.9. Each processing element, in this case, is interconnected to its nearest neighbours in all four directions to the north, east, south and west. The orthogonal systolic arrays differ relative to the number and direction of data flow as well as the number of delay elements organised in them. One of the possible mappings of the matrix multiplication algorithm is the most general representation of this array [2.1].

Figure 2.9: Orthogonal systolic array

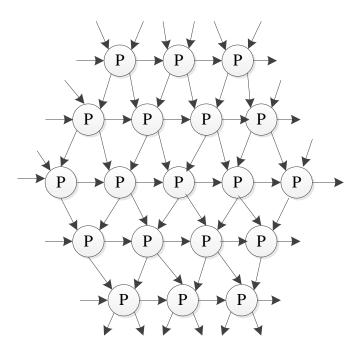

# 2.3.2.3 Hexagonal systolic array

The processing elements are organised in a two-dimensional grid in a hexagonal systolic array as shown in Fig 2.10. The processing elements are connected with their nearest neighbours on six sides where inter-connections have a hexagonal symmetry [2.1].

Figure 2.10: Hexagonal systolic array

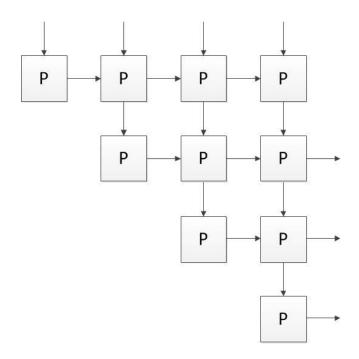

#### 2.3.2.4 Triangular systolic array

The processing elements are organised in a triangular form in a triangular systolic array as shown in Fig 2.11. It is a two-dimensional systolic array. Mostly, this form is used in different algorithms from linear algebra. Particularly, it is more important in Gaussian elimination and other decomposition algorithms [2.1].

Figure 2.11: Triangular systolic array

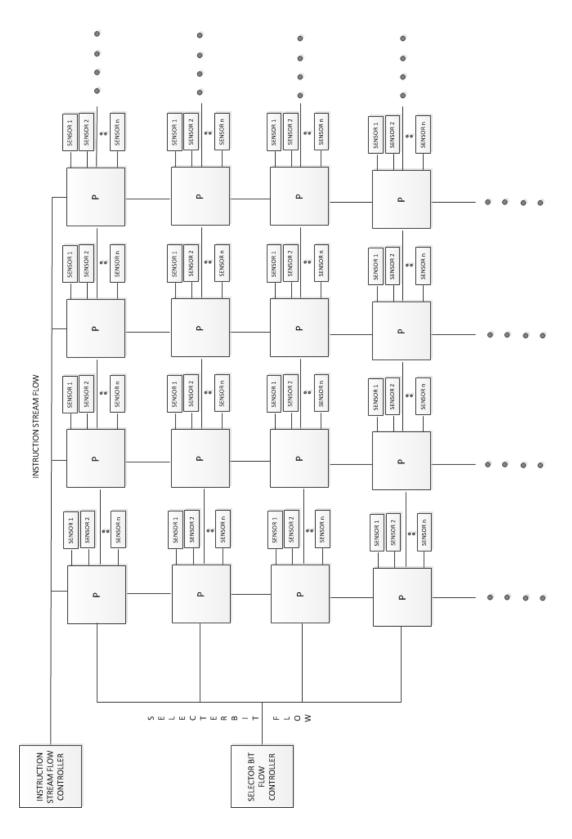

Among various types of systolic array structures, the orthogonal systolic array is assumed as its structure fits body-worn fabrics the best. The orthogonal systolic array has been chosen as the best for wearable applications because of evenly distributed processing elements in the rows and columns which benefits in the diagonal flow of instructions along the array and the array could have a simpler instruction set. Also, the underlying parallel computer model is instruction systolic array, an architectural concept suited for implementing a system with high bandwidth and with architectural benefits for wearable.

# 2.4 The Instruction Systolic Array

Instruction Systolic Array (ISA) is broadly used in VLSI for execution purposes as an architectural concept [2.11], [2.12]. ISA can be viewed as more flexible and advanced from the properties below and are considered chiefly as special purpose architectures.

The important properties of ISA are:

- local communication for data and control flow,

- modularity and scalability

- local data handling

- mapping is logical

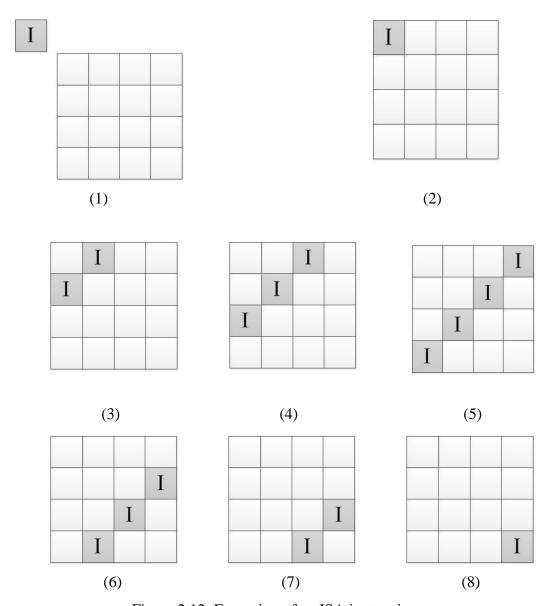

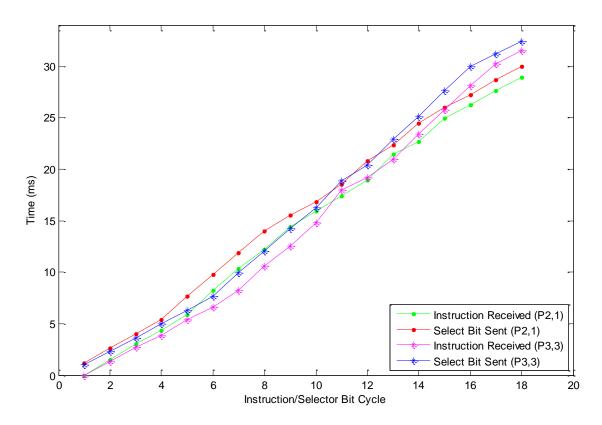

In ISA, rather than data, instructions are pumped in a systolic way through a processor array which makes it different from standard systolic arrays [2.11], [2.13]. This particular arrangement helps in executing different algorithms on the same processor array. Also, the instruction stream and the stream of selector bit both get combined. Due to this, subsets of processing elements can have a very flexible addressing. The fundamental model of a parallel computer can be seen as a mesh connected n x n-array identical processors. The processors are capable of executing instructions from a small instruction set. The processor array is synchronized by a global clock, and each instruction is supposed to take the same time for its execution.

# 2.4.1 Principles of ISA

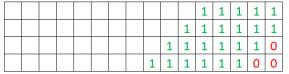

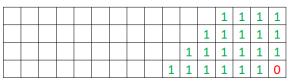

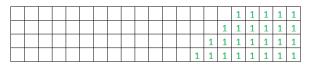

The instructions for the ISA are inputted from the upper left corner of processor array as shown in Fig. 2.12, instruction flow in horizontal and vertical directions through the array step by step [2.12]. This process makes it sure that during each clock cycle, the same instruction is available for execution within every diagonal of the array.

Figure 2.12: Execution of an ISA instruction

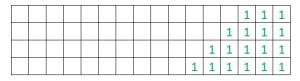

Each processor has some data registers that also includes a designated communication register C. Communication process between two processors, A and B take place in following way:

In [2.12] the concept of data transfer between the processors is explained as for example, a data item is to be sent from processor A to B, first A writes the data item into its own communication register. In the next instruction, B reads the contents from the communication register of A. Each processor is allowed only to write data to its own communication register, but it is allowed to read data from the communication registers of its four direct neighbouring processors. Two or more processors can read the data from same communication register at the same time. To avoid confusion between

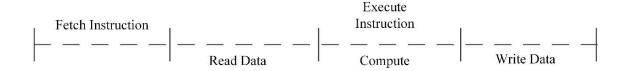

read/write processes, it is arranged so that reading from a register is carried on during the first half of the execution of instruction and writing on a register is carried on during the second half as shown in Fig 2.13.

Figure 2.13: Instruction cycle

The main feature of ISA is that throughout the array, it provides a rhythmic flow of instructions [2.11]. The basic architecture of an ISA is a mesh-connected array of processing elements, and every processing element is capable of executing instructions from a fixed instruction set. The execution of a large variety of algorithms can take place on same ISA. In an ISA, along with the instruction stream, an orthogonal stream of control bits is also used. The execution step for any instruction in processing element takes place only when the selector bit at that processing element is 1. Due to the use of selector bits in execution, the array processor architecture tends to be very flexible. Instructions and selector bits are used for controlling processing elements.

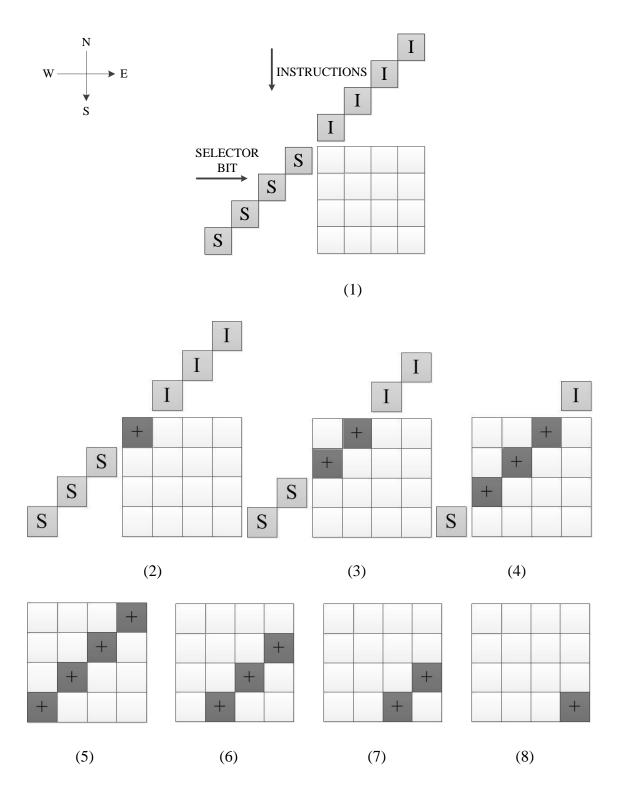

The processors are provided with instructions and selector bits from outside the array. Instructions are input one by one from the upper left processor, and then they move in diagonal wave fronts throughout the array [2.14].

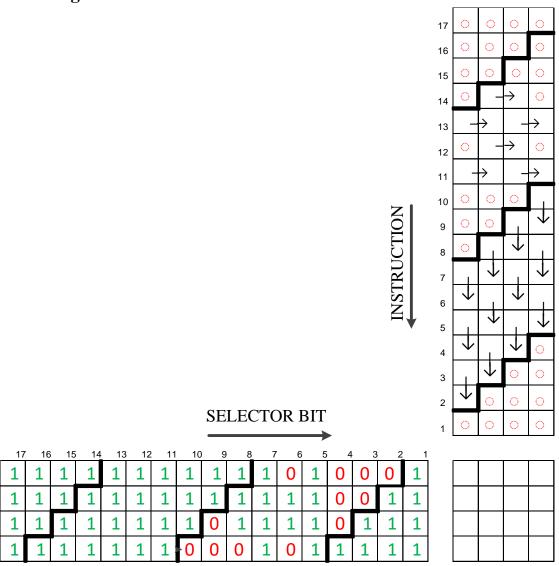

#### 2.4.2 ISA Architecture

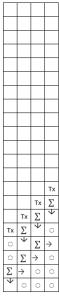

The flow of instructions is generally from top to bottom (north to south) of the array. On the other hand, the selector bit flows from left to right (west to east) of the array. To carry out the instructions at that particular processing element, the selector bits must be 1. Fig 2.14 shows the execution of ISA diagonal.

Figure 2.14: Execution of an ISA diagonal (I - Instruction, S - Selector bit, + - Execution).

The ISA can be thought as more of a pipelined SIMD array. It is still possible to perform broadcast and ring shift operations with a minimum number of instructions even though there are no global wires or wrap-around connections [2.14].

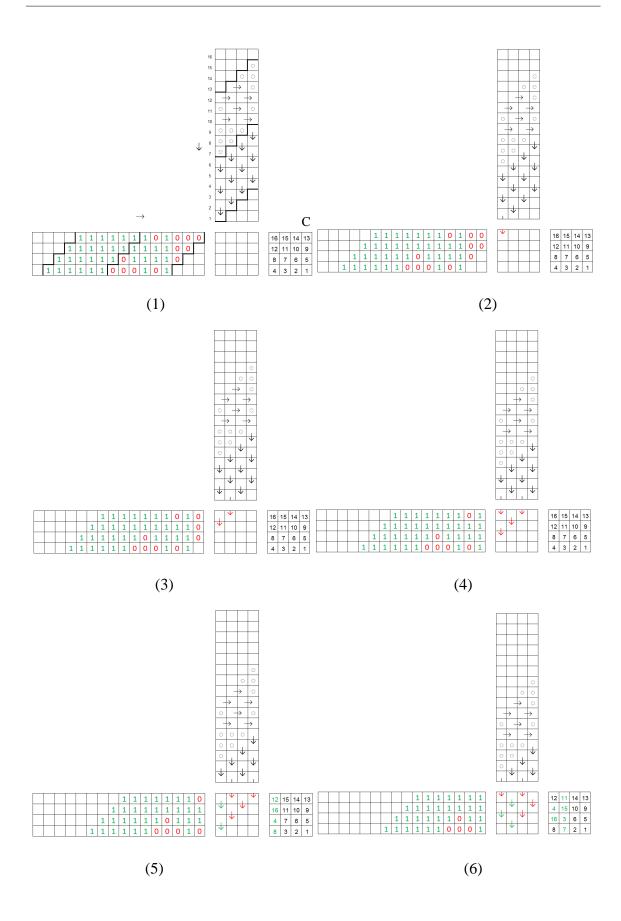

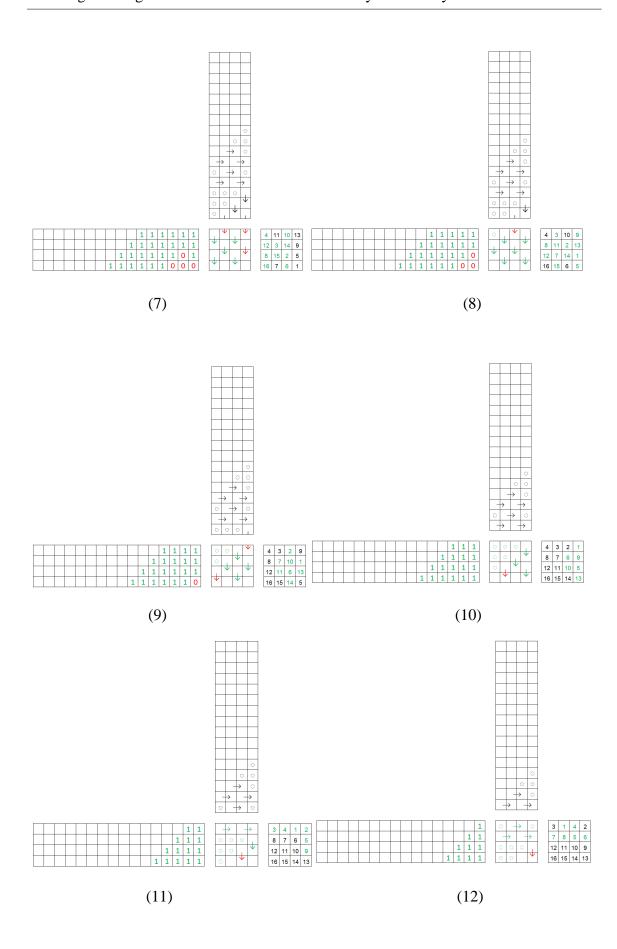

# 2.4.3 Programming and Execution of ISA

Laisa is a Pascal-like programming language used for ISA programs. It supports control structures like conditional statements and loops as well as procedures [2.9]. Basic machine code for the ISA is implemented in LAISA using brackets:

Elementary statements in Laisa are of the form

```

<instruction; selector>

```

Instructions can be register assignments of the form

```

<set source-register, destination-register>

```

or arithmetical or logical operations of the form

```

<instructioncode source-register1, source-register2, destination-register>

```

Registers can be any of the data registers or the communication register C, the communication registers of the western, northern, eastern or southern neighbour CW, CN, CE, CS, respectively [2.16].

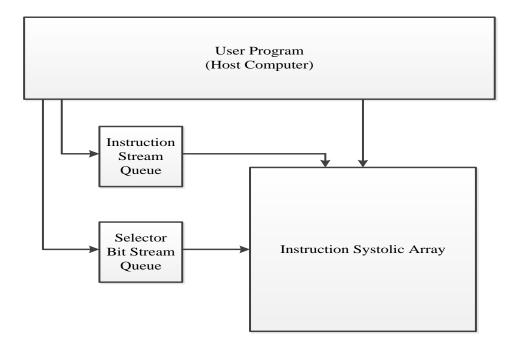

Data is input or output to the processor array is finished via the open-ended processor links present at the boundary of the array [2.9]. The ISA is supposed to be embedded into an environment which is proficient enough to:

- supply ISA with instructions and selectors,

- supply ISA input data and to store its output data.

The key concept is that there should be a communication in between the processors in the form of an array with short interconnections and without the use of any global wires. By using the concept of pipelined execution of instructions in the processor, increases efficiency of the array [2.15].

Figure 2.15: Execution of ISA program

The controller receives its instruction queue and selector bits which are loaded before the execution of an application. The ISA block consists of individual processing elements. The ISA program is loaded into each processing elements on the Instruction systolic array direct from the host computer. The ISA gets its instructions from the ISA program memory. It is also loaded before the execution of the desired application programs. The execution of the programs is started by the flow of instruction and selector bit stream, as indicated in Fig. 2.15.

# 2.4.4 Applications of ISA

The main applications of Instruction Systolic Array are as follows [2.16]:

- Solving problems regarding linear equations in Digital Image Processing (DIP)

- · Computer Graphics

- Cryptography

To summarize, following properties sums up the advantages of ISA architecture [2.16]:

- Broad applicability

- Only local communications for control and data flow purposes

- Fast and parallel computations

• Scalability and modularity

#### 2.5 Adaptation to ISA

Schmidt et al. [2.13] and Sim et al. [2.17] have adapted a different method from the conventional instruction systolic array. To improve the performance of their application they proposed modifying the way in which selector bits are sent from both top and left (north and west). The north will have both instruction and selector bit entering the array. In the present thesis, a similar approach has been taken into consideration. This has the advantages on the performance, simplification of instruction and data loading into the array. The details of this will be explained in chapter 4.

# 2.6 Systola 1024

The first commercial parallel computer based on the ISA architecture [2.18]-[2.20] is Systola 1024 which is shown in Fig. 2.16. The ISA has been integrated for standard personal computers on a low-cost add-on board. A strict co-processor concept has to be followed to operate using this board. By executing corresponding parallel programs on the Systola 1024, the sequential programs can be accelerated by replacing computationally intensive procedures.

Figure 2.16: Systola 1024 from [2.21]

One of the real time applications where ISA is used is in optical surface inspection of coated surfaces. Special measuring methods were needed for this application, which enables quick scanning of large surfaces and avoiding the direct contact to the surface at the same time. For such an application, optical methods combined with digital image processing provide a satisfactory solution. For applications mainly in the sector of machine vision and fast vision, systems provide the required computing power by utilising special image processing hardware or high-power workstations. The major

disadvantage of these systems is the involvement of large budget. The instant outcome is cutting the quality control out of economic reasons, which is the end quality control is generally carried out by human visual inspection.

A low-cost alternative to large budget solutions is developed by ISATEC and is termed as the Surface Quality Scanner (SQS 1024) [2.22]. The combination of a standard personal computer, the Systola 1024 board and low-cost video data acquisition boards, offers to provide a solution for quality control at a competitive price and performance ratio. The Systola 1024 board is used as hardware base for the technology.

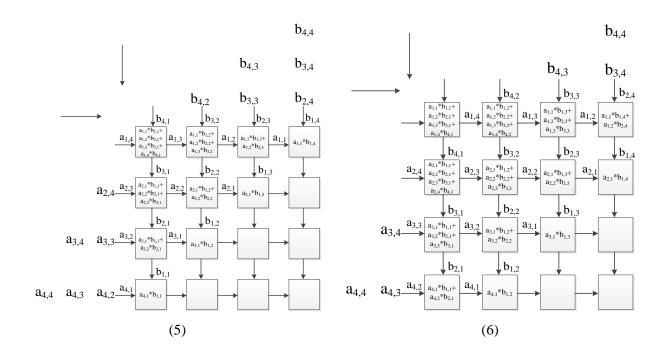

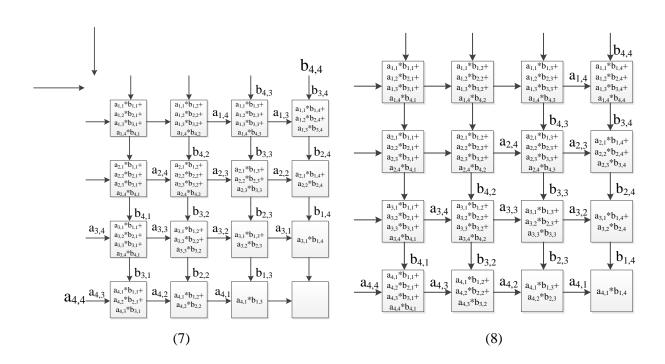

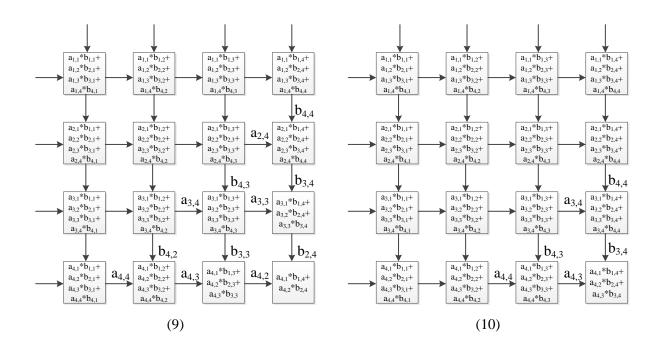

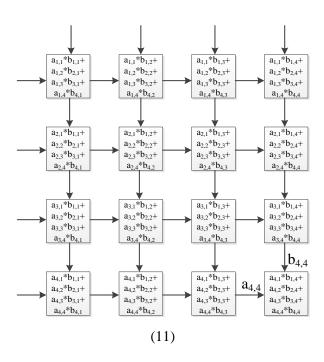

#### 2.7 Conclusion