This item was submitted to Loughborough's Research Repository by the author. Items in Figshare are protected by copyright, with all rights reserved, unless otherwise indicated.

## Animation prototyping of formal specifications

PLEASE CITE THE PUBLISHED VERSION

**PUBLISHER**

© T.S. Hughes

PUBLISHER STATEMENT

This work is made available according to the conditions of the Creative Commons Attribution-NonCommercial-NoDerivatives 2.5 Generic (CC BY-NC-ND 2.5) licence. Full details of this licence are available at: http://creativecommons.org/licenses/by-nc-nd/2.5/

LICENCE

CC BY-NC-ND 2.5

REPOSITORY RECORD

Hughes, Thomas S.. 2019. "Animation Prototyping of Formal Specifications". figshare. https://hdl.handle.net/2134/27241.

This item was submitted to Loughborough University as a PhD thesis by the author and is made available in the Institutional Repository (<a href="https://dspace.lboro.ac.uk/">https://dspace.lboro.ac.uk/</a>) under the following Creative Commons Licence conditions.

C O M M O N S D E E D

#### Attribution-NonCommercial-NoDerivs 2.5

#### You are free:

· to copy, distribute, display, and perform the work

#### Under the following conditions:

Attribution. You must attribute the work in the manner specified by the author or licensor.

Noncommercial. You may not use this work for commercial purposes.

No Derivative Works. You may not alter, transform, or build upon this work.

- For any reuse or distribution, you must make clear to others the license terms of this work.

- Any of these conditions can be waived if you get permission from the copyright holder.

Your fair use and other rights are in no way affected by the above.

This is a human-readable summary of the Legal Code (the full license).

Disclaimer 🗖

For the full text of this licence, please go to: <a href="http://creativecommons.org/licenses/by-nc-nd/2.5/">http://creativecommons.org/licenses/by-nc-nd/2.5/</a>

# BLOSC no: - DX 173557

## LOUGHBOROUGH UNIVERSITY OF TECHNOLOGY LIBRARY

|                     | LIDNANI   |       |

|---------------------|-----------|-------|

| AUTHOR/FILING       | TITLE     |       |

|                     | HUGHES,   | T. S. |

|                     |           |       |

| ACCESSION/COP       | Y NO.     |       |

|                     | 040060543 | •     |

| VOL. NO. CLASS MARK |           |       |

|                     |           |       |

| 2 8 JUN 1996        | LUAN COPY |       |

|                     |           |       |

|                     |           | ·     |

|                     |           |       |

|                     |           |       |

|                     |           |       |

|                     |           |       |

|                     |           |       |

|                     | ,         |       |

|                     | }         |       |

## Animation Prototyping of Formal Specifications

by

T.S.Hughes

A doctoral thesis

submitted in partial fulfilment of the requirements for the award of

Doctor of Philosophy of the Loughborough University of Technology

(1992)

Jeb 93 0400 60543 64923918

#### ANIMATION PROTOTYPING OF FORMAL SPECIFICATIONS.

#### ABSTRACT.

At the present time one of the key issues relating to the design of real-time systems is the specification of software requirements. It is now clear that specification correctness is an essential factor for the design and implementation of high quality software. As a result considerable emphasis is placed on producing specifications which are not only correct, but provably so. This has lead to the application of mathematically-based formal specification techniques in the software life-cycle model. Unfortunately, experience in safety-critical systems has shown that specification correctness is not, in itself, sufficient. Such specifications must also be comprehensible to all involved in the system development. The topic of this thesis - Animation Prototyping - is a methodology devised to make such specifications understandable and usable. Its primary objective is to demonstrate key properties of formal specifications to non-software specialists. This it does through the use of computer-animated pictures which respond to the dictates of the formal specification.

#### The major issues discussed in this thesis are:

- \* The role and presentation of specifications in the development of software for real-time systems.

- \* The applicability of software prototyping, in particular rapid prototyping, to specification techniques.

- \* The basis of formal specification techniques and their use as a software specification method.

- \* The development of a new specification methodology based on a structured application of the Vienna Development Method of software design (defined here as S-VDM).

- \* The development and construction of automated software tools to enable S-VDM specifications to control the behaviour of graphical displays ("animating the specification").

- \* The application of S-VDM for the animation of demonstration systems.

## DEDICATION.

To Josephine.

#### ACKNOWLEDGEMENTS.

The author wishes to thank Dr. Jim Cooling for his dedicated supervision of this work. Without Jim's friendship, patience and understanding this thesis would never have been published. Also the author wishes to thank all the members of the Department of Electronic and Electrical Engineering at Loughborough University for their support, in particular John Rippon and Tim Baseley for their assistance with computing matters. Alan Cuff and his colleagues at Transmitton Limited gave very useful comments and encouragement during early trials of animation prototyping presentations. Finally, on a personal level, thank you to Josephine, my wife, for sustaining me to the end in so many ways.

The generosity of Rolls Royce and Associates of Derby in their support of this work is gratefully acknowledged. Also, the author wishes to thank CACI for the provision of the SIMSCRIPT II.5 package which underpins so much of this work. Finally, but most importantly, thanks to the Science and Engineering Research Council without whose financial support none of this work would have been possible.

### CONTENTS

| ABSTRACT                                               |

|--------------------------------------------------------|

| DEDICATION                                             |

| ACKNOWLEDGEMENTS                                       |

| CONTENTS                                               |

| LIST OF FIGURES                                        |

| LIST OF SYMBOLS                                        |

| 1 INTRODUCTION                                         |

| 1.1 Structure of the thesis                            |

| 1.2 Real-time Embedded Systems                         |

| 1.3 Software Engineering                               |

| 2 SPECIFICATION AND SPECIFICATION ISSUES               |

| 2.1 Introduction                                       |

| 2.2 Specifications in Software Development             |

| 2.2.1 The use of specifications                        |

| 2.2.2 The origin of specifications                     |

| 2.2.3 The writing of specifications                    |

| 2.3 Ways to Improve the Specification Process          |

| 2.4 The Role of Formal Methods in Specification        |

| 2.5 The Role of Animation Prototyping in Specification |

| 3 PROTOTYPING AND ANIMATION OF SPECIFICATIONS 2        |

| 3.1 Software Prototyping                               |

| 3.1.1 Prototypes in engineering                        |

| 3.1.2 Prototyping and the Software Life Cycle          |

| 3.1.3 Prototyping and the Specification Problem 2      |

| 3.1.4 Different Types of Software Prototyping          |

| 3.1.5 Constraints on software prototyping              |

| 3.2 Rapid Prototyping                                  |

| 3.3 Animation Prototyping                            | 27                   |

|------------------------------------------------------|----------------------|

| 3.3.1 An introduction to animation prototyping       | ng 27                |

| 3.3.2 Uses of animation prototyping                  | 29                   |

| 3.3.3 Rapid prototyping techniques and anima         | ation prototyping 30 |

| 3.3.4 Concluding remarks on rapid prototypi          | ng 36                |

| 3.4 Key issues in animation prototyping              |                      |

| 3.4.1 Experience of animation prototyping.           |                      |

| 3.4.2 The model building                             |                      |

| 3.4.3 Using pictures - client-developer comm         | nunications          |

| 3.4.4 Using the results - onward into software       | re design 38         |

| 3.5 Animation Prototyping of Formal Specifications.  | 39                   |

| 3.5.1 The basic concept                              | 39                   |

| 3.5.2 Model building                                 |                      |

| 3.5.3 Style of pictures and discussions              | 39                   |

| 3.5.4 Helping the development of software.           | 41                   |

| 3.6 Summary                                          | 41                   |

| 4 FORMAL SPECIFICATIONS (GENERAL)                    |                      |

| 4.1 Introduction                                     |                      |

| 4.2 Practical Formal Systems for Software Engineerin |                      |

| 4.2.1 Different types of formal systems              |                      |

| 4.2.2 Model-based systems                            |                      |

| 4.2.3 Algebraic or axiom-based systems               |                      |

| 4.2.4 Specifying concurrent systems - Proces         |                      |

| 4.2.5 Temporal and modal logics                      | •                    |

| 4.3 Advantages and Drawbacks of Formal Systems.      |                      |

| 4.3.1 Advantages of formal methods                   |                      |

| 4.3.2 Drawbacks of formal methods                    |                      |

| 4.4 The Final Choice of Formal Method for Animatic   |                      |

|                                                      |                      |

| 5 SPECIFYING SYSTEM REQUIREMENTS USING VDM.          |                      |

| 5.1 Origins of VDM and Current Research              |                      |

| 5.2 Mathematical Foundations                         |                      |

| 5.3 VDM Specifications - describing basic and comp   | • •                  |

| 5.4 VDM Specifications - functions, operations and s |                      |

| 5.4.1 Explicit definitions of functions              | 59                   |

| 5.4.2 Implicit definitions of functions              | 60                   |

|   |        | 5.4.3 States and Operation definitions 61                           |

|---|--------|---------------------------------------------------------------------|

|   |        | 5.4.4 Proofs about states and operations                            |

|   | 5.5    | Building and Refining a Specification                               |

|   |        | 5.5.1 Operation decomposition                                       |

|   |        | 5.5.2 Decomposition into a sequence                                 |

|   |        | 5.5.3 Weakening specifications                                      |

|   |        | 5.5.4 Decomposition into conditionals                               |

|   |        | 5.5.5 Decomposition into loops                                      |

|   |        | 5.5.6 Data reification                                              |

|   | 5.6    | Building and refining a specification - summary                     |

|   |        | •                                                                   |

| 6 | ANIMAT | ING FORMAL SPECIFICATIONS                                           |

|   | 6.1    | Animating Formal Specification - an introduction                    |

|   | 6.2    | Examples of animation systems                                       |

|   | 6.3    | Important Properties of Animation Techniques                        |

|   | 6.4    | Animating Real-Time Embedded Systems - A Conceptual and Theoretical |

|   |        | Framework                                                           |

|   |        | 6.4.1 Introduction                                                  |

|   |        | 6.4.2 Specifying systems using VDM                                  |

|   |        | 6.4.3 Using structure diagrams with specifications                  |

|   |        | 6.4.4 A structuring methodology for specifications 80               |

|   |        | 6.4.5 Diagrams for structuring                                      |

|   |        | 6.4.6 A subset of VDM                                               |

|   |        | 6.4.7 Maintaining consistency in decompositions                     |

|   |        | 6.4.8 Automatic prototype production                                |

|   | 6.5    | Definition of a Subset of the VDM Notation For Use in Real-Time     |

|   |        | Embedded Systems                                                    |

|   | 6.6    | Definition of the Set of States and Data Types                      |

|   |        | 6.6.1 Data types                                                    |

|   |        | 6.6.2 State definition                                              |

|   | 6.7    | Definition of Operations                                            |

|   |        | 6.7.1 The basic elements of an operation specification 84           |

|   |        | 6.7.2 Operation signature                                           |

|   |        | 6.7.3 External clause                                               |

|   | -      | 6.7.4 Pre-condition clause                                          |

|   |        | 6.7.5 Post-Condition Clause                                         |

|   | 6.8    | Definition of the Ordering of Operations 98                         |

| 6.8.1              | Decomposing operations                                        | 88   |

|--------------------|---------------------------------------------------------------|------|

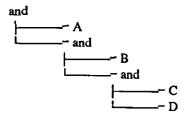

| 6.8.2              | Representing decomposition with diagrams                      | 90   |

| 7 THE ANIMATION    | PROCESS IMPLEMENTATION STRATEGY                               | 96   |

| 7.1 Overview       | of The Animation Process                                      | . 96 |

| 7.2 Parser De      | esign and Implementation                                      | 98   |

| 7.2.1              | The basic design of the parser                                | . 98 |

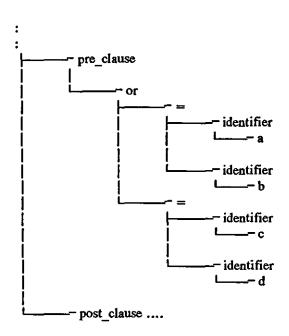

| 7.2.2              | Grammar trees and parsing                                     | 101  |

| 7.2.3              | An example of how the one-track grammar works                 | 102  |

| 7.3 Translation    | on to SIMSCRIPT Source Code                                   | 106  |

| 7.3.1              | General translation strategy                                  | 106  |

| 7.3.2              | Operation translation                                         | 106  |

| 7.3.3              | Post-condition translation                                    | 107  |

| 7.4 Ident          | ification and Implementation of SIMSCRIPT Routines to Support |      |

| Grap               | hics Output                                                   | 112  |

| 7.4.1              | Use of SIMSCRIPT graphical displays                           | 112  |

| • •                |                                                               | 112  |

| 7.4.2              | Updating the main display.                                    | 112  |

| 7.4.3              | Updating local displays                                       | 112  |

| 8 DEMONSTRATIO     | N ANIMATIONS                                                  | 113  |

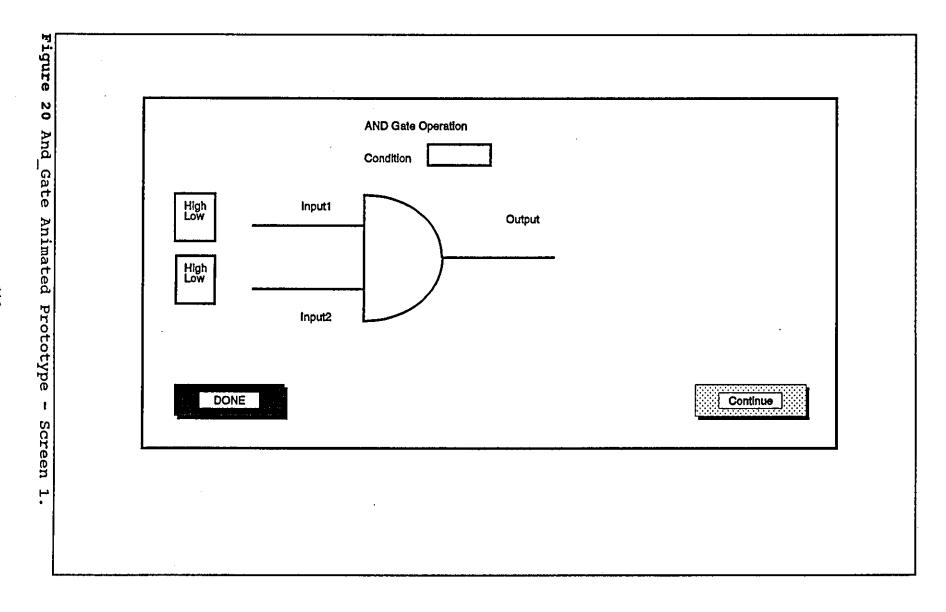

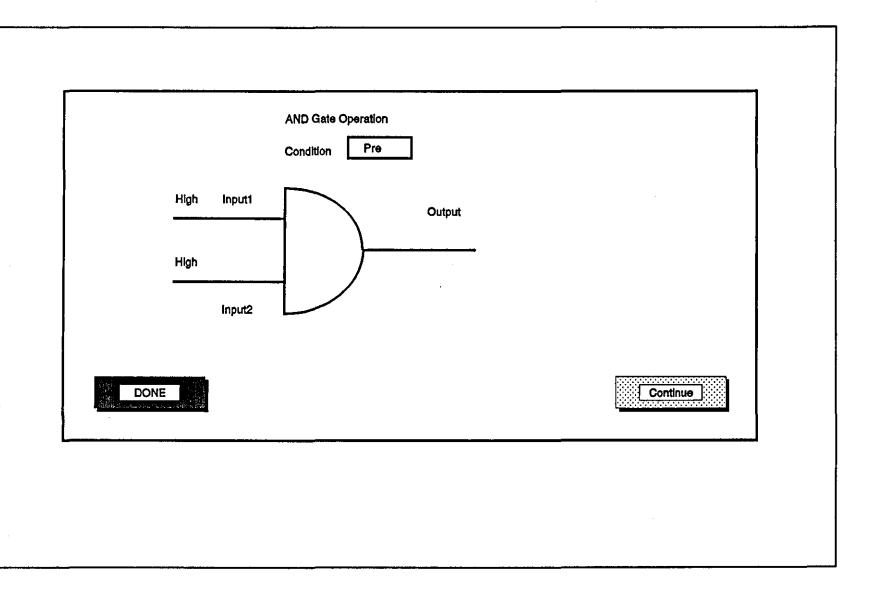

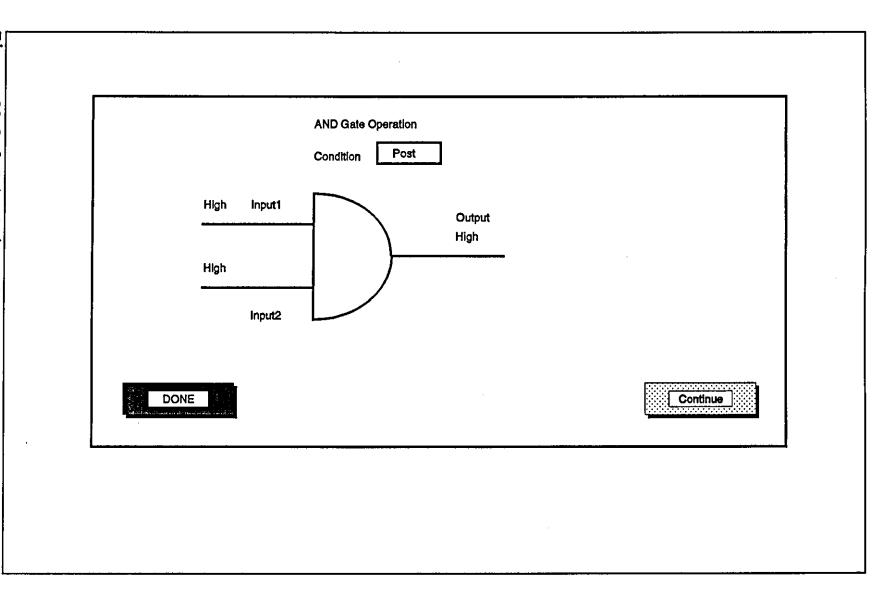

| 8.1 Specifica      | tion and Animation of a Simple Logic Gate                     | 113  |

| 8.1.1              | The purpose of the specification                              | 113  |

| 8.1.2              | Building the specification                                    | 113  |

| 8.1.3              | The stages of the animation prototyping process               | 114  |

| 8.2 Specifica      | tion and Animation of a Plant Controller                      | 120  |

| 8.2.1              | The purpose of the specification                              | 120  |

| 8.2.2              | 2 The formal specification of the system                      | 120  |

| 8.2.3              | Animation prototyping the specification                       | 122  |

| 8.3 Rigorous       | Proofs of Specification Consistency.                          | 123  |

| 8.3.1              | The purpose of proofs                                         | 123  |

| 8.3.2              | 2 Implementability of PlantSequencer                          | 124  |

| 8.3.3              | B Decomposition of PlantSequencer                             | 125  |

| 9 COMMENTS AND     | CONCLUSIONS                                                   | 128  |

| 10 Recommendations | for Future Work                                               | 120  |

| 10.1       | Improvements to tools and their use          | 129 |

|------------|----------------------------------------------|-----|

| 10.2       | Improvements to the formal language.         | 130 |

| 10.3       | More reasoning about time                    | 131 |

| REFERENCE  | ES                                           | 132 |

| APPENDIX A | A                                            | 144 |

| A AN EXPE  | ERIMENT IN ANIMATION PROTOTYPING             | 144 |

| A.1.       | Introduction                                 | 144 |

| A.3.       | Early prototype development                  | 146 |

| A.4.       | Prototype refinement.                        | 147 |

| A.5.       | Final developement                           | 147 |

| A.6.       | Lessons learned                              | 148 |

|            | ·                                            |     |

| APPENDIX   | В                                            | 150 |

| B AN INTR  | ODUCTION TO FORMAL SYSTEMS                   | 150 |

| B.1.       | Introduction                                 | 150 |

| B.2.       | Formal Systems                               | 150 |

|            | B.2.1. Formal Languages                      | 150 |

|            | B.2.2. Semantics - adding meaning to symbols | 150 |

|            | B.2.3. Inference systems                     | 151 |

|            | B.2.4. Proofs and theorems                   | 151 |

|            | B.2.5. Derivations                           | 151 |

| В.3.       | A Simple Example of a Formal System          | 152 |

|            | B.3.1. Propositions                          | 152 |

|            | B.3.2. A formal language for propositions    | 152 |

|            | B.3.3. Semantics for propositions            | 153 |

|            | B.3.4. Propositional calculus                | 156 |

| B.4.       | A More Powerful Formal System                | 160 |

|            | B.4.1. Predicates                            | 160 |

|            | B.4.2. Predicate logic                       | 161 |

|            | B.4.3. A semantics for predicate logic       |     |

|            | B.4.4. Predicate calculus                    | 162 |

| D 5        | C                                            | 160 |

| APPENDIX C.                                               | 165 |

|-----------------------------------------------------------|-----|

| C MATHEMATICAL DETAILS OF VDM                             | 165 |

| C.1. Defining Data Types                                  | 165 |

| C.1.1. Simple data types                                  | 165 |

| C.2. An example implementability proof                    | 168 |

| C.3. A Simple Plant Controller.                           | 174 |

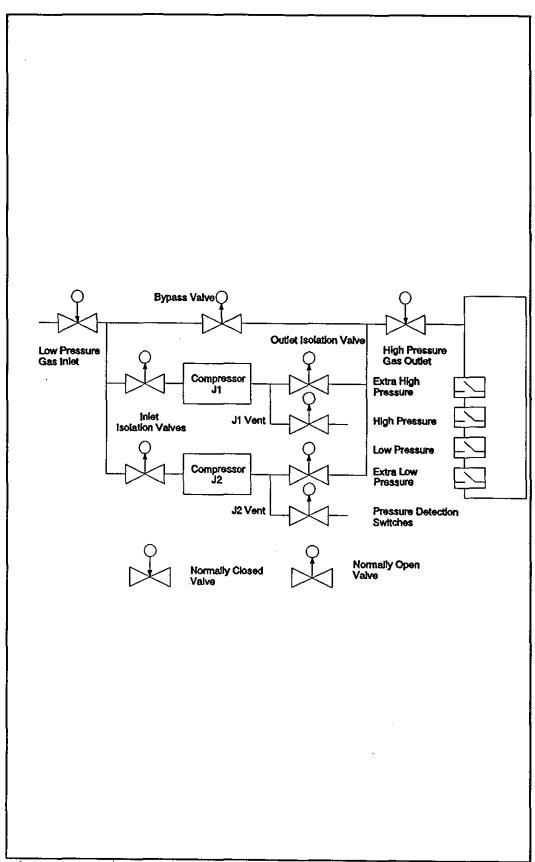

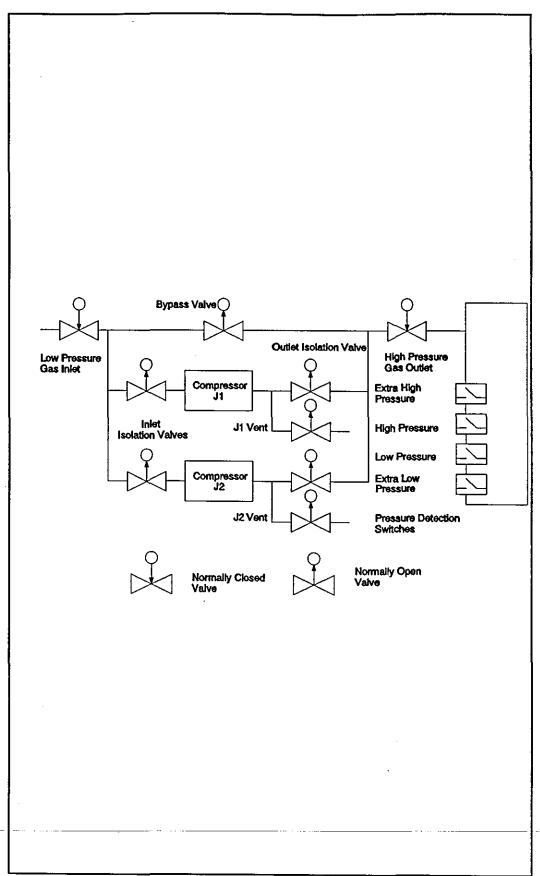

| C.3.1. Informal specification of the system               | 174 |

| C.3.2. Formal specification of the system state           | 175 |

| C.3.3. Formal specification of the plant controller.      | 175 |

| C.3.4. Decomposing the plant controller operation         | 176 |

| C.3.5. Decomposing the Service operation                  | 178 |

| C.4. An Example of Decomposition into Conditionals        | 180 |

| C.5. Two Examples of Decomposition into Loops             | 183 |

| C.5.1. The inference rule for decomposition into loops    | 183 |

| C.5.2. A simple example of decomposition into loops       | 183 |

| C.5.3. A more problematic example involving loops         | 186 |

| APPENDIX D                                                | 188 |

| D IMPLEMENTABILITY PROOF FOR A SIMPLE LOGIC OPERATION     | 188 |

| D.1. The Function and its Specification                   | 188 |

| D.2. The Implementability Proof                           | 188 |

| APPENDIX E                                                | 192 |

| E. EBNF DESCRIPTION OF THE PROJECT'S FORMAL NOTATION      | 192 |

| E.1. Names and Literals.                                  | 192 |

| E.2. Types                                                | 192 |

| E.3. Expressions.                                         | 192 |

| E.4. Statements                                           | 193 |

| E.5. Definitions                                          | 193 |

| APPENDIX F                                                | 195 |

| E THE CRAMMAD TREE FOR THE DARRING OF THE FORMAL NOTATION | 105 |

| APPENDIX G        |                                               | 204 |

|-------------------|-----------------------------------------------|-----|

| G. ANIMATION PROT | TOTYPE OF A LOGIC GATE                        | 204 |

| G.1. Statement    | of Requirements for the Logic Gate            | 204 |

| G.2. Formal S     | pecification of the Logic Gate                | 204 |

| G.3. Animation    | n Code Produced by the Animation Process      | 205 |

| APPENDIX H        |                                               | 209 |

| H. THE NITROGEN/I | HYDROGEN COMPRESSOR PLANT                     | 209 |

| H.1. The State    | ement of Requirements                         | 209 |

| H.2. A Formal     | 1 Specification of The Plant Operation        | 213 |

| H.2.1.            | State and type specification                  | 213 |

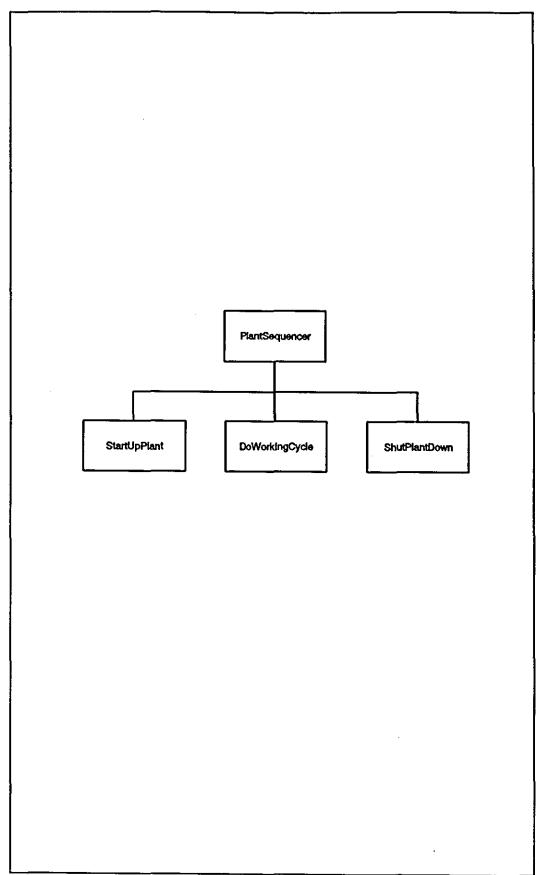

| H.2.2.            | Specification structure                       | 215 |

| H.2.3.            | Specification of the operation PlantSequencer | 217 |

| H.2.4.            | Specification of the operation StartUpPlant   | 219 |

| H.2.5.            | Specification of the operation DoWorkingCycle | 222 |

| H.2.6.            | Specification of the operation ShutPlantDown  | 226 |

| H.3. Animatio     | on Code Produced by the Animation Process     | 229 |

| Н.3.1.            | Preamble and state initialisation             | 229 |

| Н.3.2.            | Routine PlantSequencer                        | 231 |

| Н.3.3.            | Routine StartUpPlant                          | 234 |

| H.3.4.            | Routine DoWorkingCycle                        | 238 |

| H.3.5.            | Routine ShutPlantDown                         | 242 |

| Н.3.6.            | Routine Tim. Update. Display                  | 245 |

| Н.3.7.            | Adding animated graphical displays            | 251 |

| нзя               | Further decomposition of the specification    | 263 |

#### LIST OF FIGURES

| Figure 1 A Real-Time System                                   |

|---------------------------------------------------------------|

| Figure 2 The Software Development Lifecycle                   |

| Figure 3 Two Views of a Real-Time System                      |

| Figure 4 A Simple Model of SOR Interpretation                 |

| Figure 5 Watkin's Classification of Prototyping               |

| Figure 6 Ratcliff's Classification of Prototyping             |

| Figure 7 Schneider's Classification of Prototyping            |

| Figure 8 A Scheme for Rapid Prototyping                       |

| Figure 9 The Gap Between Client and Specifier                 |

| Figure 10 Three Key Aspects of Animation Prototyping          |

| Figure 11 Animation Prototyping of Formal Specifications      |

| Figure 12 Stepwise Refinement of a Formal Specification       |

| Figure 13 Decomposing an Operation                            |

| Figure 14 Using Diagrams to Represent Operation Decomposition |

| Figure 15 Associating VDM Text with Diagrams - Ideal Method   |

| Figure 16 Associating VDM Text with a Single Operation        |

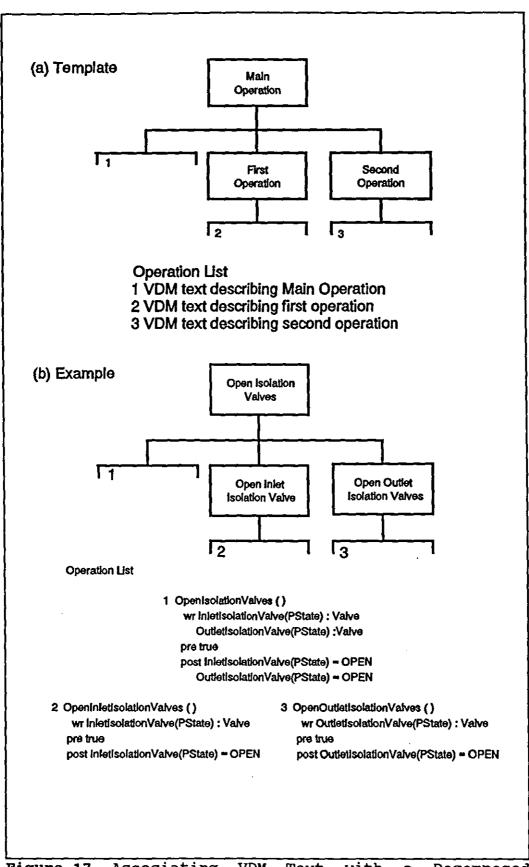

| Figure 17 Associating VDM Text with a Decomposed Operation    |

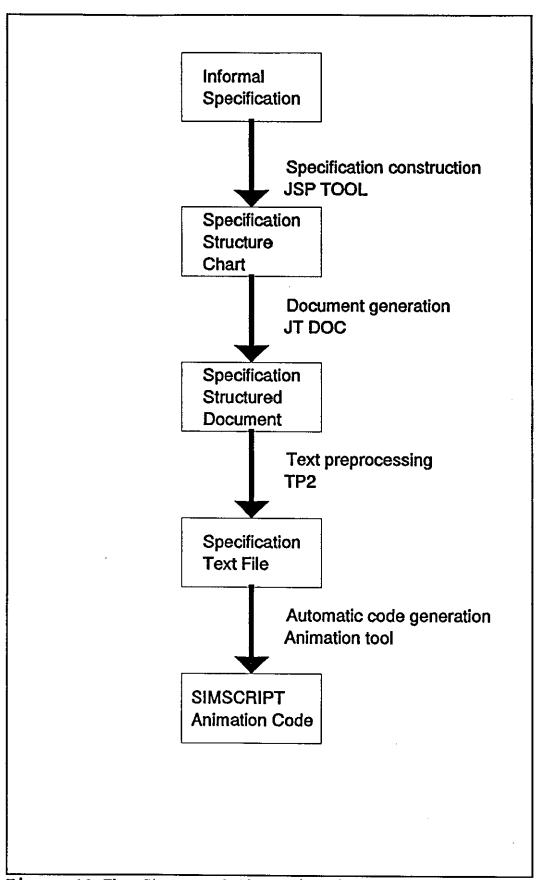

| Figure 18 The Stages of the Animation Process                 |

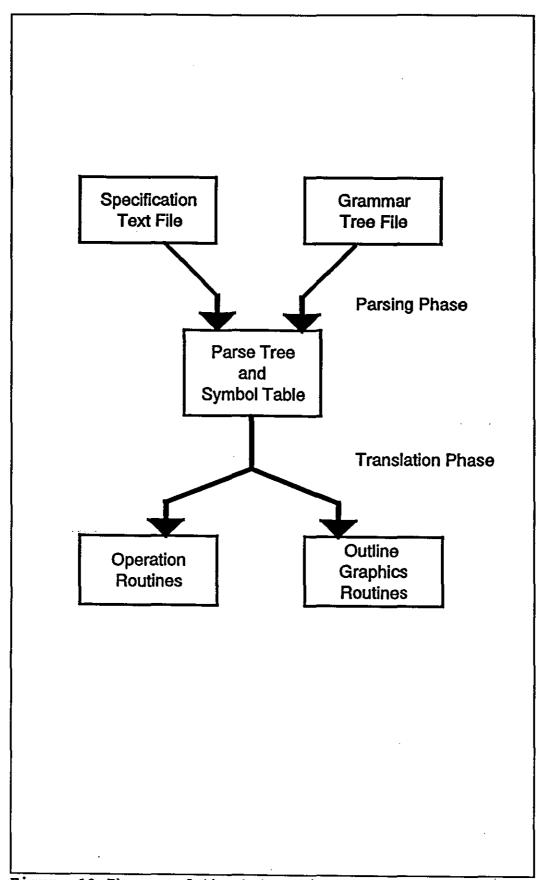

| Figure 19 Phases of the Automatic Code Generation             |

| Figure 20 And_Gate Animated Prototype - Screen 1              |

| Figure 21 And_Gate Animated Prototype - Screen 2              |

| Figure 22 And_Gate Animated Prototype - Screen 3              |

| Figure 23 Plant Schematic                                     |

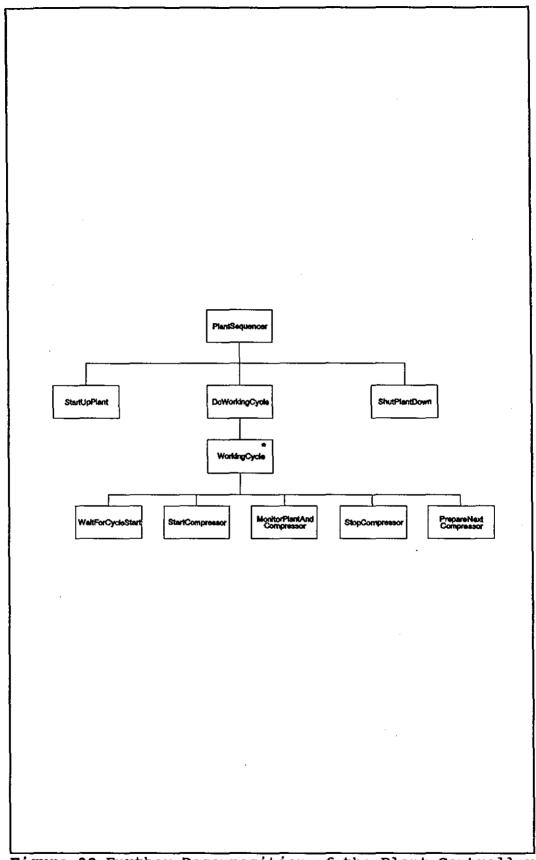

| Figure 24 Structure Diagram of the Plant Specification        |

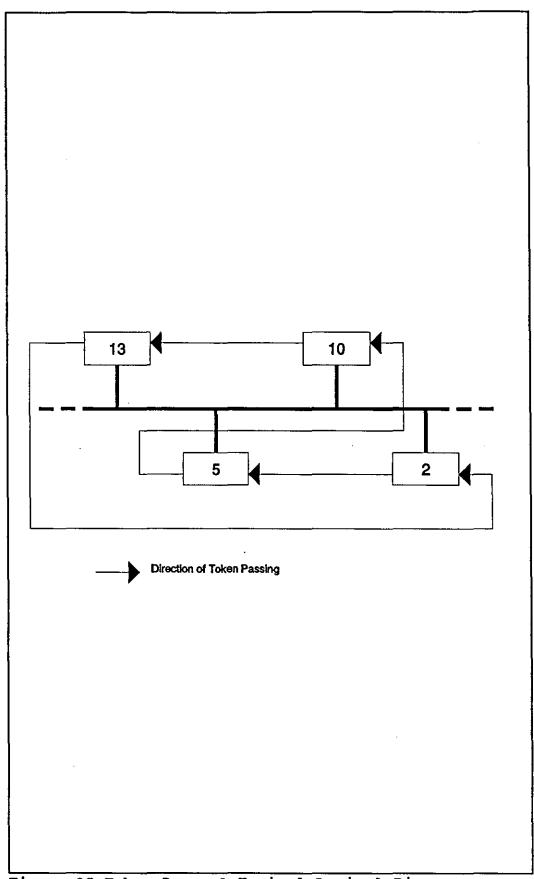

| Figure 25 Token Bus - A Typical Logical Ring                  |

| Figure 26 Plant Schematic                                     |

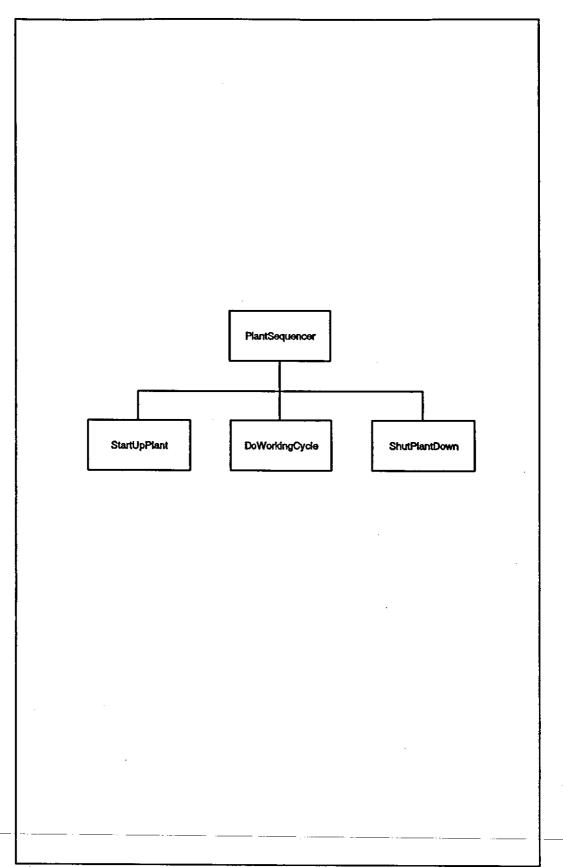

| Figure 27 Structure of the Plant Controller Specification     |

| Figure 28 Plant Controller - PlantSequencer 1                 |

| Figure 29 Plant Controller - PlantSequencer 2                 |

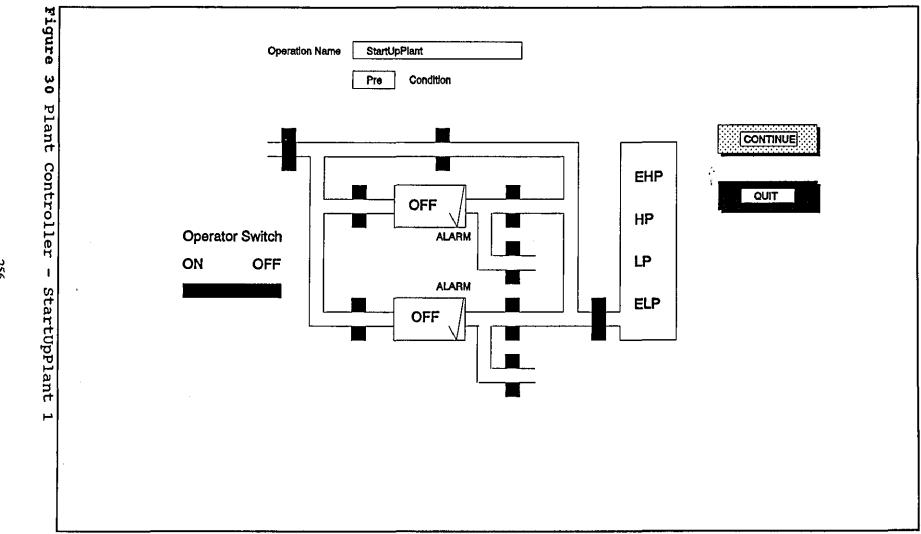

| Figure 30 Plant Controller - StartUpPlant 1                   |

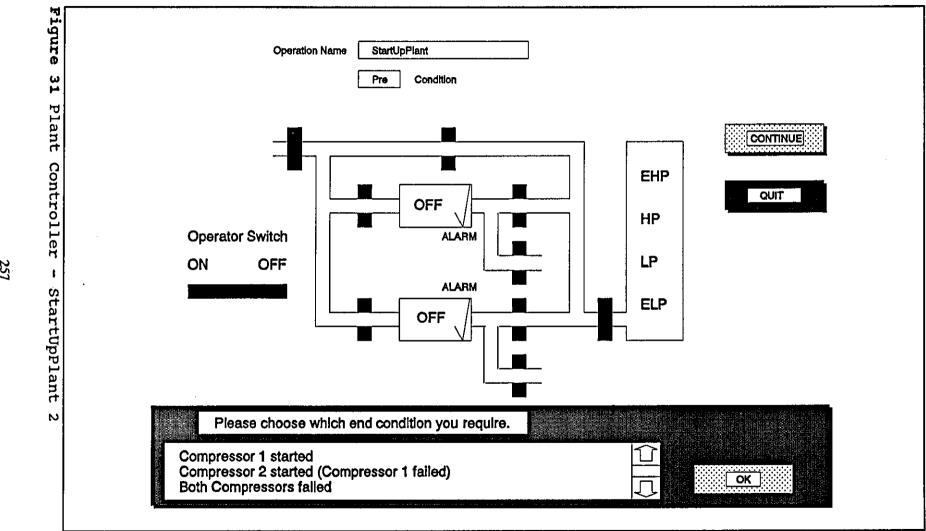

| Figure 31 Plant Controller - StartUpPlant 2                   |

| Figure 32 Plant Controller - StartUpPlant 3                   |

| Figure 33 Plant Controller - DoWorkingCycle 1                 |

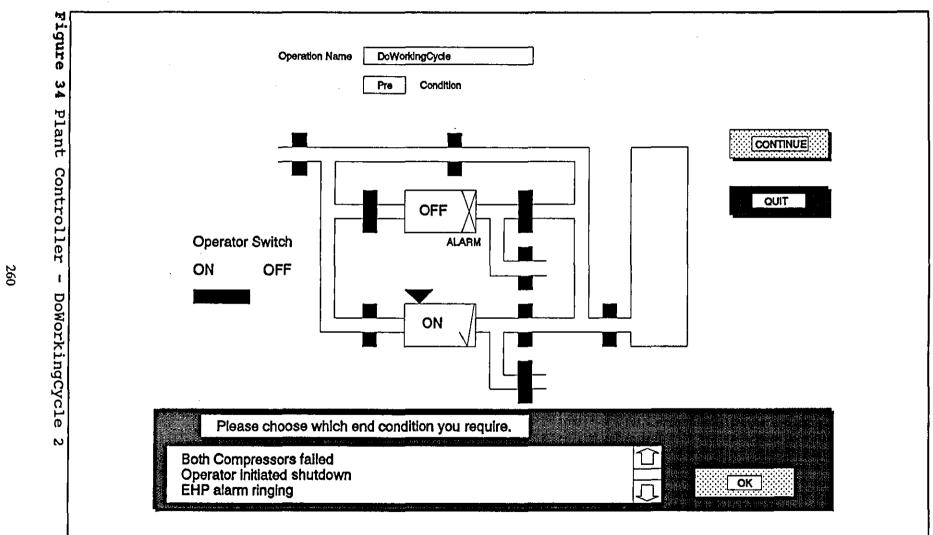

| Figure 34 Plant Controller - DoWorkingCycle 2                 |

| Figure 35 Plant Controller - DoWorkingCycle 3                 |

| Figure 36 Plant Controller - ShutPlantDown 1 |                          | 26  |

|----------------------------------------------|--------------------------|-----|

| Figure 37 Plant Controller - ShutPlantDown 2 |                          | 262 |

| Figure 38 Further Decomposition of the Plant | Controller Specification | 26  |

#### LIST OF SYMBOLS.

<u>P</u>

- Logical Not. The negation of a sentence can be thought of as the logical opposite of that sentence.

- $\wedge$  Logical And. The sentence  $P \wedge Q$  is referred to the conjunction of P and Q. P and Q are conjuncts of the sentence.

- V Logical Or. The sentence  $P \vee Q$  is referred to as the disjunction of P and Q. P and Q are disjuncts of the sentence. The truth value of the sentence is "P or Q or both P and Q". It is also referred to as inclusive or.

- Logical Implication or "if ... then ... ". The sentence  $P \Rightarrow Q$  is read as P implies Q. Care is needed in the informal interpretation of this connective as, in programming terms, there is no information covering "otherwise" or "else". Implication should always be referred to truth tables for exact interpretation.

- $\Leftrightarrow$  Logical Equals. This connective is also referred to as double implication. The sentence P  $\Leftrightarrow$  Q is true if and only if P and Q have the same truth value.

- The universal quantifier. Universal quantification is used to express propositions of the form "every object has this property" or "all objects are related in this way", e.g.

$$\forall x \cdot P(x)$$

The existential quantifier. Existential quantification is used to express propositions of the form "there is at least one object which has this property", e.g.

$$\exists x \cdot P(x)$$

- The syntactic turnstile. If there is a derivation from P to W one can write  $P \vdash W$ .

- The semantic turnstile. The statement P W can be paraphrased as, given a set of assumptions P are true then W is also true.

C An Inference rule. The meaning of this is that if all the sentences, P, above the line are given then the sentence below the line, C, can be deduced as an immediate consequence.

- B The set of boolean values, i.e. { true, false }.

- Z The set of integer numbers.

- N The set of natural numbers, positive integers (including zero).

- N<sub>1</sub> The set of natural numbers, strictly positive integers (excluding zero).

- R The set of real numbers.

- Set membership, e.g.  $x \in Z$  denotes that x is a member of the set of integers.

- {..} A set of values.

- { 1, 2, 4 }

Set enumeration.

$$\{n \in \mathbb{N} \mid 1 \le n \le 5\}$$

Set comprehension.

→ The mapping operator, e.g. s→123 denotes that s "maps to" 123.

$$\{1 \mapsto x_1, 3 \mapsto x_4\}$$

Map enumeration.

$$\{x\mapsto x^2\in\mathbb{N}\times\mathbb{N}\mid x\in\{i\in\mathbb{N}|-2\leq i\leq 3\}\}$$

Map comprehension.

- [..] A sequence of values.

- [12,14,93]

Sequence enumeration.

$$doubles = [x \in \mathbb{N} \mid doubles(x) = 2 \times x]$$

Sequence comprehension.

- T Sequence comprehension. The member of the sequence are drawn from the type T.

- Sequence concatenation, e.g.  $[1,2]^{3,4}=[1,2,3,4]$ .

- V:T Type definition. Variable V is of type T.

- △ "Is defined as".

- $D\rightarrow R$  Function mapping from domain D to range R.

- $A \times B$  The cartesian product of A and B.

$\{P\}Q\{R\}$

A triple. Where P and R are truth valued expressions and Q is some operation. This notation asserts that if the state satisfies expression P then the application of operation Q will yield a state which satisfies the expression R.

#### 1 INTRODUCTION

#### 1.1 Structure of the thesis

The central consideration of this thesis is the involvement of people in developing software for safety-critical, real-time systems. In particular, it considers how these people can accurately specify this type of system. After considering the background to this process, a new technique called animation prototyping is introduced.

In order to establish the practical applications of this technique, it is necessary to look at the type of systems at which the technique is aimed and where in the development process it is to be used. These ideas are considered in detail later in this chapter.

Chapter 2 discusses the idea of systems specifications in detail. By considering how specifications are written and what they are used for a list of useful properties for specifications and their development is suggested. The specific concerns of this thesis are:

- \* The pitfalls in the translation of client-written requirements into developer written specifications;

- \* The development of safety-critical real-time systems from these specifications.

A brief introduction to formal methods is given. This highlights why formal methods are useful in this work.

Chapter 3 introduces the idea of software prototyping. This is a diverse field and the emphasis is placed on techniques useful for the early stages of software development.

The approach to prototyping that is used here has two main strands; firstly the use of formal specification techniques and second the use of animated pictures to aid the discussion and improvement of the specifications thus written. Formal specifications are used for many reasons but above all because they provide a concrete result at the end of the prototyping effort. Animated pictures are used because they provide a more familiar medium for discussions than the mathematic formulae of the formal specification.

Chapter 4 describes what formal methods are and how they are used. It includes an overview of different techniques. The impact of the techniques on the specification process is discussed. There are still problems with an approach based solely on these techniques and these are discussed. The choice of one particular method for this work, called the Vienna Development Method or VDM, is explained. Also the idea of animation prototyping of formal specifications is introduced.

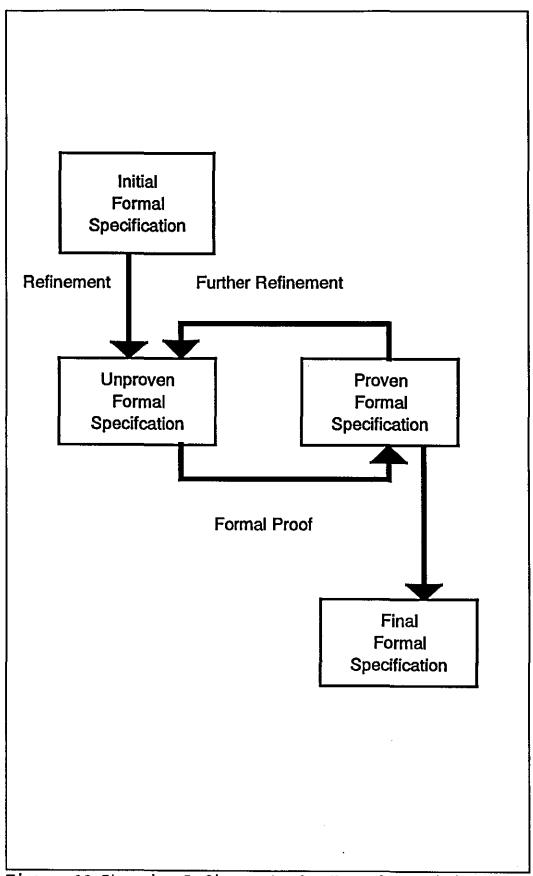

Chapter 5 gives a more detailed description of the Vienna Development Method. Particular emphasis is placed on the structure of specifications written in this style. The mathematical manipulations called proofs are one of the central features of formal methods. The purpose and results of these proofs are shown. The need for animation prototyping when using formal specifications is again shown.

Having seen the need for animation prototyping of formal specifications, chapter 6 gives a detailed description of the background issues to the development of a demonstration prototyping tool. A new specification methodology based on a structured application of the Vienna Development Method of software design (defined here as S-VDM) is shown. Also, the requirements for automated software tools to enable S-VDM specifications to control the behaviour of graphical displays ("animating the specification") are established. Finally, a diagrammatic technique for showing the structure of S-VDM specifications is also defined.

Chapter 7 shows how the implementation of the tool was achieved. This chapter shows the process of creating an animation prototype from the formal specification.

Chapter 8 gives a description of a number of animation prototypes which were built. The practical application of S-VDM for specification is shown. The animation prototyping process and the use of tools is also illustrated.

A summary of the ideas in the thesis and the scope for future work is given in chapters 9 and 10.

#### 1.2 Real-time Embedded Systems

In order to understand the thesis presented here better it is necessary to address two questions; what sort of systems are being developed and how does that affect the development approach?

The characteristics of real-time embedded systems set them aside from many other types of systems. In these systems the correct functioning of the system is dependent on the timing of data input and output as well as the values of the data. Although computer programs are at the heart of such systems the correct performance of the system as a whole depends equally on the external non-computer

hardware in the system. In general real-time systems gather information from external sensors and then exert an influence through external devices. Examples of real-time embedded systems are chemical plant control [Williams87], windtunnel control [Williams84], astronomical data acquisition [Kelton84], fighter plane control [Kaplan85], space shuttle control [Carlow84], radar applications [Fathi84] and amusement park ride control [Nelson81].

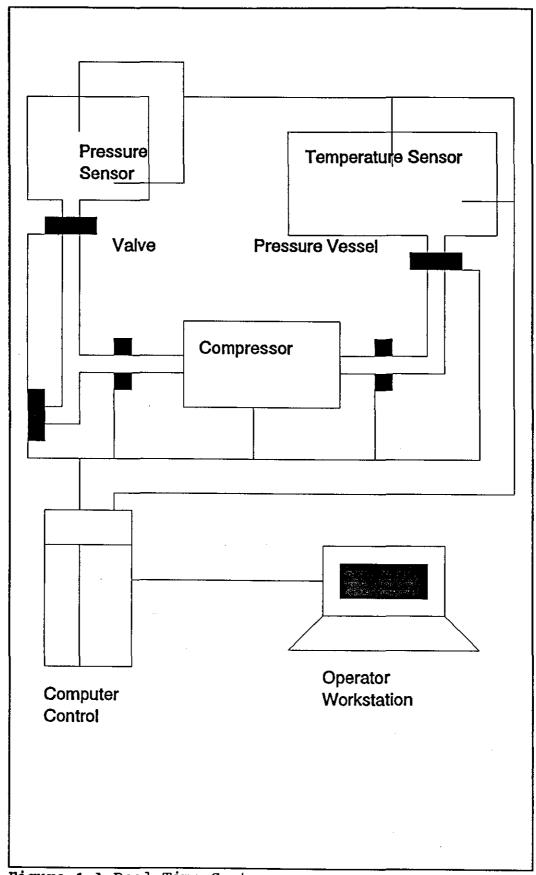

Consider the chemical plant controller shown in Figure 1. This includes such diverse elements as the computer electronics, pressure sensors, temperature sensors, valves, pipes, pressure vessels, gas compressors and operator displays and controls. So in real-time systems there is a complex relationship between the hardware and software: with the software forming only a small part of the whole.

Let us take a closer look at some of the terms which are used to describe and classify real-time systems. The first and most obvious property of real-time systems is that they have deadlines; certain tasks performed by the systems must occur at particular times. The nature of these deadlines divides real-time systems into two groups. In the first group are systems where the failure to meet a deadline is inconvenient but not catastrophic. Systems such as this are called soft real-time systems. Examples are airline registration systems and CAE graphics systems. The second group of systems have rigid deadlines, hence the name hard real-time systems. In these systems failure to meet a deadline will lead to serious or catastrophic results. The high pressure chemical plant shown in Figure 1 is an example of this type of a hard real-time system.

Within the class of real-time systems there is a sub-class of systems with which this work is especially concerned; that of safety-critical systems. These are systems where failure of the system can endanger people's lives. Such systems include aircraft flight systems, nuclear plant controllers and high pressure chemical plant controllers. Current software engineering practice for such systems places severe restrictions on the style of software which maybe employed. These restrictions are that:-

- \* All programs are strictly sequential;

- There use of interrupts is forbidden;

- \* All Input devices, including timers, are polled.

Having outlined the systems which are of interest here, safety-critical embedded real-time systems, let us consider how software for these systems is developed.

#### 1.3 Software Engineering.

Figure 1 A Real-Time System.

Pomberger in his book [Pomberger84] defines software engineering as follows:

"Software engineering is the practical application of scientific understanding to the economical production and use of reliable and efficient software."

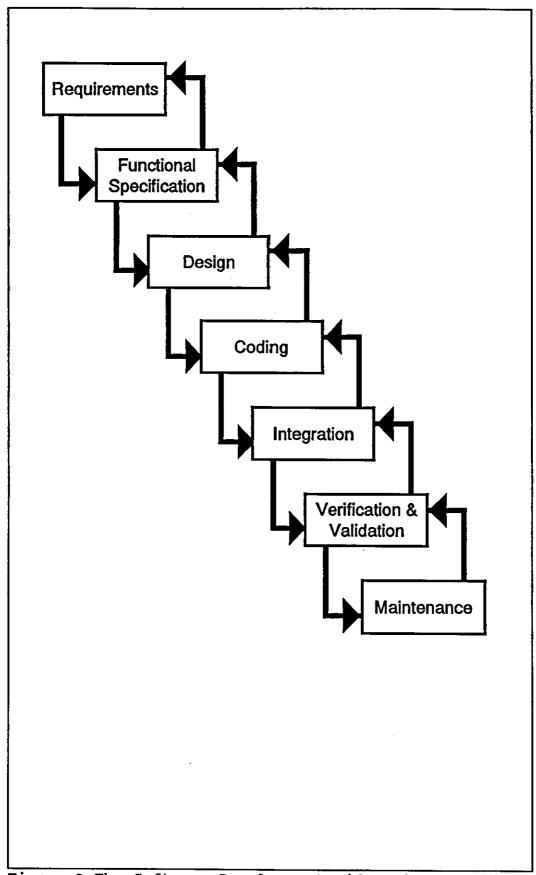

The waterfall model of software development [Royce70, Boehm76] has been a popular model and it does give a useful basis for discussion. The model is shown in Figure 2. The work done at each stage is as follows:-

- \* Requirements specification. The problem to be tackled and goals of the project are specified.

Documents are produced detailing what problems are to be addressed and constraints such as cost and timescales.

- \* Functional specification. Decisions are made as to what needs to be done in order to meet the project goals.

- \* Design. Decisions are made as to how different sub-systems will function together and what tasks each sub-system will perform.

- \* Coding. This is when the actual code is produced. Detailed design of sub-systems may also be a prelude to the coding of that sub-system. Sub-systems will also be tested against their functional specification.

- \* Integration. This is where the individual sub-systems are brought together to form the complete system. Eventually the system as a whole will be tested.

- \* Verification and Validation. Verification is checking the whole system to see if it fulfils is functional specification. Validation is checking the whole system to see if it matches the original requirements of the user.

- \* Maintenance. This is the process of modifying the system to meet the requirements of the user. This means correcting bugs not found during the development, adapting the software to cope with a changing environment and improving the performance of existing features.

There has been a great deal of criticism of this view of software development [McCracken82, Zave84, Boehm88, Luqi88, Maude91]. The major criticisms are:-

Figure 2 The Software Development Lifecycle.

- The lack of feedback between the individual stages.

- \* The lack of early feedback on accuracy of requirements.

- \* The indistinct boundaries between specifications and implementations.

- \* The flexible nature of requirements as project progresses.

The most serious of all these criticisms is the lack of early feedback on the accuracy of the requirements. If the requirements are not accurate then all subsequent development will achieve is to produce a system (possibly of high quality software) that performs the wrong set of tasks. A related problem is the correct interpretation of requirements to produce a specification. These ideas are considered more fully in chapter 2.

As has already been stated the communication of ideas is seen as central to this work. Between each of the above stages there is a flow of information. It is important to ask questions about this information such as:-

- \* Who is involved in the process?

- \* What information do they need?

- \* Who has this information?

- \* To who else is the information useful?

- \* How can the information be exchanged between parties?

- \* How can parties check each others view of the information?

- \* How can the information gathered best be passed on to subsequent stages of development?

Subsequent chapters show how animation prototyping of formal specifications of real-time systems can address these issues.

#### 2 SPECIFICATION AND SPECIFICATION ISSUES

#### 2.1 Introduction

In this chapter, the role of specifications within the software development lifecycle is be shown. Particular emphasis is placed on what specifications are, how they are written and what they are used for. A very important part of this process is the communication of ideas between people.

Correctly specifying the requirements of a software system is a crucial task; mistakes made here affect all subsequent stages of software development [Hughes87, DeMarco78]. Experience has shown that rectifying such errors is both costly and time consuming [DeMarco78]. As a result, many techniques have been developed to aid the specification process: De-Marco methods, CORE, SSADM, for instance [STARTS87]. These, although they are rigorous, lack mathematical formality; thus their correctness cannot be proven. Consequently, there has been a major move to introduce formal methods into the specification process [DEF STAN 00-55]. Formal methods, although they provide many benefits, do not aid communication in many situations. A new technique, animation prototyping, aims to alleviate some of these communications difficulties.

#### 2.2 Specifications in Software Development.

The conventional approach to software development has come under much criticism [Ramamoorthy84, Zave84, Swartout82, Balzer83, McCracken82]. The main objections cited are that its divisions between the different phases of the development are too rigid. It is argued that the development process is one in which the various stages overlap and interact considerably. A very similar argument took place between the advocates of rigid engineering design methodologies and cognitive psychologists. The psychologists argued that real designers do not think in discrete stages [Snodgras88]. Therefore, they argue, design methodologies should support a wider, more flexible approach to the whole design process and the influence of decisions at all stages on the final solution should be recognised.

Balzer [Balzer83] and others recognise that in software engineering too the specification of a system is inevitably intertwined with the nature of the final implementation. Furthermore, the assumption that the specification can be fixed at an early stage in the development process is a too idealistic

[Brookes87]. The developers' perception of the customers' requirements always change. This is inevitable as the developers start with only a limited appreciation of the customers' domain. Despite this criticism, specifications are part of all software development approaches [STARTS]. In order to consider the role of specifications, three main questions need to be answered. These questions are:

- (a) What are specifications used for?

- (b) Where do they come from?

- (c) How are they written?

The profound effects of bad specifications on software quality cannot be ignored and consequently this is a specification-centered view of software development. As has already been stated the flow of information between groups involved in these processes is very important [Potts88].

"(T)his brings us to the most important requirement of all: we need methods, not data flow diagrams or formal systems but real methods, methods that assist in the elicitation of expert domain knowledge and consolidation of knowledge from different sources, methods that bristle with heuristics to check the consistency, quality and appropriateness of the specification, methods that define the viewpoints from which one can inspect the specification, methods which produce specifications that can be used by clients, lawyers, requirements analysts, project managers, quality assurance auditors, hardware interface engineers, and software developers. These people are people. With so many of them involved it is time software engineers started paying more serious attention to the human factors of specification methods."

Consequently in considering the process of specification the following points are highlighted:-

- \* Who is involved in the process?

- \* What information do they need?

- \* Who has this information?

- \* To who else is the information useful?

- \* How can the information be exchanged between parties?

- \* How can parties check each others view of the information?

- \* How can the information gathered best be passed on to subsequent stages of development?

#### 2.2.1 The use of specifications.

The end users of the software specification are the software designers. Their job is to decide in detail how the software will accomplish its task. They need a clear statements about function, performance, interfaces and constraints. The specification is an expression of these goals. The overall aim of this process is to form first an architectural design and then a detailed design of the system.

The software designers are usually not the same designers as those who wrote the software specification. Consequently, as with the SOR document, the clarity and accessibility of the information in the specification document is crucial to the success of the design and subsequent phases. This requirement of specifications is emphasised when considering ways to improve the specification process.

Architectural design takes the functional and non-functional requirements and forms a structure of clearly defined software components. Each components performs a specific task which relates to the identified requirements. This is not a trivial task because of the large amount of information to be organised. In order to help them in this task there are a number of different development tools and methods. The STARTS Guide [STARTS87] contains a comprehensive review of many such software development tools.

Detailed design adds detail to the structure and components in the architectural design. This activity leads into the coding and testing of an implementation. It should also be noted that the specification will be needed by those testing the software. Their job is to ensure that the software meets all its requirements of function, performance, interfaces and its constraints. In safety-critical software, traceability between the requirements and the deliverable software is a very important. So clear, easily-accessible specifications are essential in the development of such systems.

#### 2.2.2 The origin of specifications.

As with any engineering discipline the successful development of a software system depends on a clear understanding of the role of that system. This implies that designers must begin a project with a thorough analysis of the problem and a sound strategy for development of solutions to that problem [Prager87]. In industrial and, more specifically, military software development great emphasis is placed upon long and wordy statements of the problem. For real-time embedded systems, software specifications are generated during the overall system design phase. These specifications are defined in a Statement of Requirements (SOR) document, this being produced by the systems designers. In industrial and defence applications, systems designers are usually engineers, with backgrounds in fields such as mechanical, avionic, chemical and civil engineering. Software engineers are rarely employed in this role. This is one source of problems when subsequently writing specification. SOR documents are the starting point for software specification. It is essential, therefore, to know what sort of information do they contain.

According to the STARTS guide, the four main software requirements covered by SOR documents are:-

- \* Function what is the software supposed to do.

- \* Performance how well it should perform these tasks.

- \* Interfaces how it fits in with its environment. Interfaces can be further categorised as:-

Physical: how people interact with the software.

how the software interacts with external devices.

Software: how it interacts with other software, e.g. operating systems and databases.

\* Constraints - what may and may not be done.

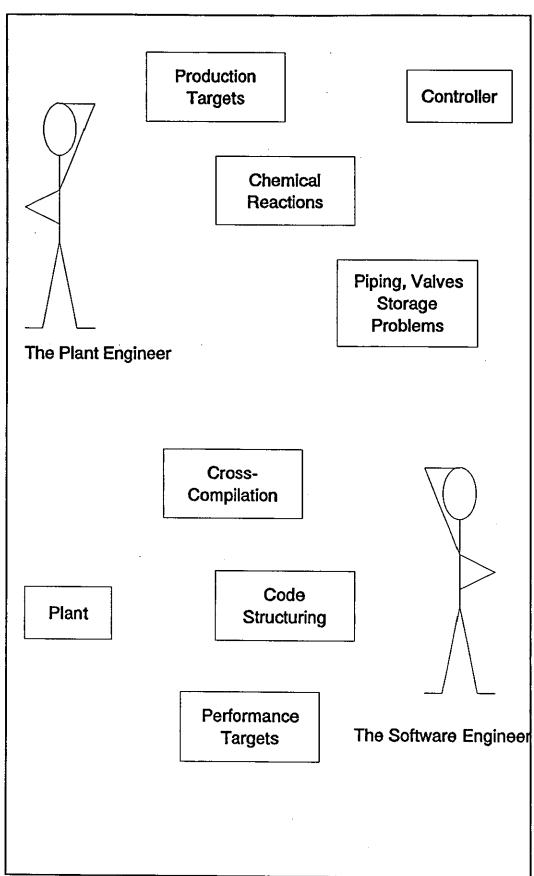

This information, and particularly the constraints, derive from design decisions taken even this very early stage of the development process. Real-time embedded systems are, by their very nature, only small parts of much larger systems. Consequently the overlap between specification - stating WHAT is to be done - and design - deciding HOW it is to be done - is very marked [Swartout82]. Figure 3 shows two contrasting views of a real-time system. It is apparent from this that many design constraints will have been placed on the software during the specification and design of the whole system. So the requirements for a real-time system derive from design decisions made to meet much higher level specifications. Consider the following example:-

Managers at a large chemical manufacturing company perceive an increase in the markets demand for a new organic chemical. Their requirement for profitable production of this chemical is translated into the specification - build a production plant to produce X tonnes per year of chemical Y at price £Z per tonne. Using this specification, chemists, chemical engineers and plant engineers decide on what method of production to employ. Their requirement for physical devices to implement this process becomes a number of new specifications such as - a storage vessel to hold W tonnes of a chemical, piping to withstand V KPa, heaters to produce U watts, a temperature controller, a valve sequencer and a pressure controller. Some of these specify the physical plant while other devices seem to have functions which may require microprocessor control. One such device, a temperature controller, is to be implemented using a microprocessor. Finally a specification for real-time software is generated.

This example serves to illustrate the very close link between real-time software and the larger system of which it is part. The specification for real-time software is the result of a number of higher-level design decisions. These decisions are taken by people who are not necessarily software engineers. The software to be developed must meet the requirements of these people and thus software engineers

Figure 3 Two Views of a Real-Time System.

must be able to communicate their thoughts effectively to non-software engineers.

So in summary, before a specification is written, the system designers:-

- \* Analyze the problem thoroughly from their own point of view;

- \* Form a strategy for developing a system to solve that problem;

- \* Write a statement of requirements document stating the problem and the required form of solution.

This statement of requirements document is used by the software designers as the basis for their software specification.

#### 2.2.3 The writing of specifications.

There is a great deal of information passed from system designers and engineers to software designers in the SOR document. Software specification is the process by which software designers assimilate and organize this information for use by software engineers. There are a number of problems which make this a difficult task.

The first hurdle is the use of specialist terminology. Systems engineers have a good understanding of the system domain: function, structure and behaviour. SOR documents are written from their point of view, that is, the external environment of the software. Normally they are expressed using the technical language and terms of the application environment. The software designer, by contrast, is unlikely to have such detailed knowledge. Thus he is faced with the problem of interpreting the requirements of the specification; then translating these into a form which can be used during the software design phase. This task can be difficult enough when the requirements documents are clear, precise and correct. Unfortunately, as they are frequently ambivalent, ambiguous, incomplete, and sometimes in error [Meyer85], it may be an extremely onerous task. This is the second hurdle in the development of good quality specifications.

Technical language is not the only problem with SOR documents. A clear understanding of the requirements is obstructed by the text of the SOR being:-

- (a) Ambivalent. The SOR is written so that it can mean one thing or another or possibly both.

- (b) Ambiguous. The SOR fails to make its point clearly enough for the reader to understand.

- (c) Incomplete. A vital, or useful, piece of information has been omitted.

- (d) Inconsistent. The SOR includes contradictory information.

- (e) Complex. The SOR contains all necessary information, but in such a way as to make comprehension difficult.

- (f) Wrong. The SOR contains information that is not true. Such errors derive from many different sources.

Such problems can only be resolved satisfactorily by consultation with the system designers. This is also not a trivial exercise. Discussions between the system designers and software designers can also highlight further problems with the SOR and its interpretation:-

- (h) What the SOR describes is not always what was intended by the system designers or is actually needed by the user.

- (i) The software designers have incorrectly interpreted what the SOR says.

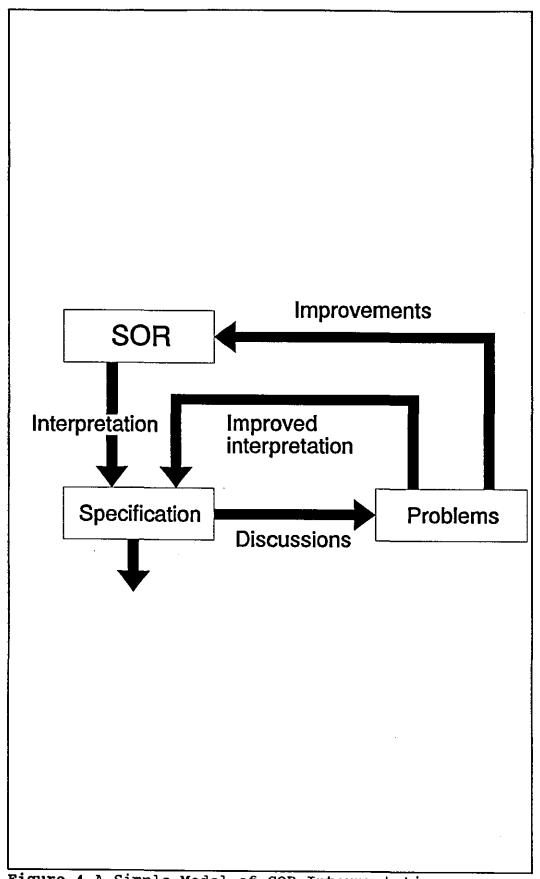

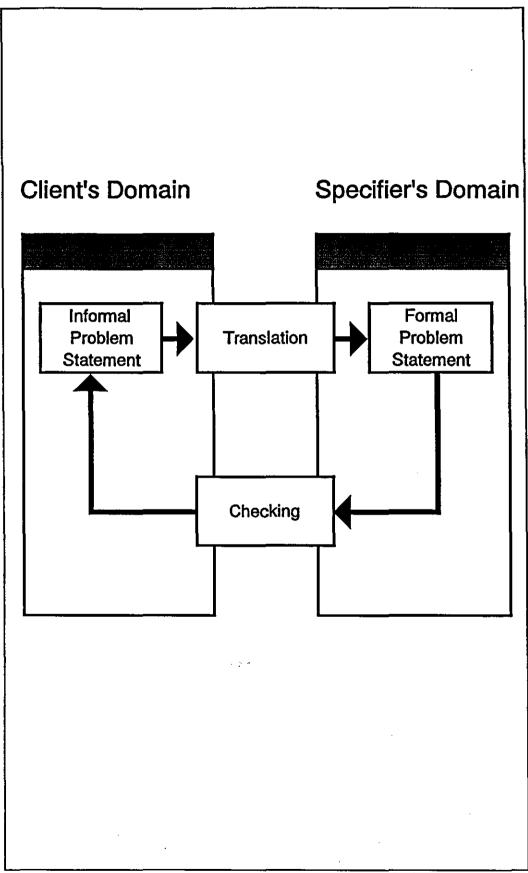

From this it can be seen that developing a good quality specification is a highly interactive process. Figure 4 shows a simple model of the interpretation of the SOR to build a specification. This illustrates the importance of discussions between the parties. Through these discussions and the increased understanding that develops, both the specification and the SOR are improved.

#### 2.3 Ways to Improve the Specification Process.

The central theme of the specification process is the communication of ideas and information between different groups of people involved in the software development process. Specifications are essentially a bridge between the systems designers requirements and the software designers efforts to build software to meet them. Any improvements to this process must thus aim to smooth the passage from SOR to specification and thence to software design and testing.

The transition from SOR to specification is a highly iterative process. Improvements to this transition process include:-

- (a) Careful writing of SOR documents.

- (b) Using good structure so that requirements are easily accessible to both systems designers and software specifiers.

- (c) Explanation or avoidance of highly specialised technical language.

- (d) Review of specifications with respect to the SOR. The software specifiers need to express their understanding of the requirements clearly to the system designers.

Figure 4 A Simple Model of SOR Interpretation.

Producing specifications which can analysed systematically is another way to aid the specification process [Ramamoorthy84]. When the specification is being produced the specifiers need to answer certain questions. They also need to convince the system designers that such questions have been answered. Some of the questions which might be posed by the specifiers are listed below.

What does the specification say?

Is it consistent within itself?

Is it consistent with the specifiers' view of the system?

Is it consistent with the system designers' view of the system?

Is it complete within itself?

Does it contain all the information needed?

Is it correct within itself?

Is it syntactically correct?

Is it semantically correct?

Is it feasible?

Is it correct?

Does it describe the system as the specifiers understand it?

Does it describe the system as the system designers understand it?

Will the specified system perform the desired tasks?

Will the specified system meet safety requirements?

These are important points for the specifier, but the management of this process is equally important.

Any approach to specification ideally should support:-

- (a) The coordination of teamworking;

- (b) The documentation of benchmarks for acceptable functionality and performance;

- (c) The ability to express design decisions;

These points aid the writing of a specification which accurately expresses the system designers requirements. However, the software designer as end users of the specification need considering. In order to aid the production of software in line with the requirements, a specification must state the requirements:

- (a) Unambiguously. All requirements must be carefully written so as to avoid different interpretations.

- (b) Completely. All significant information must be provided. Terms must be clearly defined.

- (c) Verifiably. Where possible measurable quantities or properties required should be provided.

- (d) Consistently. Statements about requirements must not conflict.

- (e) Traceably. The origins of each requirement should be clear.

To overcome some of these problems, and to improve software quality and productivity, the use of mathematically based specification languages, or formal methods, has been proposed [Gibbons87, Cohen82]. A second technique, software prototyping, has been proposed in order to address the problems of communication and requirements analysis [Budde84]. The next two sections give a brief introduction to these techniques and suggest how the two can be combined.

#### 2.4 The Role of Formal Methods in Specification.

Formal methods are based on mathematical formal systems. They use a mathematically based formal notation and reasoning system to describe and analyze the structure, function and behaviour of software systems. Carefully applied to the development of software, they form the basis for a rigorous engineering approach [ALVEY84].

The role of formal notations in software engineering varies considerably. Some methods are intended to cover a large portion of the software life cycle. VDM [Jones90], for instance, embraces the cycle from specification through to coding. Others, such as FOREST [Goldsack88], address themselves only to the problem of stating system specifications. Here the concern is mainly with the specification aspects of formal methods.

There are a number of claimed benefits for the use of formal specification techniques [Hall90]. First, they introduce precision, rigour and clarity of thought into the process. As a result, the specification document is likely to be correct, consistent and complete. Second, the document itself can be used as a firm basis for interaction between the software designers and the system specifiers. Third, this approach also raises the visibility of the project as documentation is produced from the beginning of work.

The application of this approach raises questions as to who should produce the formal specifications. Few systems designers have knowledge or experience of discrete mathematics and formal reasoning, the basis of formal specification techniques. Consequently, it becomes necessary to employ specialists to convert the informally expressed requirements of the system designers into formal software specifications. When they complete their work the resulting formal specifications are presented to the system designers for approval and agreement. But the notation used is fully comprehensible only to the experts who produced the formal specifications. The systems designers must decide whether their requirements are being correctly specified. This, at the present time, is a major problem for the designers of real-time embedded systems.

A final - crucial - point concerns the use of formal methods for proving the correctness of specifications. Proponents of this approach stress the confidence obtained by using mathematical techniques in place of conventional procedures. But rarely are the complexities of proof discharges highlighted. To illustrate this point, Appendix D contains the discharge of the implementability proof for the very simple logic function specified there. Its intricacy raises a serious question. How confident can we be in our ability to detect errors in such mathematical workings?

The need to make formal specifications comprehensible to non-specialists is great. The recognition that system designers need to assess the accuracy of formal specifications is the main motivation behind the approach to specification called animation prototyping.

#### 2.5 The Role of Animation Prototyping in Specification.

The approach used in this project is called animation prototyping. The essential objective of animation prototyping is to illustrate the key properties of specifications to non-computer specialists by using computer-animated pictures [Cooling89]. It provides a demonstration of executable specifications ('animates the specification') in terms of the SYSTEM domain. Animation prototyping may be used to express both the SOR objectives and those of the formal specification document. In this way the system and software designers are more easily able to evaluate the interaction of the software with its environment. This interaction leads to a greater understanding of the system objectives and operation; in turn this should result in software which more accurately meets the needs of the client.

Commercial software projects place severe restrictions on development time and cost. For animation prototyping to be acceptable in this sort of environment, it must fulfil three main objectives:-

(a) Model production must be done quickly - typically no more than a few weeks.

- (b) Clients should need only a minimal knowledge of technical jargon to understand the model behaviour.

- (c) Both client and developer must be able to interact with the model and thus increase their mutual understanding of the problem.

In the commercial development of software, hand-built prototypes are prohibitively expensive. It is therefore necessary to consider what techniques and tools can be used to help in the model building. On this basis, the approach suggested here is to use an executable program, derived automatically from the formal specification, to animate pictures on the computer screen. In this way, animation prototyping aims to help in the discussion and understanding of the problem and the ideas expressed in the formal specification. Animation prototyping and other forms of software prototyping are discussed in more detail in chapter 3.

#### 3 PROTOTYPING AND ANIMATION OF SPECIFICATIONS

### 3.1 Software Prototyping.

## 3.1.1 Prototypes in engineering.

Looking at other engineering disciplines can give an interesting perspective on what prototyping means. In the aerospace industry, full scale working prototypes of aircraft are commonplace. Every year automobile industrial shows are filled with the latest prototype designs. Much electronic design these days is accomplished through computer aided design packages. These offer not only tools for laying out designs but also functional simulators. Thus an engineer can see some of the important features of a design before the actual production work commences. It is worth mentioning that these are disciplines where the investment in production equipment is considerable. Thus it is necessary to know (or have a high degree of confidence) that a design works before production commences. However the production costs of software are escalating to levels where such confidence building is becoming essential.

In software engineering the use of prototypes has also been advocated. Software prototypes have been variously described:

"Prototypes present the user with a relatively realistic view of the system as it will appear."

[Mason83]

"A prototype is an executable model or pilot version of the intended system." [Luqi88a]

"A system that can solve parts of a problem and is used to show potential value to management and prospective sponsors." [Jordan89]

These quotes, particularly the last one, could be made by engineers from any field. It can be seen that prototypes have many possible uses:

- (a) To test the feasibility of various different design approaches.

- (b) To test particular technical aspects of a design ( eg Space shuttle Enterprise which has no engines but mimics the glide characteristics of the full working shuttles )

- (c) To attract funding for further development work ( eg Experimental Aircraft Project ).

- (d) To test user or customer reaction to a particular design (eg New car designs).

### 3.1.2 Prototyping and the Software Life Cycle.

Software engineers should adopt prototyping essentially because they suffer from the same problems which other engineers use prototyping to solve. The engineer's job is to efficiently build a system to solve a customer's needs. In real-time embedded systems, the "customers" are the systems designers. It is they who produce the SOR document and it is their requirements which must be satisfied. There are a number of key aspects to this problem:

- (a) Correctly identifying the problem to be solved.

- (b) Generating possible approaches to solving this problem.

- (c) Using professional judgement to select the "best" approach.

- (d) Overseeing and helping with the resolution of detailed technical problems encountered in the realization of a solution using the chosen approach.

- (e) Ensuring the efficient production of a quality product for delivery to the customer.

Effective methods of code design and production enable software engineers to fulfil the last two objectives. Better methods of dealing with the first three issues are now needed.

As discussed in the previous chapter, there have been a number of different proposals as to what should replace the conventional life cycle model. The one on which the work described here is based is software prototyping.

#### 3.1.3 Prototyping and the Specification Problem.

The largest and most important task facing software designers is to establish the customers' requirements for the system. It has been shown by De Marco [DeMarco78] that problems are caused by errors in the writing and interpretation of the statement of requirements document. Furthermore, these errors are very expensive to correct in terms of time and money [DeMarco78]. Brookes [Brookes87] argues that a system cannot be correctly specified without the customer being able to test a working version of the product. Proponents of rapid prototyping support these views and aim to provide a cost effective means of producing a demonstratable version of the design concept [Maude91].

As seen in the previous chapter, specifying a real-time system is made more difficult by

communications difficulties between system designers and software specifiers. The interpretation of the system requirement is requires a great deal of discussion between the people involved. With the differing perspectives involved it is one in which misunderstandings easily occur. There is a need for all parties to be able to explore a commonly agreed definition of the problem. This requires a method of defining the problem which is easily understood by both parties. This is one of the major reasons for adopting the use of animation prototyping.

# 3.1.4 Different Types of Software Prototyping.

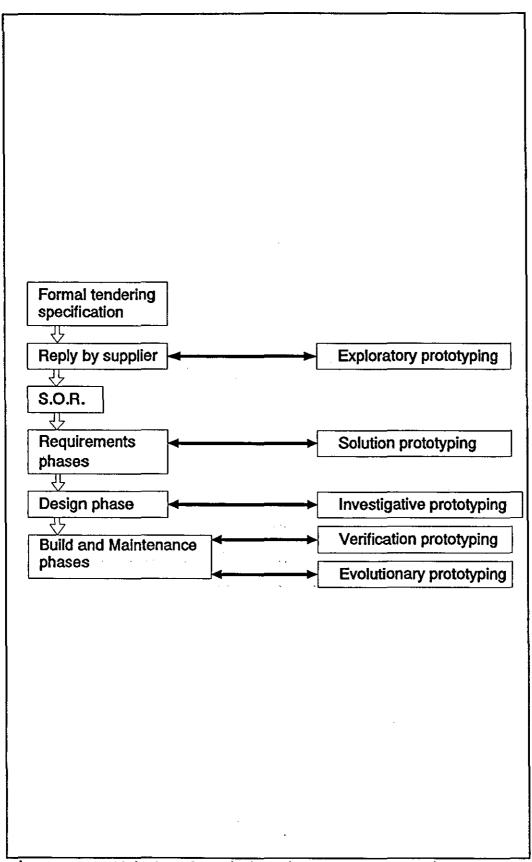

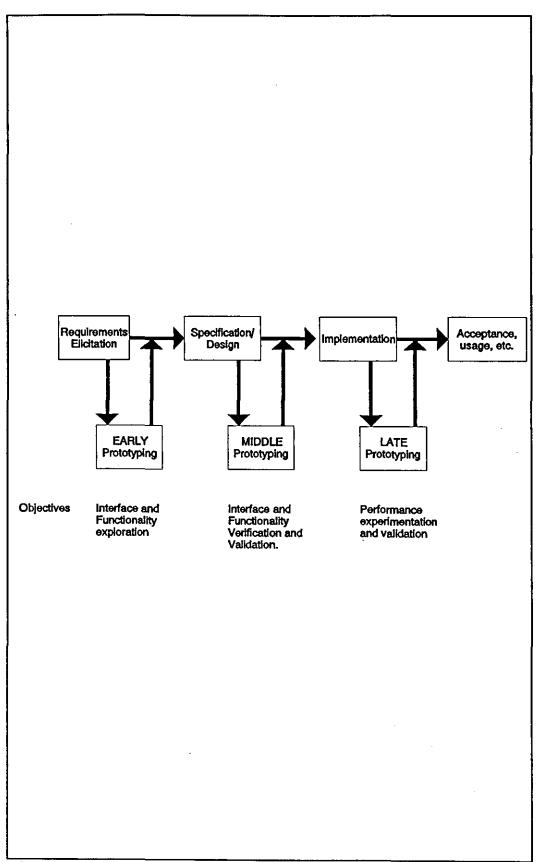

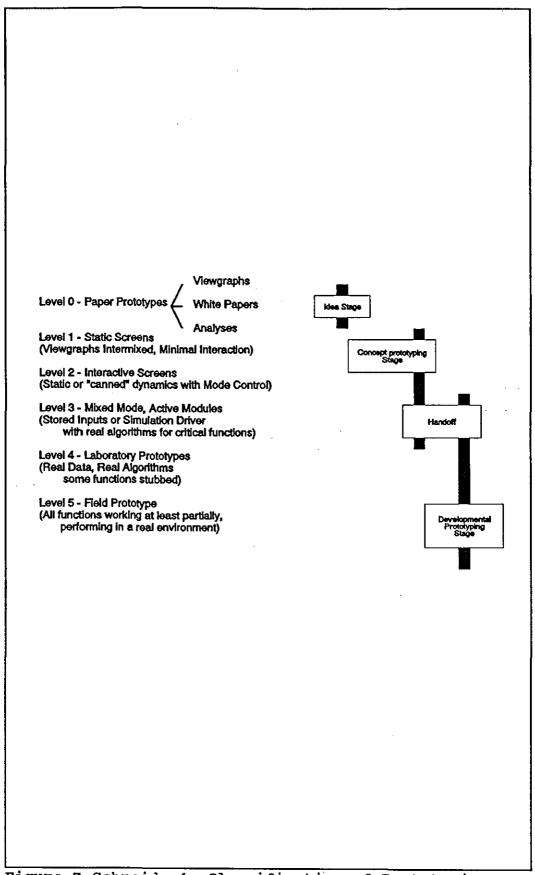

Software prototyping is a relatively new development in software engineering. There are many different types of software prototyping. Various classifications have been proposed for the different types of software prototyping. Watkins [Watkins88] proposes a useful definition as shown in Figure 5. Although it depends a little too much on the reference to a conventional software life cycle model, Ratcliffe's [Ratcliff88] definition places more emphasis on WHEN prototyping occurs than WHAT it is intended to achieve as shown in Figure 6. Schneider [Schneider87] provides a definition based on stages and levels of prototyping. He states the distinction between stages and levels is:

"(T)he stages of prototyping deal with differences in kind, while the levels of prototyping deal with differences in degree."

The relationship between levels and stages of prototyping as envisaged by Schneider are shown in Figure 7.

The common factor in all software prototyping is to allow more customer involvement in software development. This involvement is aimed at producing software which meets the customer's requirements more closely than conventional methods allow. The vehicle for this involvement is usually a demonstration of part of the systems proposed functionality or external appearance. Here the major concern is with using prototyping to extract customer requirements. The techniques of interest is a type of early prototyping called animation prototyping. The work of Budde et al [Budde84] and Tanik and Yeh [Tanik89] gives a broader view of other types of software prototyping.

Figure 5 Watkin's Classification of Prototyping.

Figure 6 Ratcliff's Classification of Prototyping.

Figure 7 Schneider's Classification of Prototyping.

# 3.1.5 Constraints on software prototyping.

Prototyping to explore customer requirements occurs at a very early stage in the design process. Thus any method used should be economical, fast and adaptable, for the following reasons.

- (a) Economical: It is possible that the outcome of requirements analysis may be that the system is not economically viable in its present state. Whether the project is abandoned at this stage or pursued in a modified form, work upto this stage must be scrapped. Therefore it is essential that prototyping should not absorb great amounts of resources.

- (b) Fast: At this stage answer are needed quickly, especially prior to and during the tendering phase of the project.

- (c) Adaptable: As the development of the prototype is an ongoing process, any methodology must provide for easy modification of the model.

If these three goals are not achieved three problems may be encountered:

- (a) Slow response to customer's enquiries. This may undermine confidence in the developers.

- (b) Lack of flexibility. This may lead to a waste of effort in trying to reuse parts of an inadequate model.

- (c) The focussing of excessive efforts on the development of the model. Prototyping should never be seen as a replacement for design techniques; rather it aims to increase the effectiveness of such techniques.

Methods designed to support the quick building and evaluation of prototypes are called rapid prototyping.

### 3.2 Rapid Prototyping.

The concept of rapid prototyping comes from the field of interactive information handling systems. Work here showed that to be effective prototyping must be supported by extensive tool sets [ Musa85, Gomma81, Dearnley83, Alavi84].

If software prototyping is to be widely adopted it must demonstrate clear commercial advantages. Software production is a competitive business. Thus techniques which are expensive in terms of time and money won't be accepted unless it can be demonstrated that the rewards for such investments are commensurately large. Thus there are two main reasons for using "rapid" prototyping.

- (a) Reduction of the time spent building prototypes. This makes rapid prototyping a commercial proposition.

- (b) Improving the ability of the software produced to meet client requirements. This is very important in many real-time applications, particularly safety-critical applications.

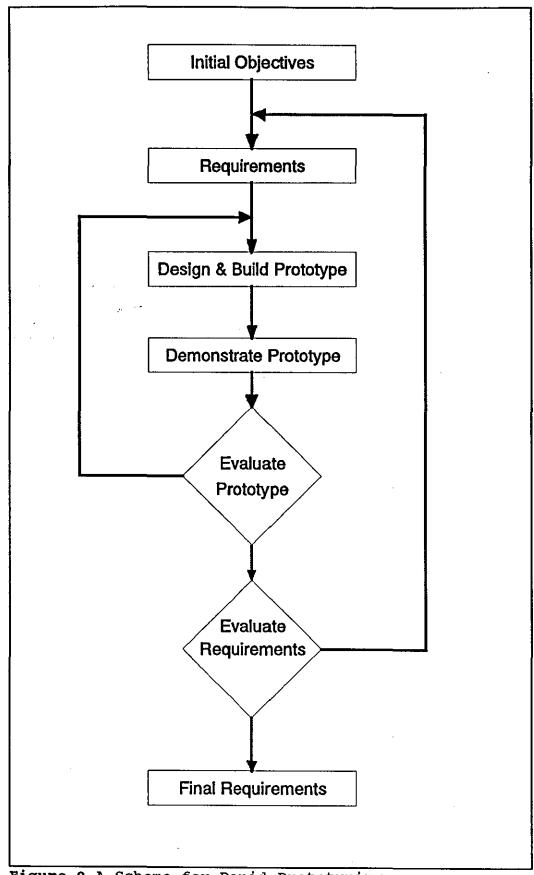

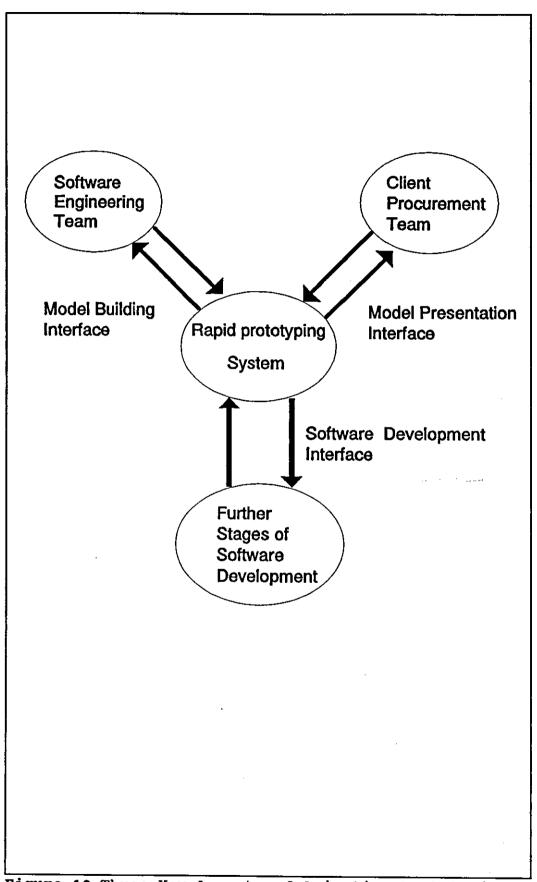

In rapid prototyping models are built quickly then demonstrated to the client for evaluation. The results of this evaluation are then used to modify the model. This process is repeated until the customer is satisfied about the properties demonstrated by the model. A typical scheme for rapid prototyping is given in Figure 8. In rapid prototyping a question which needs careful consideration is how customers are to be involved. In the words of Potts, in an piece of work highly critical of software engineering methods [Potts88].

" It is no use 'executing' a specification only to watch it wobble bewilderingly; the behaviour of the specification must be explained in terms of application-specific constructs with which the client is familiar."

The approach adopted in this research project is to use computer-animated demonstrations of the system's interaction with its external environment. This is called animation prototyping.

# 3.3 Animation Prototyping.

#### 3.3.1 An introduction to animation prototyping.

There are two central themes in animation prototyping. The first is a model which is used to demonstrate important properties of the proposed software. The second is the provision of tools and methodologies to facilitate the quick construction and manipulation of these models. Animation prototyping is aimed at the specification of real-time embedded systems.

Building a model is considered important because:-

Figure 8 A Scheme for Rapid Prototyping.

- (a) It acts as a vehicle for communication between customer and developer. The specification must be assessed to see if it describes the customers' requirements. Real-time systems are used in areas where the customer has very specialised knowledge about his own field but very little knowledge of software engineering. Model building makes the specification comprehensible to non-software specialists.

- (b) It allows both parties to increase their understanding of the problem. In particular, by demonstrating the dynamic properties of the system, key elements can be identified. This is of special importance when dealing with real-time systems where dynamic responses are complex.

- (c) The explicit modelling of the system helps to avoid misunderstandings about the importance of response requirements. In some cases these requirements are fixed by plant or safety considerations and are beyond the control of the software developer. In other cases requirements can be changed to eliminate unnecessary, costly design requirements. Such problems arise when customers do not appreciate the technical difficulty of achieving a response which is not critical to the system's safe functioning.

In data processing applications, where systems are oriented around the user interface, generating feedback from customers about the "feel" of a system is relatively easy. There are certain features which are common to most data processing systems and they have all spawned specialised prototyping tools. Hartson's paper [Hartson91] gives a good "state-of-the-art" report on rapid prototyping in this field. In real-time systems these features are of lesser importance. Of far greater importance is the question of the system's interaction with its external environment.

In order to obtain customer feedback it is necessary to demonstrate the model properties. This must not require customers to have a detailed knowledge of software engineering techniques. When rapid prototyping real-time systems, a mimicking of the system's actions is often the best way to demonstrate to the customer what the proposed software does. However, unlike data processing problems, there are few recurrent themes. Tools for real-time animation prototyping must support the modelling of systems with very diverse behaviour.

## 3.3.2 Uses of animation prototyping.

Animation prototyping is seen mainly as a vehicle for communication between customers and developers. These discussions are aimed at a number of different areas where communication

#### difficulties exist.

- (a) Tendering for contracts. The production of animated prototypes to demonstrate possible solutions to customers has advantages:

- \* Demonstrating understanding of the customer requirements as currently expressed.

- \* Demonstrating in a non-technical manner the results of using different software techniques.

- \* Demonstrating particular products or expertise that the developers possess.

- \* As a side effect, producing a useful introduction to the project for new team members.

- (b) Requirements Analysis. To successfully analyse customer requirements, developers need a means to express their ideas about a system. Animation prototyping can be used to provide animated models of basic concepts.

- (c) Validation of Formal Specifications. As recognised by Potts [Potts88] one of the greatest problems facing users of formal methods is communication with the customer. More importantly large formal specifications are very difficult to interpret by any single person. This problem is especially important in organisations where the people who generate the informal system concepts do not understand formal notations.

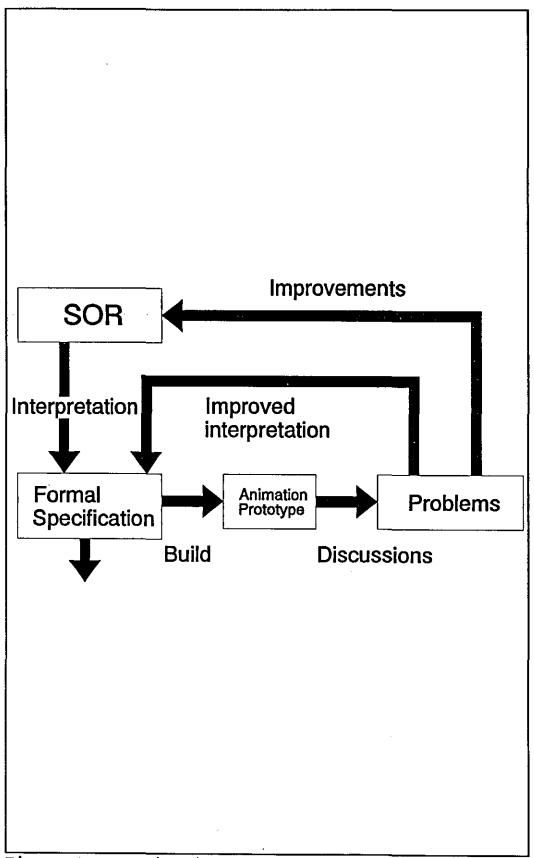

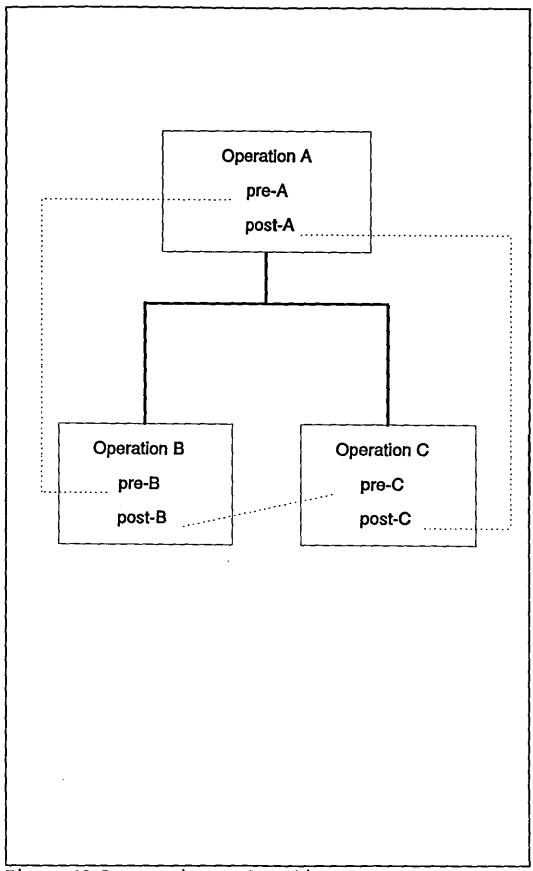

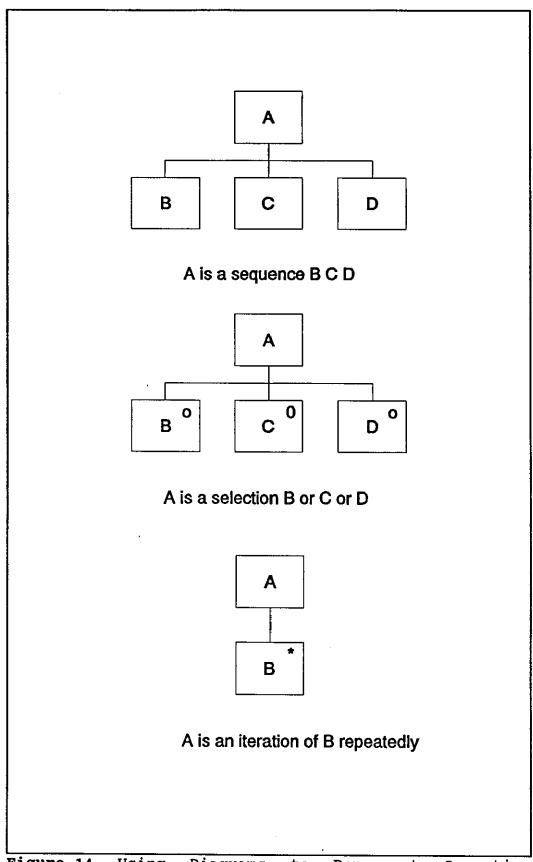

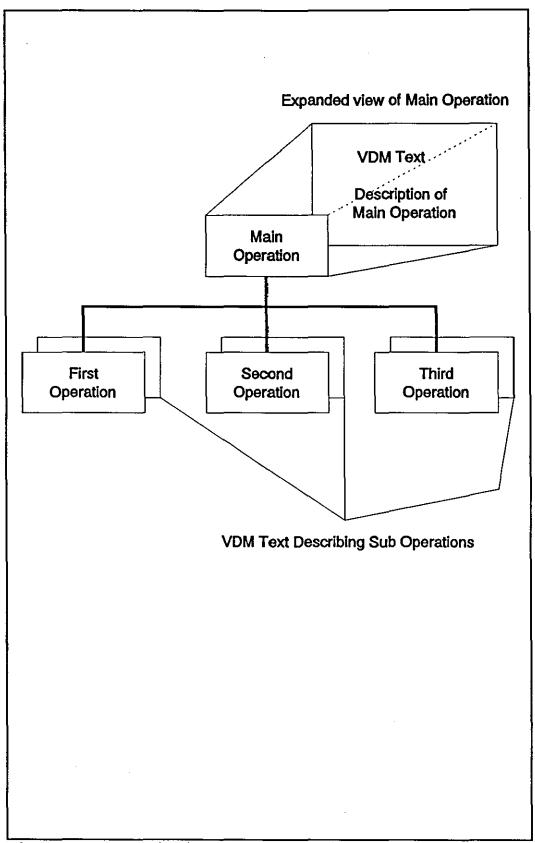

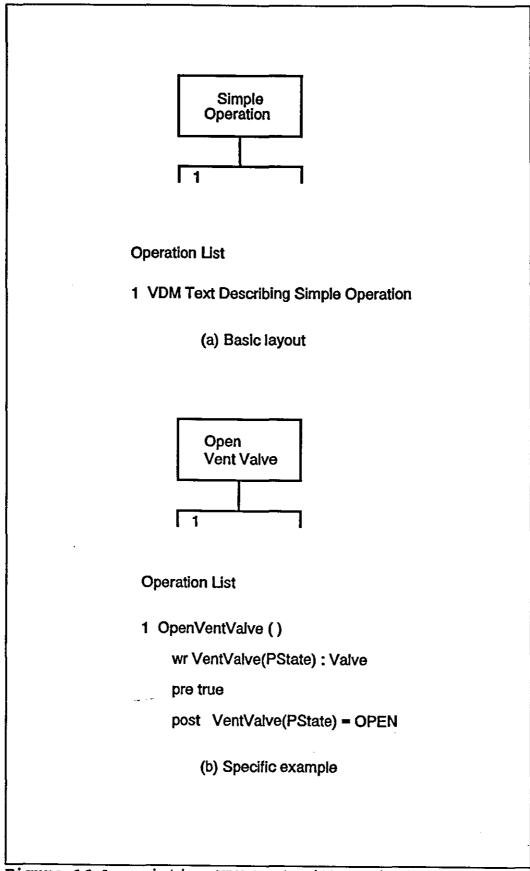

Consider the example in Figure 9. Assessing the formal statement to see if it accurately expresses the original idea is crucial. The use of animated prototypes translated from formal problem statements can overcome this problem. The use of animation prototypes in this role is the main focus of this thesis and is discussed in greater detail later in this chapter.