This item was submitted to Loughborough University as a PhD thesis by the author and is made available in the Institutional Repository (<u>https://dspace.lboro.ac.uk/</u>) under the following Creative Commons Licence conditions.

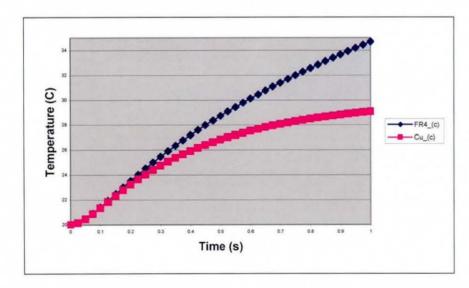

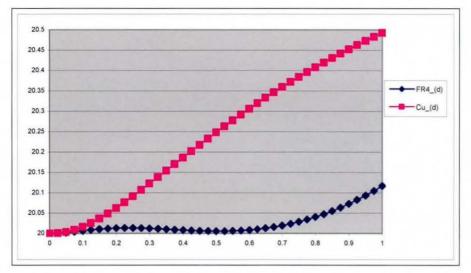

| COMMONS DEED                                                                                                         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Attribution-NonCommercial-NoDerivs 2.5                                                                               |  |  |  |

| You are free:                                                                                                        |  |  |  |

| <ul> <li>to copy, distribute, display, and perform the work</li> </ul>                                               |  |  |  |

| Under the following conditions:                                                                                      |  |  |  |

| <b>BY:</b> Attribution. You must attribute the work in the manner specified by the author or licensor.               |  |  |  |

| Noncommercial. You may not use this work for commercial purposes.                                                    |  |  |  |

| No Derivative Works. You may not alter, transform, or build upon this work.                                          |  |  |  |

| <ul> <li>For any reuse or distribution, you must make clear to others the license terms of<br/>this work.</li> </ul> |  |  |  |

| <ul> <li>Any of these conditions can be waived if you get permission from the copyright<br/>holder.</li> </ul>       |  |  |  |

| Your fair use and other rights are in no way affected by the above.                                                  |  |  |  |

| This is a human-readable summary of the Legal Code (the full license).                                               |  |  |  |

| Disclaimer 🖵                                                                                                         |  |  |  |

|                                                                                                                      |  |  |  |

For the full text of this licence, please go to: <u>http://creativecommons.org/licenses/by-nc-nd/2.5/</u>

| Universit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | University Library |                      |               |                                         | ough  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|---------------|-----------------------------------------|-------|

| Author/Filing Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                      |               |                                         |       |

| Class Mark .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ·····              | T                    | •••••         | ••••••••••••••••••••••••••••••••••••••• | ••••• |

| Please                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | note that f<br>ove | ines are<br>rdue ite | charge<br>ms. | ed on ALL                               |       |

| interne de la composition de |                    |                      |               | · ·                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                      |               |                                         |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                      |               |                                         |       |

| -<br>-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |                      |               |                                         |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                      |               |                                         | •     |

•

|   | 0402941055                          |   |

|---|-------------------------------------|---|

|   |                                     |   |

| I | NINE KINEN I DIENKE DIE BUILT IN NI | : |

.

•

,

•

By Andrew Ochana

## A Doctoral Thesis submitted in partial fulfilment of the requirements for the award of Doctor of Philosophy of Loughborough University

September 2004

### Abstract

This thesis demonstrates the feasibility of power cycling a "Flip Chip" assembly for reliability assessment. The assemblies studied were Si on Si Multi-Chip Modules (MCMs) that were mounted on either an organic FR4 or a metallic (copper) substrate. The aim of the work was to investigate how anisothermal temperature distributions caused by local power inputs could influence the reliability of devices that would not be expected to be effected by thermal cycling. This work was performed using two complementary techniques: physically manufacturing assemblies in order to perform "real" power cycles, and utilising Finite Element Analysis (FEA) to perform "virtual" cycles.

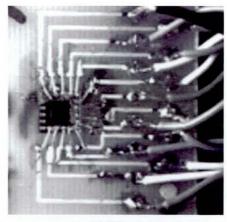

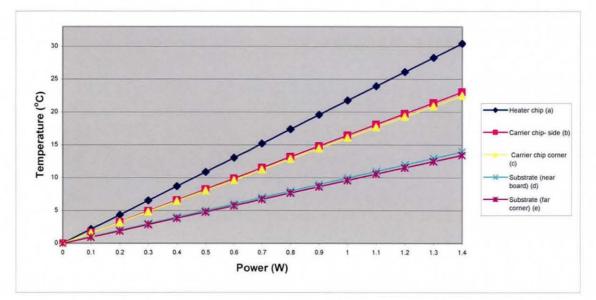

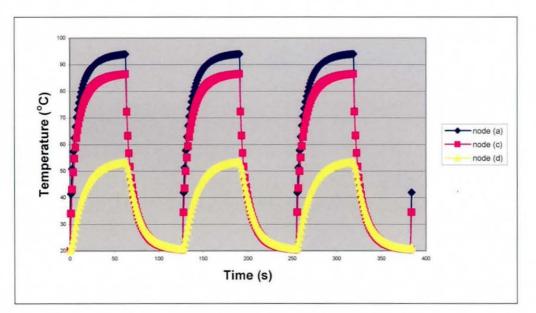

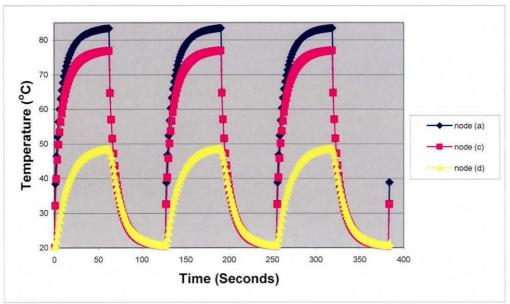

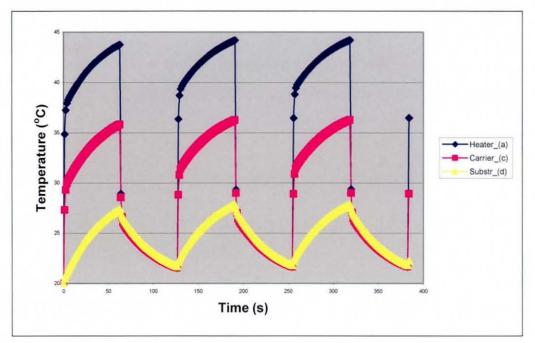

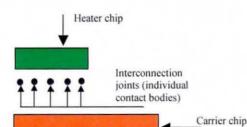

The MCMs consisted of "heater chips" into which electrical power could be dissipated to heat the device locally. These heater chips were flip-chip bonded to Si carrier chips by solder interconnections and the entire assembly was then mounted onto a substrate. The thermal performance of the MCMs as a result of power input was characterised under steady state and cycling conditions using a number of techniques including thermal imaging. In addition, many devices were power cycled to evaluate their reliability.

In addition to the evaluation of real devices, a three dimensional finite element model was developed of the same structures. The model initially provided thermal data that was validated against that obtained from the real devices operating under the same environmental and power input conditions. In addition, it enabled the stress level within the solder joints to be evaluated so that insight to the long-term reliability of the assemblies could be gained.

The results of the experimental and modelling work have shown that the thermal performance and reliability of the devices depend strongly on the substrate onto which the MCMs are bonded. It was found that, using a copper substrate, the temperatures reached within the assemblies were greatly reduced and that the reliability during power cycling was enhanced.

Keywords: Flip Chip, Finite Element Analysis, Power Cycling, Reliability, Multi-Chip Modules, Solder.

i

## Acknowledgements

First of all I would like to thank God for granting the opportunity for me to complete this, without whom this would not be possible.

I would particularly like to give special thanks to my supervisors, Dr David Hutt and Mr David Whalley for their continual guidance and support through my time completing this work. I would also like to express my gratitude to the technical staff, in particular Neville Carpenter and Andy Sandaver who have repeatedly gone beyond the call of duty to help me complete some of the practical work. I would like to thank Dr Amin Al-Habaibeh for the extended loan of some of the specialist thermography equipment, and also Furo Jumbo for offering me a valuable lifeline towards the end of my work.

I would also like to say thank you to the rest of my department, in particular my colleagues within my research group for continual support, the Students Union for keeping me occupied in my time away from my studies. Lastly I would like to thank all my friends and family for their relentless patience and understanding.

If there's anyone I have left out, it was not intentional so thank you

I would like to dedicate this thesis to my parents: - Richard and Mary Ochana, just to say thank you for continually believing in me when it seemed that everyone (including myself) had doubted my potential.

Happy Retirement

| Contents       |                                                                          |            |  |

|----------------|--------------------------------------------------------------------------|------------|--|

| 1              | Introduction                                                             | 1          |  |

| 1              | Trends in the Manufacture of Electronic Products                         | 1          |  |

| I.1            |                                                                          | 1          |  |

| 1.2            | Advantages of Flip Chip Technology                                       | 4          |  |

| 1.3            | Disadvantages of Flip Chip Technology                                    | 6          |  |

| 1.4            | Thesis Aims                                                              | 9          |  |

| 2              | Literature Review                                                        | 11         |  |

| 2.1            | Higher Power Flip Chip Assemblies                                        | 11         |  |

| 2.2            | Thermal Cycling and Associated Phenomena                                 | 14         |  |

| 2.3            | Investigated Phenomena using Thermal Cycling                             | 24         |  |

| 2.4            | Power Cycling                                                            | 34         |  |

| 2.5            | Conclusion                                                               | 39         |  |

| 3              | Manufacture of Si on Si MCM Assemblies                                   | 44         |  |

| 3.1            | Introduction                                                             | 44         |  |

| 3.1.1          | Background                                                               | 44         |  |

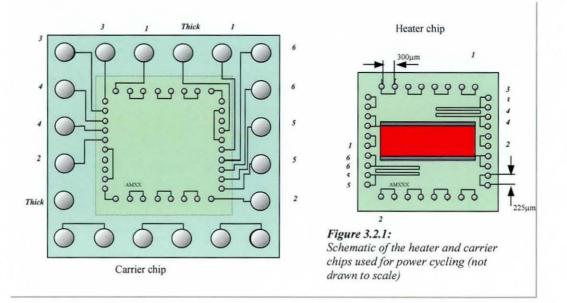

| 3.2            | Component Description                                                    | 45         |  |

| 3.2.1          | Multi-Chip Module (a general overview)                                   | 45         |  |

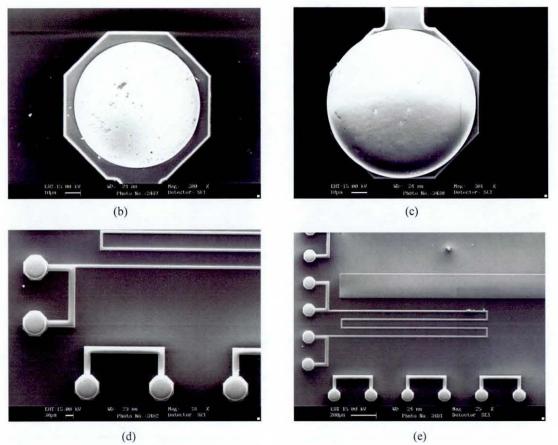

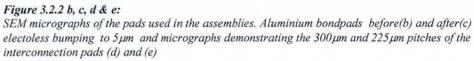

| 3.2.2          | Interconnection Pads                                                     | 46         |  |

| 3.2.3          | Chip and Substrate Descriptions                                          | 48         |  |

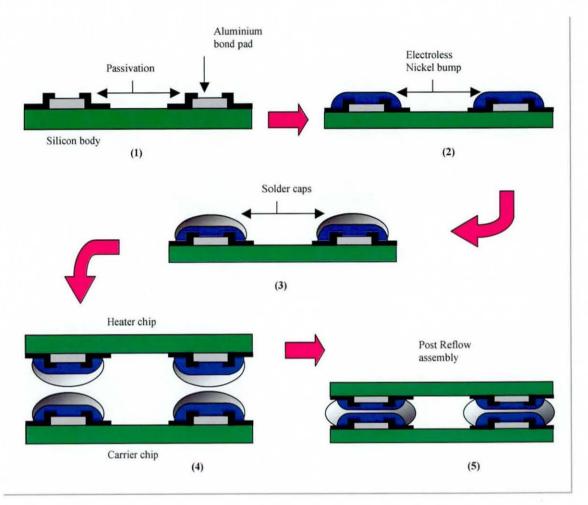

| 3.3            | Chip Preparation                                                         | 51         |  |

| 3.3.1          | Chip Dicing                                                              | 51         |  |

| 3.3.2          | Solder Dipping                                                           | 52<br>54   |  |

| 3.3.3<br>3.4   | Inspection<br>MCM Assembly                                               | 54         |  |

| 3.4<br>3.4.1   | Fluxing                                                                  | 55         |  |

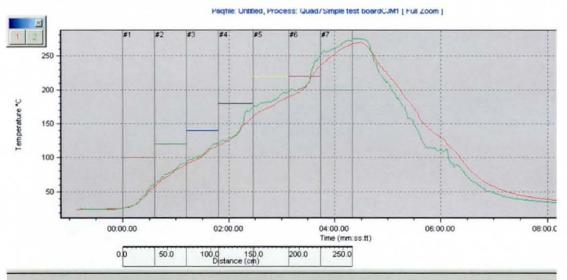

| 3.4.1          | Reflow Profile                                                           | 58         |  |

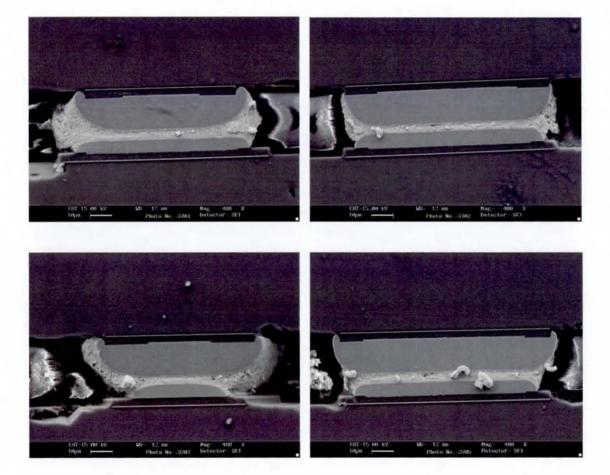

| 3.4.3          | MCM Inspection                                                           | 60         |  |

| 3.5            | MCM to Board Connection                                                  | 61         |  |

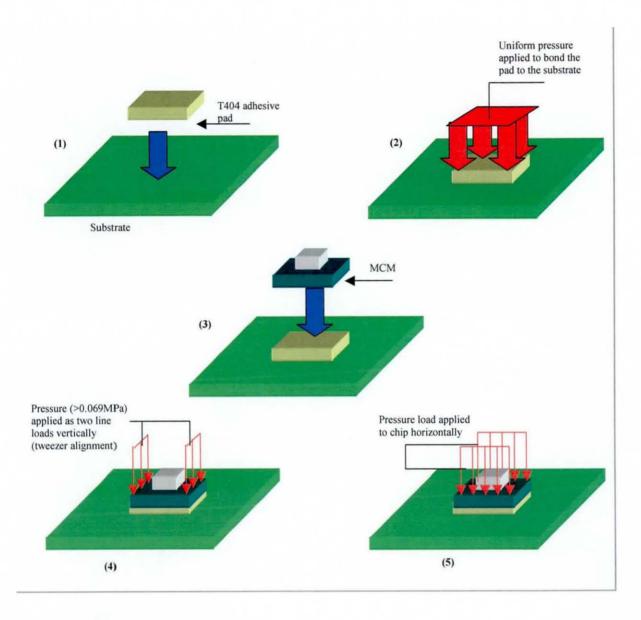

| 3.5.1          | Chip Attachment to Substrate                                             | 61         |  |

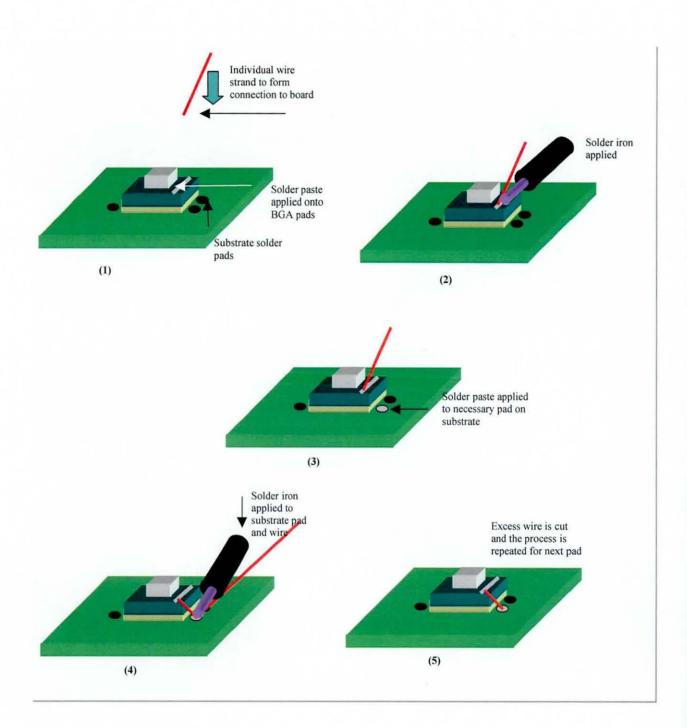

| 3.5.2          | Attaching wires from MCM to board                                        | 64         |  |

| 3.6            | Final Assembly Procedure                                                 | 67         |  |

| 4              | Thermal Data Collection from MCM assemblies                              | 68         |  |

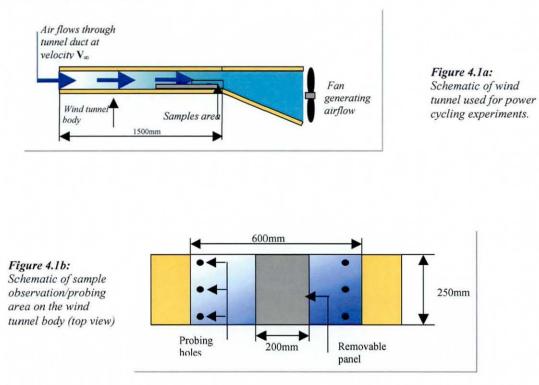

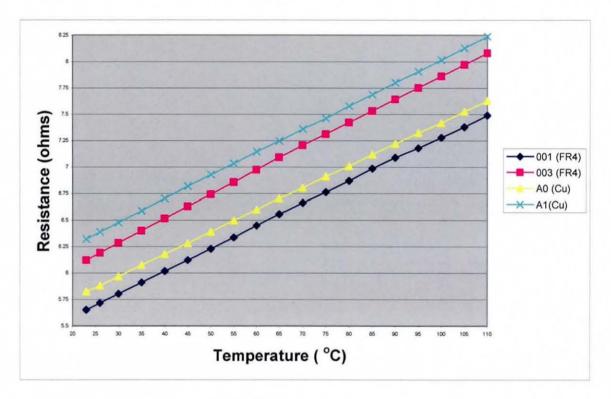

| 4.1            | Power Cycling Chamber                                                    | 68         |  |

| 4.2            | Assembly temperature Measurement                                         | 70         |  |

| 4.2.1          | Thermocouples                                                            | 70         |  |

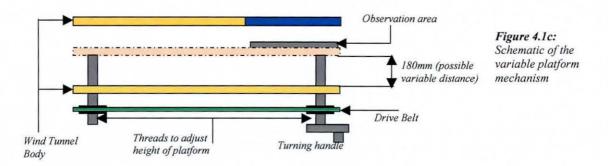

| 4.2.2          | Four Point Resistance Measurements                                       | . 71       |  |

| 4.2.3          | Thermal Imaging Cameras                                                  | 75         |  |

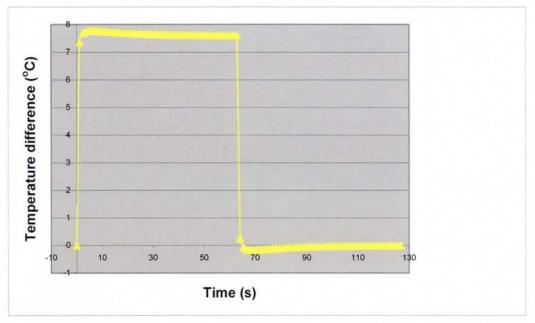

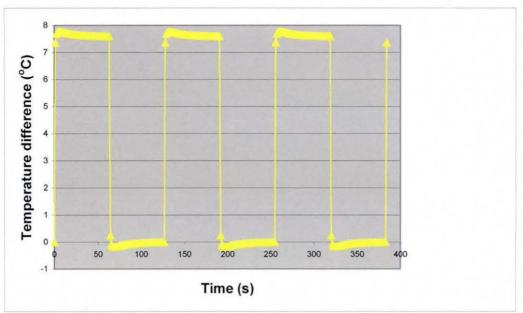

| 4.3            | Thermal Data Capture from the MCMs                                       | 77         |  |

| 4.3.1          | Steady State Procedure                                                   | 78<br>94   |  |

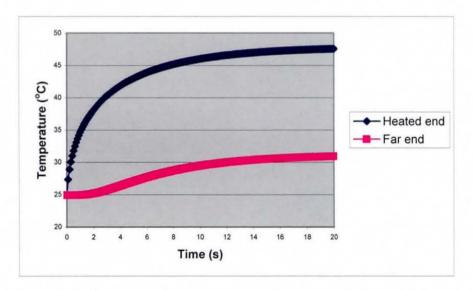

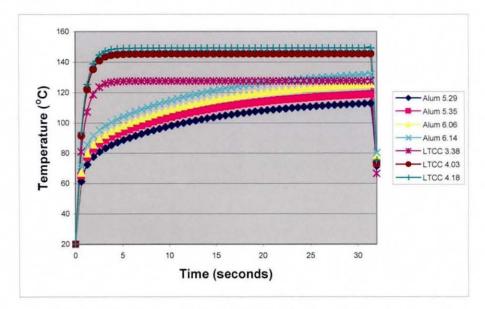

| 4.3.2<br>4.4   | Transient Thermal Data Capture Discussion                                | 94<br>102  |  |

| 4.4.1          | Comparisons of Assemblies on FR4 and Copper                              | 102        |  |

| 4.4.2          | Comparison with Other Studies                                            | 102        |  |

| 4.4.3          | Hardware Merits and Flaws                                                | 106        |  |

| 4.5            | Conclusion                                                               | 107        |  |

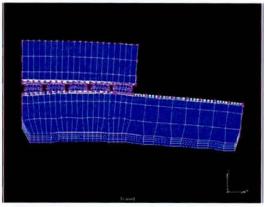

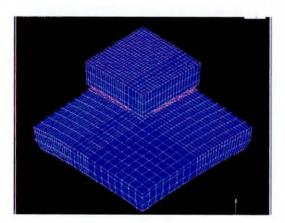

| 5              | Finite Element Model Development                                         | 109        |  |

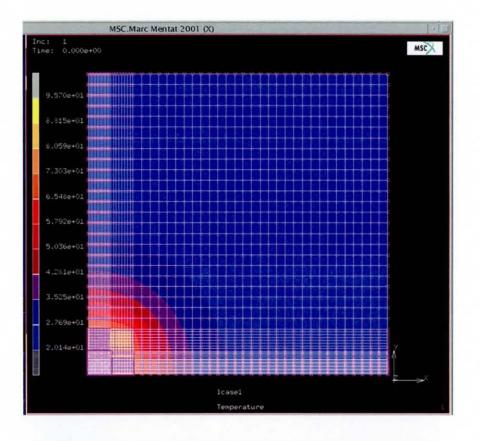

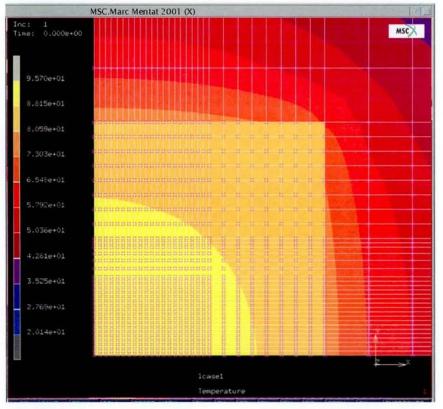

| 5.1            | MARC MENTAT Package Overview                                             | 113        |  |

| 5.2            | Model Construction for Thermal Analysis                                  | 116        |  |

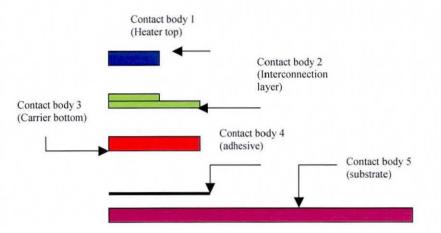

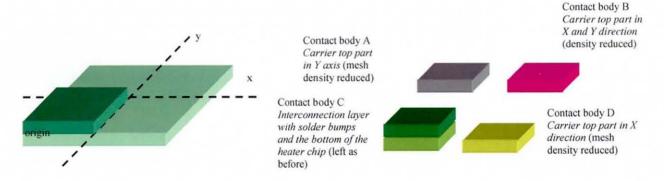

| 5.2.1          | Models Evaluated with respect to Mesh Density                            | 110        |  |

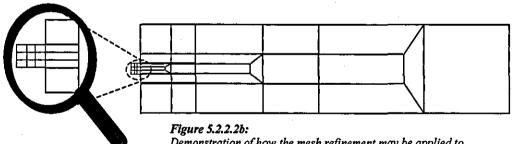

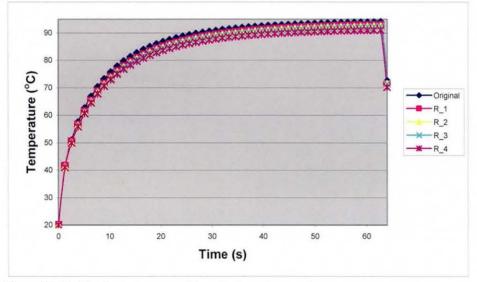

| 5.2.2          | Mesh Refinement Evaluation                                               | 120        |  |

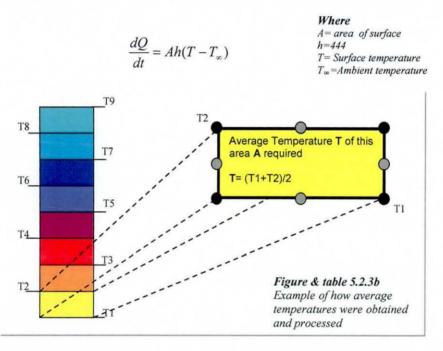

| 5.2.3          | Alternative Solution (Numerical)                                         | 124        |  |

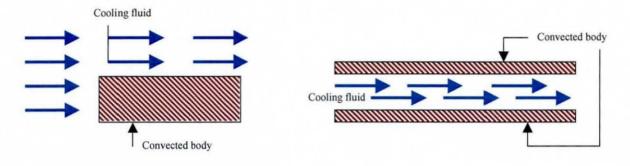

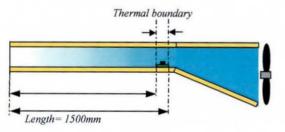

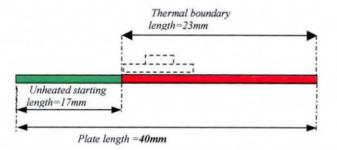

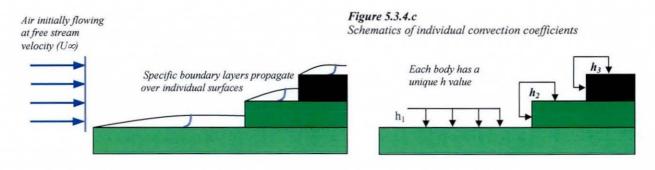

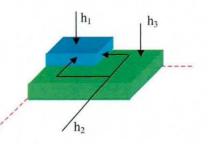

| 5.3            | Heat Transfer by Convection                                              | 126        |  |

| 5.3.1          | Introduction                                                             | 126        |  |

| 5.3.2          | Fundamental Framework for Convection                                     | 129        |  |

| 5.3.3<br>5.3.4 | Dimensionless Parameters<br>Heat Transfer Coefficient for the MCM Models | 132<br>137 |  |

| 5.5.4<br>5.4   | Material Properties                                                      | 137        |  |

| 5.4            |                                                                          | 1.4.4      |  |

iv

| 5.5<br>5.5.1   | Model Generation<br>Mesh Generation Procedure             | 146<br>147 |

|----------------|-----------------------------------------------------------|------------|

| 5.5.2          | Boundary Conditions                                       | 153        |

| 5.6            | Conclusion                                                | 155        |

| 6              | Finite Element Model Results (Thermal)                    | 159        |

| 6.1            | Introduction                                              | 159        |

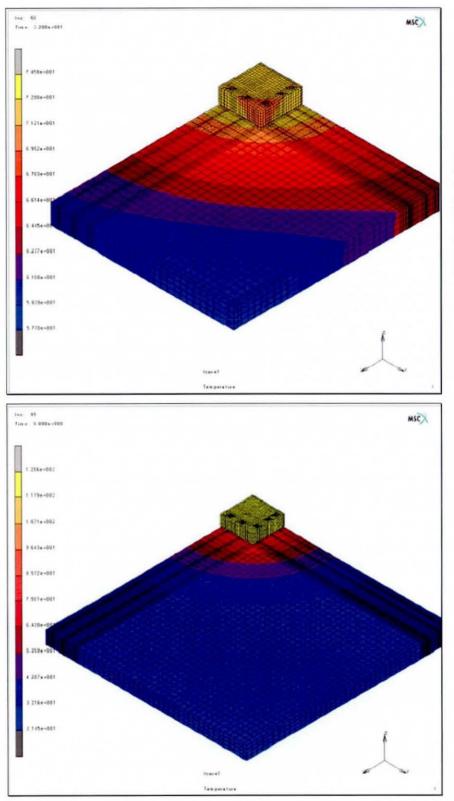

| 6.2            | Steady State Finite Element Results                       | 161        |

| 6.2.1          | FR4 Substrate                                             | 161        |

| 6.2.2          | Copper Substrate                                          | 167        |

| 6.3            | Transient Finite Element Results                          | 172        |

| 6.3.1          | FR4 Substrate                                             | 173        |

| 6.3.2          | Copper Substrate                                          | 167        |

| 6.4            | Discussion                                                | 183        |

| 6.4.1          | Effects of Copper Substrate Compared with FR4             | 183        |

| 6.4.2          | Comparison of FE Models with "Real" Thermal Profiling     | 189<br>196 |

| 6.4.3<br>6.4.4 | Comparison with Other Studies<br>Direct Chip Attach       | 196        |

| 6.5            | Conclusion                                                | 202        |

| 0.5            | Conclusion                                                | 202        |

| 7              | Finite Elemnt Stress Simulation                           | 204        |

| 7.1            | Introduction                                              | 204        |

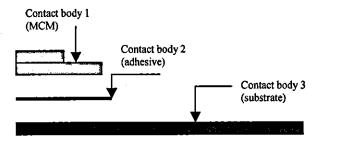

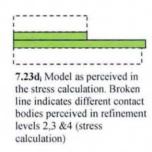

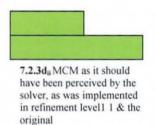

| 7.2            | FE Refinement for Stress Analysis                         | 204        |

| 7.2.1          | Refinement Description                                    | 204        |

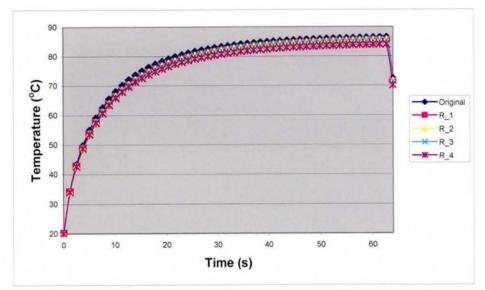

| 7.2.2          | Model Refinement Thermal Validation                       | 208        |

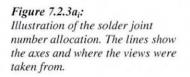

| 7.2.3          | Model Refinement for Stress Assessment                    | 211        |

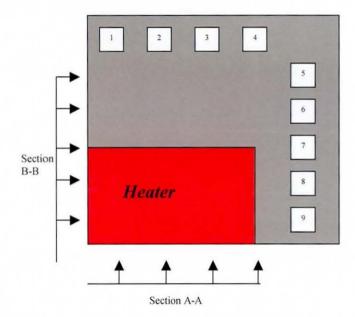

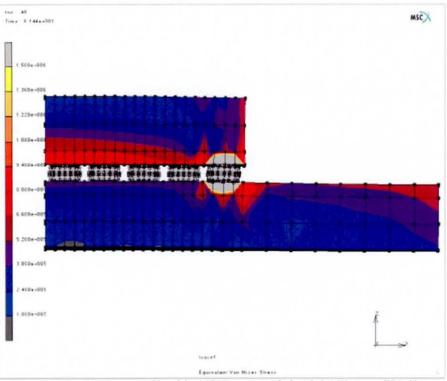

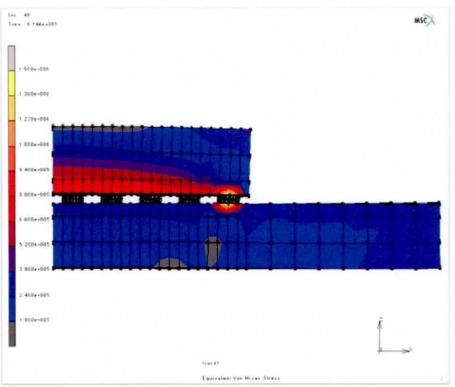

| 7.3            | Stress Modelling of MCM Assemblies                        | 224        |

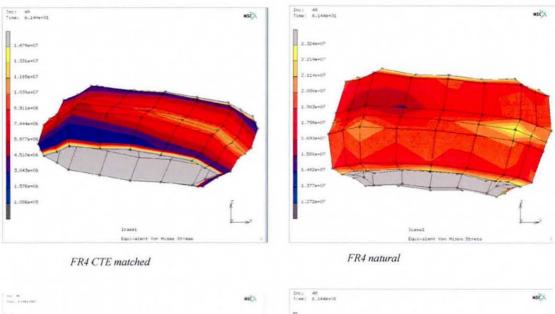

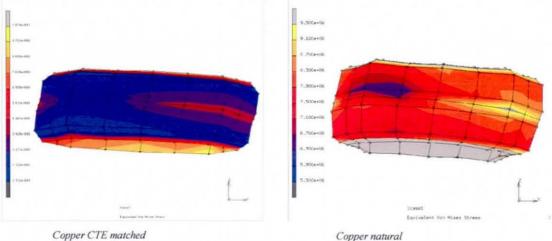

| 7.3.1          | Simulation Results for MCM Assemblies with FR4 Substrates | 226        |

| 7.3.2          | Assemblies on Copper Substrates                           | 239<br>242 |

| 7.3.3<br>7.4   | Influence of Mesh Density<br>Discussion                   | 242        |

| 7.4            | FR4 Vs Copper                                             | 245        |

| 7.4.2          | Generic Stress Characteristics at the Joints              | 246        |

| 7.4.3          | Influence of Local CTE Mismatch                           | 247        |

| 7.4.4          | Plastic Strain Profiles                                   | 248        |

| 7.4.5          | Creep Strains                                             | 250        |

| 7.4.6          | Lifetime Predictions                                      | 251        |

| 7.4.7          | Die Stresses                                              | 252        |

| 7.4.8          | Comparison with Other Studies                             | 254        |

| 7.5            | Conclusions                                               | 256        |

| 8              | Power Cycling of the MCM Assemblies                       | 259        |

| 8.1            | Background and MCM Manufacture                            | 259        |

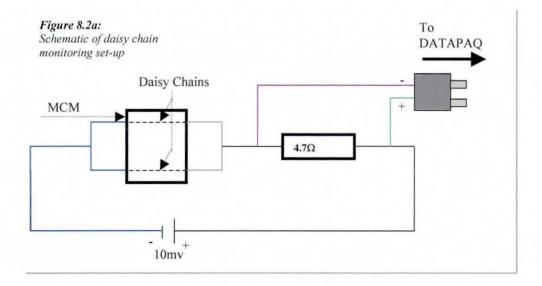

| 8.2            | Power Cycling Apparatus and Procedure                     | 260        |

| 8.3            | Specimen Preparation                                      | 263        |

| 8.3.1          | Mounting and Potting Procedures                           | 263        |

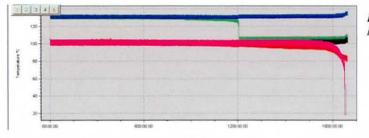

| 8.4            | Results                                                   | 267        |

| 8.4.1          | FR4 Substrate Results                                     | 267        |

| 8.4.2          | Copper Substrate Results                                  | 275        |

| 8.5            | Discussion                                                | 285        |

| 8.5.1          | Comparison of MCMs on FR4 and Copper Substrates           | 285        |

| 8.5.2          | Comparison of FE models and the Power Cycling Results     | 288        |

| 8.5.3          | Comparison with Other Studies                             | 290        |

| 8.6            | Conclusion                                                | 291        |

|                |                                                           |            |

9 Conclusion

293

## Glossary

## Abreviations

- **BGA** <u>Ball Grid Array:</u> A packaging method where the intermediate body has external connections made by attaching solder balls to large diameter pads, and the final connection is made typically by reflowing the component.

- **CTE** <u>Coefficient of Thermal Expansion</u>: The rate at which a material expands when it is heated up.

- DCA <u>Direct Chip Attach</u>: (also known as flip chip on board (FCOB)) A flip chip packaging technology where the chip is placed directly on the circuit board. This method has the benefit of offering the lowest packaging profile.

- **DNP** <u>Distance from Neutral Point</u>: Commonly used when describing the location of a feature on a die (such as a connection joint) with respect to some location (normally central point).

- **FE** <u>*Finite Elements:*</u> Generic name for the science that incorporates FEM and FEA; this involves providing an numerical approximate solution to a problem that may otherwise be unsolvable. This method is applicable to a wide range of physical and engineering problems.

- **FEA** *Finite Element Analysis:* Practical implementation for the FEM. This may be divided in to the pre-processing, analysis and post-processing stages. Pre-processing involves first discretising a given domain (geometry) into smaller sub regions (elements), applying the conditions (boundary conditions, material properties), the analysis involves submitting the job to be solved and the post processing is extrapolating the useful information from it.

- **FEM** <u>*Finite Element Method:*</u> A method of solving partial differential equations, where the equations may involve a function u(x) for all x values defined in the domain with respect to a given boundary condition. The purpose of the method is to determine an approximation for the function u(x)

- **FR4** (FR = Flame Retardant) Typical material used as an insulating base for circuit boards. It is manufactured from woven glass fibres that are bonded together with an epoxy resin. Subsequently the board is cured using temperature and pressure causing the resin to melt and bond such that the board is rigid.

- IC <u>Integrated Circuit</u>: A device on which a number of components, typically transistors are formed on the surface on a single piece of semiconductor

- IPA <u>Isopropyl alcohol</u>: (alternative name 2-propanol) an alcohol commonly used for cleaning applications

- MCM <u>Multi-Chip Module:</u> A packaging technology where one or more die is mounted on to an intermediate body, which is then mounted on to a parent substrate.

- PCB <u>Printed Circuit Board</u> (also known as a Printed Wiring Board in the US): A type of circuit board that has artwork superimposed or "printed" on one or both sides; it may also contain internal signal layers as well as power and ground planes.

- SEM <u>Scanning Electron Microscope</u>: A powerful microscope where images are created using electrons as opposed to light waves.

SMT <u>Surface Mount Technology:</u> A technique for populating hybrids, multi-chip modules and circuit boards where packaged components are mounted directly on to the surface of the substrate. A layer of solder paste is stencil printed onto the pads and the components are attached by placing them on the paste (the viscosity of the past is normally sufficient to temporarily hold the components. They are then soldered using a either a vapour phase or reflow soldering method.

THT <u>Through Hole Technology</u>: A technique for populating part or all of circuit board where components are inserted into plated through holes (vias). When all the components have been inserted they can be subsequently soldered to the board, typically either a wave or hand soldering technique is utilised

### Names for parts of an electronic assembly

(adapted from http://www.maxmon.com/glossary.htm)

| Artwork       | Actual circuit layout (including pads and tracks) as used to manufacture a circuit board                                                                                                                                                                                                                                                                                       |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Circuit Board | Generic name for several interconnection methods; the board may be rigid flexible<br>and may be either single sided, double sided, or multilayered.                                                                                                                                                                                                                            |

| Die           | Generic name for an unpackaged integrated circuit (IC)                                                                                                                                                                                                                                                                                                                         |

| Flux          | Chemical applied to the solderable surfaces (e.g. PCB pad or UBM) that removes the oxides that will inevitably impede the solder "wetting", therefore a good solder joint to form.                                                                                                                                                                                             |

| Lead frame    | A metallic frame containing leads and a base such that an unpackaged IC may be attached. Once correctly positioned the outer part of the frame can be cut away and the leads bent into the required shape.                                                                                                                                                                     |

| Pad           | A conductive area on the substrate where one of the following may occur: a) the pad may be a designated area where a component is to be placed; b) the pad may connect to a via (e.g. in the case of double sided/ multi-layer PCBs) c) the pad may allow for external probing.                                                                                                |

| Schematic     | Name for a theoretical (drawn) circuit diagram                                                                                                                                                                                                                                                                                                                                 |

| Solder        | An alloy consisting of tin and other metal(s) used to join less fusible materials together. The solder has a low melting temperature (compared with the materials it is joining) and this allows the tin in the solder to "wet" the other materials (typically either copper, gold or nickel) and form the intermetallic layer that is necessary for an adequate solder joint. |

| Solder paste  | microscopic solder balls combined with flux that have high viscosity and can be<br>dispensed on to a designated area. Normally this area is a pad on the board where a<br>component is intended to be placed later.                                                                                                                                                            |

vii

**UBM** <u>Under Bump Metallurgy:</u> A layer of material that is able to wet with solder (typically gold or nickel) that is superimposed on a material that the solder would otherwise not wet with. The material is superimposed on the designated area by a process such as electroplating.

| Solder bump  | Solder that has been placed on a pad and then reflowed (heated to a sufficient temperature that the solder melts) and the surface tension of the molten solder pulls the solder into a spherical shape. Upon cooling down, this spherical shape is retained.                                        |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Solder joint | Solder that is connecting the pad on the substrate with the corresponding connection on the component                                                                                                                                                                                               |

| Solder Mask  | Layer applied to surface of the substrate to prevent solder wetting any other metallic surface; holes are patterned into the mask to correspond with the pads on the substrate.                                                                                                                     |

| Substrate    | The base layer for any integrated circuit, hybrid, multi- chip module or circuit board.<br>A substrate may be manufactured from several materials depending on the product<br>specification requirements. Typical materials include FR4, semiconductors and those<br>that are ceramic based.        |

| Track        | A narrow conductive connection between two different pads such that a component<br>may emit or receive signals. The tracks are superimposed on the circuit board and<br>may relay signals with other components or they may run to an external connection to<br>a parent/ child board or component. |

| Via          | A hole drilled in a circuit board to link two or more conductive layers of a substrate.; the hole may be bare in the case when used in through hole technology or may be filled/lined with a conductive material when used for a double sided/ multi-layered PCB                                    |

| Underfill    | An epoxy based material utilised in flip chip technology applied between the chip and<br>the parent substrate. The purpose is to mechanically couple the chip and substrate<br>such that stresses resulting from thermal expansion mismatches are distributed.                                      |

| Wafer        | A thin slice cut from a pure semiconductor                                                                                                                                                                                                                                                          |

## IC package configurations

Wire Bonding The process of connecting the pads on an unpackaged IC to corresponding pads on a substrate using fine wires. Wire bonding may also be used to connect the pads on an unpackaged IC, hybrid or multi chip module to the leads of a component package.

Area Array A packaging technology where the area of a components base is utilised for interconnection purposes.

**Grid array** A packaging technology where components external connections are arranged as an array on the base of the package; there are several types

- Pin Grid Array The interconnection layer consists of conducting pins or leads

- Pad Grid Array The external connections are pads

- Ball Grid Array Similar to that of the Pad Grid Array however the pads have solder balls attached to them.

Peripheral array A packaging technology where only the area near the edges of the board are used for interconnection purposes.

## Chip Assembly Procedures

- **Reflow** A method of soldering surface mount components attached to a board with solder paste. The populated board is passed through an oven on a conveyor where it is progressively heated to a temperature sufficient to melt the solder paste such that a good connection is formed.

- Solder Wetting The alloying procedure that occurs when the tin element of solder comes into contact with a compatible solid material. The tin atoms join with the pad/UBM material and a resultant intermetallic compound is formed; the intermetallic is a necessary product to ensure that an adequate joint has been formed.

- Stencil printing A technique for depositing solder paste on to either a substrate (surface mount) or a wafer (flip chip). The wafer/ substrate is placed on the surface and a stencil with holes (for the pads) is correctly aligned. Solder paste is then placed on top of the stencil and a squeegee is then passed across the pattern such that the solder paste is forced through the holes and onto the pads. Following this the wafer or substrate is inspected and either is populated with components or reflowed (depending on method used).

- Vapour phase A method of soldering surface mount components attached to a board with solder paste. The populated board is lowered into a tank containing boiling hydro carbons that consequently form a vapour cloud. The temperature of the vapour cloud is sufficient to melt the solder. However this method is now becoming less popular due to environmental legislations.

- Wafer bumping A flip chip technique where spheres are formed on the dies pad. Solder paste is deposited on the pads using a stencil printing technique. The wafer is then passed through a reflow oven such that the solder melts and solidifies resulting in spherical solder "bumps". Once complete, the wafer can be diced and individual die can be subsequently placed on the appropriate pad.

- Wave soldering A method of soldering through hole components to a circuit board. A wave of molten solder is generated in a tank and the board is passed over the solder wave by a conveyor, the wave then catches the bottom and the components are soldered.

### Miscellaneous

- Solder Wetting The alloying procedure that occurs when the tin element of solder comes into contact with a compatible solid material. The tin atoms join with the pad/ UBM material and a resultant intermetallic compound is formed; the intermetallic is a necessary product to ensure that an adequate joint has been formed.

- **Thermal Cycle** A product verification method whereby a component is physically heated and cooled according to a predefined specification. Thermal cycling is normally carried out in an oven such that the temperature of the component is dictated by the temperature of the surrounding environment.

**Power cycle** A product verification method whereby a component generates heat internally as a result of a power load applied to it.

# Symbols used

| R<br>t<br>T<br>U | Resistant measurement<br>Time measurement<br>Temperature measurement<br>Fluid velocity measurement | (Ω)<br>(s)<br>(°C OR °K)<br>(m/s) |  |

|------------------|----------------------------------------------------------------------------------------------------|-----------------------------------|--|

| k i              | Thermal Conductivity                                                                               | $(w/M^2xK)$                       |  |

| h                | Convection heat transfer coefficient (w/M <sup>2</sup> xK)                                         |                                   |  |

| R <sub>obs</sub> | Measured resistance of assembly v                                                                  | with power applied                |  |

| R <sub>RT</sub>  | Measured resistance of assembly at room temperature                                                |                                   |  |

| T <sub>s</sub>   | Temperature of a body surface                                                                      |                                   |  |

| T <sub>∞</sub>   | Ambient temperature (temperature of surroundings)                                                  |                                   |  |

| U <sub>∞</sub>   | Free flow fluid velocity                                                                           |                                   |  |

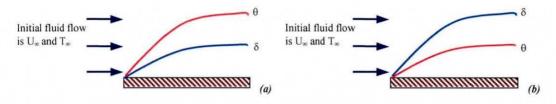

| δ                | Velocity boundary layer                                                                            |                                   |  |

| θ                | Thermal boundary layer                                                                             |                                   |  |

| v                | Kinnematic viscosity                                                                               |                                   |  |

| h <sub>x</sub>   | Specific convection heat transfer of                                                               | coefficient                       |  |

| x                | length                                                                                             |                                   |  |

| Re <sub>x</sub>  | Reynolds number for given condit                                                                   | tions                             |  |

| Nu <sub>x</sub>  | Nusselt number for given conditio                                                                  | ons                               |  |

x

# **Chapter 1: Introduction**

## 1.1: Trends in the Manufacture of Electronic Products

### Every 18 months the number of transistors found on a typical silicon chip doubles (Moore's law 1965)

In the present consumer electronics climate, there are persistent demands for a product to be of superior quality and performance, yet smaller size than its predecessor. To illustrate the effects of just 6 years of product improvement, table 1.1 shows the volume reduction of a typical domestic "camcorder" manufactured at two different periods in the 1990's (1,2). In addition, the seemingly continuous increase in computer processing speeds and memory capacity are well known.

| Feature and the second | 1992                          | <b>1998</b> : 1999, 1999, 1999, 1999, 1999, 1999, 1999, 1999, 1999, 1999, 1999, 1999, 1999, 1999, 1999, 1999, 1999, 199 |

|------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| No. of components      | 1800                          | 848                                                                                                                     |

| Density                | 12 components/cm <sup>2</sup> | 21 components/cm <sup>2</sup>                                                                                           |

| Volume                 | 2380cm <sup>3</sup>           | 1598cm <sup>3</sup>                                                                                                     |

| Viewing unit           | B/W charge coupled device     | Colour LCD                                                                                                              |

Tables 1.1a: Illustration of electronic trends over 6 years (1)

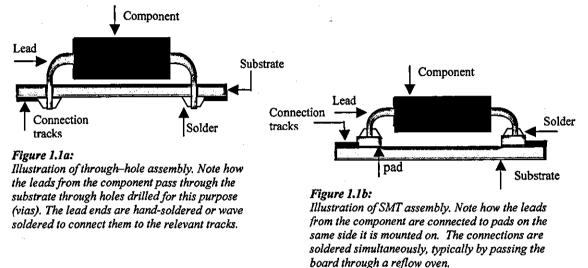

Many of these reductions in size and increases in performance were due to persistent changes in manufacturing methods and endeavour to reduce package profile. Possibly the most significant initiative in package reduction was the introduction of the **Printed Circuit Board** (PCB). PCBs are typically manufactured from FR4, which is a glass fibre epoxy laminate though they may also be ceramic based. The PCB initially had its electronic components secured to it by passing the connecting leads through the board in specified positions and then soldering them to tracks that were superimposed on the PCB (Through Hole Technology fig 1.1a). The components were originally attached to the board by hand soldering where an operator soldered each connection with a soldering iron; this method was not only slow but also potentially introduced human error. Therefore a more efficient manufacturing method was sought, which greatly reduced the risk of human error and allowed several components on a PCB to be soldered simultaneously. This initially lead to the introduction of *wave soldering* where this allowed a board populated with through-hole components to be mass-soldered by a molten solder wave passed underneath the board; the subsequent drive

for lower profile led to the development of Surface Mount Technology (SMT). In contrast to the through hole technology, SMT PCBs were manufactured with their tracks on the same side of the board as the soldering was carried out using either a *vapour phase* or *solder paste "reflow" oven* soldering where all the mounted components could be soldered simultaneously. These simultaneous soldering methods increased the production rate as well as offering greater assurance of product quality.

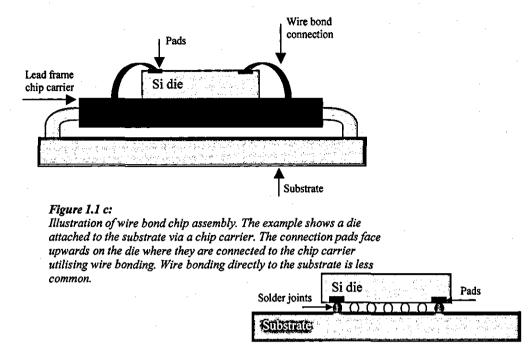

Initially the components connected to the board were single passive devices such as resistors, capacitors and transistors. In subsequent years, there were developments of integrated circuits based on silicon that required several input and output connections. As the capabilities of a single packaged electronic component increased, the number of necessary Input/Output (IO) connections also inevitably increased. These were accommodated for by utilising a lead-frame where several leads would pass from the component (typically a silicon die) and connect to the board as shown in figure 1.1c. To connect the pads of the silicon die to the lead frame, wire bonding was used and until the present day has been used to successfully secure dies with many IO connections. This method was available for through hole assembly, however, its application to SMT allowed for smaller lead profiles and smaller pad dimensions to be implemented in the chip/board design, therefore providing a greater number of potential connections for a given area. In order to avoid the additional packaging associated with the lead frame, the die was directly wire bonded to the PCB in some devices.

In recent years the drive towards smaller products with more functionality has led to the introduction of other packaging methods that enable the maximum number of IO

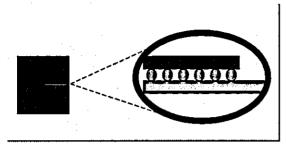

connections in the minimum area. Typically this has required the introduction of area array devices where an entire face of a chip can be utilised for connections to and from the substrate. However this is a limitation of the conventional wire bonding interconnection where only area close to the face edges can be used for connection pads, therefore new technologies have been developed to accommodate for this connection method. For SMT the area array connections are made using solder balls in place where the connections are to be made; this connection methodology is known as Ball Grid Array (BGA). Variations of this methodology exist, a common example is when the solder balls are substituted for pins resulting in a Pin Grid Array (PGA). The ultimate extension of the reduction in package size is the removal of all packaging and direct connection of the Si chip to the PCB surface. The technique of flip chip assembly enables bare die to be connected to a PCB using solder or a conducting adhesive as shown in figure 1.1d. At present, there is a considerable interest in flip chip assembly; in particular, the mobile telecommunications industry has benefited due to increased research in flip chip resulting in economic mass production of smaller devices (1). Flip chip was first researched in the 1950's by Lucent Technologies (formerly AT&T), and later enhanced when IBM Yasu developed the Controlled Collapse Chip Connection (C4) process in the 1960's. In contrast to the mature wire bond manufacturing method, flip chip involves mounting a chip with its topside down and interconnections made by solder bumps to a matching pad array on the substrate (typically a PCB) for the case of Direct Chip Attach (DCA) or it may be attached to an intermediate body in the case of a Multi-Chip Module (MCM) where connections to the substrate are typically made utilising BGA technology.

#### Figure 1.1d:

Illustration of flip chip on board assembly method or DCA. In this instance, the chip has been directly attached to the board, though can be attached to a chip carrier first. Note the much shorter distance an electronic signal would have to travel through compared with the wire bond example as the pads are themselves closer to the substrate. The grey solder balls show the more common peripheral array solder joints while the clear solder balls represent the extra potential connections if an area array grid pattern is used.

## **1.2:** Advantages of Flip Chip Technology

With increasing performance and consumer demands, flip chip is likely to become ubiquitous in electronics packaging and assembly, especially as the limits are being reached for wire bonding technology in terms of IO connections per available area. This enables the continuation of the packaging trends witnessed in recent years. As previously stated, the manufacturing of mobile phones greatly utilises flip chip technology and it is anticipated that other technologies will soon adopt this trend. There are several reasons why flip chip is an attractive manufacturing method compared with SMT or wire bonding (3,4), among the obvious are:

Lower package profile: As stated in section 1.1, the consumer demands smaller packages with increasing functionality. Flip Chip On Board (FCOB) or DCA is the smallest packaging technology as it eliminates the peripheral wires or leads that are present in wire bond and SMT manufacturing methods respectively. In addition as the

connections are underneath the chip (in contrast to around the perimeter) they not only allow denser connections, but also free up extra space on the substrate.

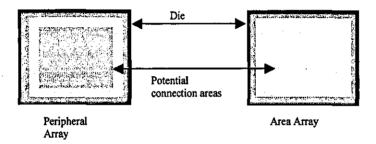

Area Array packages: The ever-increasing number of IO connections required from a die are a significant factor when considering manufacturing processes; flip chip enables full area array interconnect as opposed to only the peripheral areas of a die as is the case with both wire bonding or conventional surface mount devices. Therefore extra area of the board can be utilised for IO connections without having to reduce the pad size on the peripheral array chips. Figure 1.2 shows the available pad area for peripheral array and the potential connection space when area array is implemented, it can be seen that a much larger area on the die can be utilised for interconnections.

Figure 1.2:

Illustration of the potential connection space available if an area array pattern is used, compared with the more conventional peripheral array available for wire bond. The grey area represents the die while the red area shows the potential connection area for the respective methods

Shorter IO connections: The reduced distance travelled by the electrical signal (a flip chip solder joint height is typically less than 100µm tall, compared to the wire bond or lead frame which may be several mm long) enables signals to be relayed faster; this feature is becoming more critical as the speeds of microprocessors are constantly increasing. In addition to the speed increase, the shorter distance implies less impedance and noise.

*Manufacture economy:* According to Lau (4), the cost of attaching a die to a PCB using wire bond technology is largely dependent on the number of connection pads the chip contains; for example, assuming all other aspects of a die are constant, it may be the case that only 4 wire bonders are necessary for a die with 30 IO pads, whereas 70 wire bonders are required for a die with 600 pads (4). Clearly as the amount of connection points per chip increases an unacceptably large number of wire bonders

will be needed. Conversely, for flip chip assembly, only one reflow oven is required regardless of the amount of pads on chips, it can therefore clearly be seen that as the amount of pads increases (as it will inevitably, as consumer demands continue to grow) the wire bond method will become very impractical and uneconomical if not totally prohibitive. Furthermore, as a reflow soldering process is used to secure the flip chip to the board it is directly compatible with conventional SMT methods.

## 1.3: Disadvantages of Flip Chip Technology

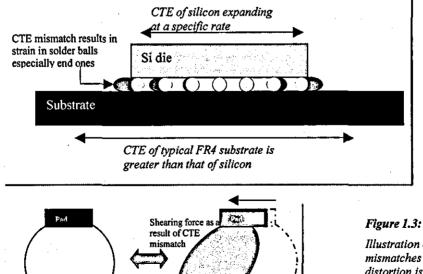

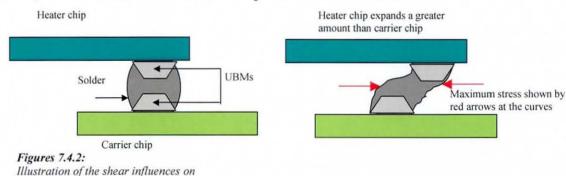

Though there are several disadvantages of flip chip (4), the fundamental drawback of flip chip is the potential impact of thermal effects on product reliability; when an electronic die is in service (or powered on) it is well known that the temperature will increase in proportion with the power level supplied. Consequently the die will expand according to its Coefficient of Thermal Expansion (CTE); in addition, the substrate may also heat up and expand with respect to its own CTE. The CTE values may be substantially different between the die and the substrate and this will result in a shear stress in the small solder joints as shown in figure 1.3. While materials thermally expanding at different rates is not a new concept in electronics reliability assessment, it is especially emphasised from the flip chip perspective due to the small geometries of the solder joints (height is typically <100 $\mu$ m); resulting in little room for flexibility. The wires and lead frames used in wire bonding and surface mount technology respectively, are long and flexible enough to absorb the CTE mismatches between the die and substrate.

Pad

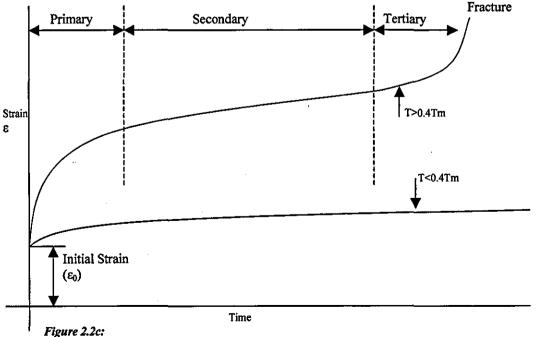

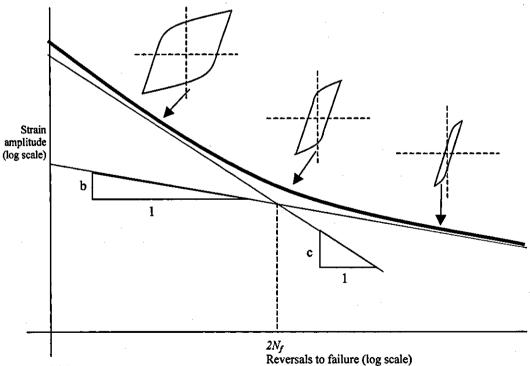

Illustration of effects of CTE mismatches on solder joints. The distortion is exaggerated. The light grey bumps are in the cool state while the dark grey bumps are in the hot state As the product experiences temperature changes either due to testing or use in service, the die and substrate will be continuously expanding and contracting, therefore increasing and decreasing the shear stress. There are several failure mechanisms that may be invoked by this shearing action; they may be instantaneous such as plastic deformation, or they may be time dependent as is the case with creep and fatigue (5,6). These effects shall be looked at in more detail in subsequent chapters.

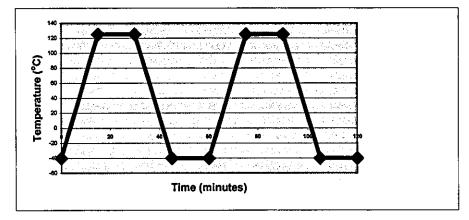

### **Product Reliability Evaluation methods**

Obviously products require some form of testing to investigate the extent these mechanisms mentioned contribute to the demise of a product. A common method used for assessing damage mechanisms is thermal cycling. This involves heating and cooling a component isothermally and holding it at the high/low temperatures. The isothermal temperature of the assembly has been considered adequate to investigate the CTE mismatches of the die and the substrate and to invoke the time dependent mechanisms described. This method has been used for many years to demonstrate the reliability of electronic devices including flip chip. However this is a somewhat artificial test condition and may be a misrepresentation of the stresses an assembly would endure in a real environment. The main issue regarding thermal cycling is that the heat source is supplied from an external source, hence is independent of the testvehicle (they are normally placed in an oven and heated this way) resulting in an isothermal temperature distribution. In reality the heat from a component will be generated internally as a result of the power supplied to it. As a consequence, the temperature of the component may be significantly greater than the substrate; hence an anisothermal temperature distribution exists. Such an anisothermal temperature distribution is more likely to be captured using an alternative product testing method, namely power cycling. Power cycling involves supplying a specified power level to an assembly for a given time period and then removing the power for an equivalent "off" period. The heat involved in a power cycle is generated internally (i.e. from within the device) and the temperature change endured by the component when the power is supplied/removed forms a complete ON/OFF power cycle which is equivalent to the conventional high/low thermal cycle; the fundamental drawback of power cycling is that in most cases the ambient temperature cannot be regulated, nor can a strict maximum/minimum temperature be enforced. Compared with

conventional thermal cycling, the temperature of the assembly is "an-isothermal" where the substrate is typically cooler than the component. This leads to a range of stress distributions within the device that are difficult to predict and can be unexpected.

For devices where there is no CTE match between the component and the substrate, power cycling is likely to show similar results to thermal cycling. However in situations where components and substrates are of the same material, which is particularly important for Multi-Chip Modules (MCMs) composed of Si chips flip chip attached to a Si substrate, thermal cycling is unlikely to stress the device and therefore power cycling will be more representative, as has been demonstrated by Trigg & Corless (7). They thermally cycled silicon on silicon assemblies (hypothetically a good CTE tailored scenario) and found that after 500 cycles that there was only one failure, that was attributed to earlier rework of the chip. However, when the components were power cycled, a greater number of assemblies were observed to fail, implying a different stress distribution from the case when they were thermal cycled. It was anticipated that there was an anisothermal temperature distribution present as the chip may both heat up faster than the substrate chip (7) and reach a higher temperature; this effect may be enhanced depending on the type of substrate the assembly is mounted on and the external cooling conditions. Trigg and Corless have highlighted the potential hazards of being totally dependent on thermal cycling and highlights why power cycling may be a more reliable testing method.

## 1.4: Thesis Aims

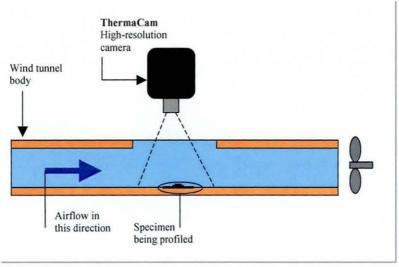

The aim of this thesis is to investigate the effect of power cycling on the temperature, stress and reliability of a flip chip assembly. The work involved the manufacture of silicon on silicon multi-chip module assemblies that were power cycled to investigate their reliability and such that the temperatures of the different "parts" of the assembly could be seen/measured. The assemblies were attached to either an FR4 or a copper substrate such that the different thermal properties of the substrates were also investigated. FR4 is a conventional electronics substrate while the copper substrate represents a thermally enhanced assembly such as when a heat sink is fixed to a component. In order to control the external variables, the experiments were conducted in a wind tunnel such that the airflow could be regulated. Finite element modelling of the assembly was also carried out to understand the thermal effects and consequent stress distributions.

فالمصيبية وتنجو البرداف بالمتهمية بالمصيد وللم

### References

- 1) J.H. Lau "Low Cost Flip Chip Technologies" McGraw-Hill, 1999, Chapter 1

- J.H. Lau & S.W. Ricky Lee "Chip Scale Packaging, Design, Materials, Process, Reliability and Applications" McGraw-Hill, 1999, Chapter 1

- 3) S.G. Konosowski, & A.R. Helland "Electronic Packaging of High Speed Circuitry" Electronic Packaging and Interconnection Series McGraw-Hill, 1997

- 4) J.H. Lau "Low Cost Flip Chip Technologies" McGraw-Hill, 1999, Chapter 4

- 5) Peter M. Stipan, B. C. Beihoff, M.C. Shaw "Electronics Package Reliability and Failure Analysis: A Micro Mechanics Approach" *The Electronic Packaging Handbook IEEE press, 2000, Chapter 15*

- 6) Robert D Malucci "Accelerated Testing of Tin Plated Copper Alloy Contacts" IEEE Transactions on Components and Packaging Technology Volume 22, March 1999, pages 53-60

- 7) A.D. Trigg & A.R. Corless "Thermal Performance and Reliability Aspects of Silicon Hybrid Multi-Chip Modules" 40<sup>th</sup> Electronic Components and Technology Conference, 1990, pages 592-9

## Chapter 2: Literature Review

As outlined in the introduction, the area of electronics reliability is strongly affected by the thermal issues regarding an assembly. This is especially apparent in the area of flip chip technology where the CTE mismatch may cause excessive shear strain in the joints. These effects however, can be minimised by applying a cooling mechanism such as a fan or heat sink. This review starts off by analysing the more novel approaches to thermal management of high power devices, before looking at reliability testing (thermal/power cycling methods) in more detail.

## 2.1: Higher Power Flip Chip Assemblies

Prior to a discussion of issues regarding high power flip chip assemblies it is first necessary to define what is meant by "high power." Kranz (1) defines a high power device as one with a power density greater than 6.2 Watts/cm<sup>2</sup>. Though clearly this is an arbitrary figure, it can serve as an approximate guide to differentiate between high and moderate power levels (e.g. much greater than 6.2 Watts/cm<sup>2</sup> may be confidently considered high and lesser values moderate). An obvious application area of high-powered flip chip is an alternative packaging method for computer microprocessors. Computer technology (especially microprocessors) are approaching the limits that conventional wire bonding may offer with respect to the increasing number of IO connections required from a given density. This increasing number corresponds with a smaller connection pitch required resulting in microprocessor manufacturers considering flip chip as viable alternative to packaged components (2, 3, 5).

### **General Application Areas**

There have been some studies considering the possibility of flip chip packaging for microprocessors. For example Darnauer et al (2), considered the feasibility of flip chip packaging for the next generation of microprocessors by comparing low cost organic ball grid array against thin film ceramic land grid array. The feasibility study was conducted with respect to electrical noise control and specifically the study focused on two types of noise emissions, namely a) core noise, and b) simultaneous

switching output (SSO) noise. The noise measurements were recorded and compared against noise recorded from the conventional wire bonded packages and the results were analysed for each parameter separately. The results showed no significant reduction in core noise over conventional wire bonding technology, nonetheless, positioning a chip capacitor near the noise source may compensate for this. SSO emissions, on the other hand, had significantly improved over the previous generation microprocessor, with the resulting noise emission reduced by a factor of 2. In addition, the ceramic land grid array demonstrated superior performance to plastic ball grid array due to the lower impedance of its power plane.

This investigation is useful as it certainly gives credibility to the next generation microprocessor being flip chip based, though there are several crucial issues that have not been considered. Furthermore, it should be noted that Darnauer only considers the feasibility from an electrical perspective (that is to say "*is* the product capable of functioning adequately using flip chip technology?") and does not address the mechanical and thermal performance of such packages.

### **Thermal Management**

There is limited published data on thermal management for high power flip chip assembly, however most methods involve thermally enhancing the package, and typically enhancing the substrate material. For most electronic applications, the utilised substrate material is FR4, which has a thermal expansion rate approximately 4 times that of silicon. In order to address the CTE mismatch issues highlighted, a potential substrate material should have a thermal expansion rate close to that of silicon, and good thermal conductivity.

Gilbert et al (3) illustrated the temperature reached by high power modules when they performed a Finite Element (FE) simulation of a signal processor for military applications. The module consisted of 16 GaAs chips  $650\mu m$  thick mounted on a copper and polyimide flex 100 $\mu m$  thick mounted on a 100 $\mu m$  thick alumina substrate. There were two 6W power chips in the central region of the board and it was calculated that left untreated the chips would exhibit a thermal resistance of 7°C/W, resulting in a potential temperature rise of 42°C per chip. An array of metal vias was

inserted into the substrate such that each chip had a via running from the base of the chip vertically through the polyimide and into the substrate. The via was in contact with approximately 7% of the chip area and subsequent simulations indicated that the chips would have a thermal resistance of only 1°C/W. The thermal performance was greatly improved by the vias providing a highly conductive path between the chips and the substrate.

Traditional substrate materials for high power MCMs include approximately 1mm thick alumina or 600-650µm silicon wafers. However in more recent times, alternative materials including sapphire and metal matrix composites containing silicon carbide are becoming popular. According to Wu et al (4) sapphire is popular as it is available at reasonable costs and in large wafer sizes, whereas silicon carbide is desirable as it provides excellent thermal conductivity. In addition to this, the overall performance of the assembly can be improved by altering the die package.

Ulrich and Rajan (5) foresaw a novel approach to thermal management of high power flip chip assembly. Rather than provide a path for heat flow through the joints and the substrate and finally to a heat sink, their theory was to conduct as much heat from the die as possible therefore bypassing the interconnection layer completely. The only way this could be done was to immerse the chip in liquid nitrogen. Operating a component at these cryogenic temperatures offers many additional benefits, for instance the thermal conductivity of the silicon and copper are greatly increased and furthermore, the rate of many temperature dependent failure mechanisms, such as corrosion and electro-migration are greatly reduced therefore resulting in good package improvements. Initial tests (5) involved bare chips directly exposed to liquid nitrogen and the silicon yielded excellent thermal resistance (0.15°K/W), however it is undesirable to have bare chips in a microelectronic assembly from a reliability perspective. After a metal lid was placed on the test vehicle the thermal resistance rose to 4°K/W due to a gas gap between the lid and the chip; this gap increased the thermal resistance to 18°K/W resistance and forced 80% of the heat generated to flow through the solder bumps and the substrate.

## 2.2: Thermal Cycling and associated Phenomena

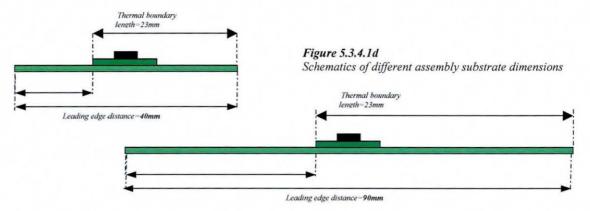

### **Thermal Cycling Description**