This item was submitted to Loughborough's Research Repository by the author. Items in Figshare are protected by copyright, with all rights reserved, unless otherwise indicated.

## An assessment of dual-rail encoded on-line test methodologies and their impact on ASIC/FGPA design

PLEASE CITE THE PUBLISHED VERSION

**PUBLISHER**

© David Thulborn

LICENCE

CC BY-NC-ND 4.0

REPOSITORY RECORD

Thulborn, David. 2019. "An Assessment of Dual-rail Encoded On-line Test Methodologies and Their Impact on ASIC/FGPA Design". figshare. https://hdl.handle.net/2134/13754.

This item was submitted to Loughborough University as a PhD thesis by the author and is made available in the Institutional Repository (<a href="https://dspace.lboro.ac.uk/">https://dspace.lboro.ac.uk/</a>) under the following Creative Commons Licence conditions.

C O M M O N S D E E D

#### Attribution-NonCommercial-NoDerivs 2.5

#### You are free:

· to copy, distribute, display, and perform the work

#### Under the following conditions:

Attribution. You must attribute the work in the manner specified by the author or licensor.

Noncommercial. You may not use this work for commercial purposes.

No Derivative Works. You may not alter, transform, or build upon this work.

- For any reuse or distribution, you must make clear to others the license terms of this work.

- Any of these conditions can be waived if you get permission from the copyright holder.

Your fair use and other rights are in no way affected by the above.

This is a human-readable summary of the Legal Code (the full license).

Disclaimer 🗖

For the full text of this licence, please go to: <a href="http://creativecommons.org/licenses/by-nc-nd/2.5/">http://creativecommons.org/licenses/by-nc-nd/2.5/</a>

## BLDSC 10: - DX 203156

| L | Loughborough |

|---|--------------|

| • | University   |

## Pilkington Library

| Author/Filing Title | TH   | OLBORA | ه ريا |        |

|---------------------|------|--------|-------|--------|

| Accession/Copy No.  | 0401 | 4727c  |       | •••••• |

| Vol. No             |      | <      |       |        |

|                     | LoAn | COPY   | ٠.    |        |

|                     |      |        |       |        |

|                     | ·    |        |       |        |

|                     |      |        |       |        |

|                     |      |        |       |        |

# AN ASSESSMENT OF DUAL-RAIL ENCODED ON-LINE TEST METHODOLOGIES AND THEIR IMPACT ON ASIC/FPGA DESIGN

by

David Thulborn, B.Sc., M.Sc.

A Doctoral Thesis.

Submitted in partial fulfilment of the requirements

for the award of

Doctor of Philosophy

of

Loughborough University.

March 1997

© by David Thulborn 1997

|                                                                |                                       | a caalah jiraa da<br>Galama ayyahad<br>Galama a |                    |

|----------------------------------------------------------------|---------------------------------------|-------------------------------------------------|--------------------|

|                                                                |                                       |                                                 | TIY<br>TAMMAN      |

| K<br>E FASTO<br>SI<br>SI SI S | 0,4                                   | 97                                              | T. EIREMENT        |

| Ciro                                                           | a a a a a a a a a a a a a a a a a a a | ٧                                               | The section of the |

| No.                                                            | oto 1                                 | 47.2                                            | 70                 |

#### **ABSTRACT**

The testing of fabricated Integrated Circuits (IC's) is of great concern to production engineers and circuit designers alike. With the complexity of Very Large Scale Integrated (VLSI) circuits increasing every year, the problem of testing the fabricated designs is becoming acute. Several methods for reducing the burden of IC testing have been incorporated into the designs being tested thus giving rise to the phrase Design For Test (DFT).

This thesis aims to understand how dual rail encoding of digital data can affect the different characteristics of electronic circuits. More specifically, it investigates a novel on-line test methodology called IFIS (If it Fails, It Stops), and its impact upon the design and implementation of electronic circuits intended for Application Specific Integrated Circuit (ASIC) and Field Programmable Gate Array (FPGA) technologies.

The first two studies investigate the characteristics of the IFIS methodology to determine the most efficient and effective encoding scheme, protocol rules and feedback structures required for data processing. The third study investigates a series of possible improvements to the design of IFIS cells and determines the most efficient method of designing cells using the IFIS methodology. The final study investigates the feasibility of IFIS using a 'real life' commercial UART re-engineered using the IFIS methodology.

The outcome of this work is an identification and characterisation of the factors which influence the performance and implementation cost of the IFIS methodology.

#### **ACKNOWLEDGEMENTS**

I wish to take this opportunity to offer my sincere thanks to my supervisor Professor Simon Jones for his support, criticism, encouragement and technical guidance throughout this period of research. I shall always be grateful to him.

I also wish to thank all the members both former and present, of the Electronic Systems Design Group based at Loughborough University, for their help and encouragement. They have been the source of many useful and stimulating discussions. In particular, I wish to thank Mr. Mark Gooch and Mr. Julian Yeandel in this respect. I would especially like to thank Mr. Julian Yeandel for producing the top level structure of the 'C' model used for the verification of the UARTs.

To my parents I extend my warmest thanks. I wish to thank them for the education they have afforded me and for their support and encouragement over the last 3 years. Also, I must send a very special thank you to my girlfriend Claire and son Michael for always being there to see me through.

For my financial support I wish to thank the Engineering and Physical Sciences Research Council, without whom this work would not have been possible.

Finally, I wish to send a special thank you to Mr. Steve Stavrou whose enthusiasm and humour have kept me motivated.

## TABLE OF CONTENTS

| . Pag                                             |

|---------------------------------------------------|

| Abstract i                                        |

| Acknowledgements ii                               |

| Statement of Originality iii                      |

| Table of Contents iv                              |

| CHAPTER ONE                                       |

| INTRODUCTION                                      |

| <b>1.1 Introduction</b>                           |

| <b>1.2 Motivation</b>                             |

| 1.2.1 Off-line Testing                            |

| 1.2.2 On-line Testing                             |

| <b>1.3</b> Aims of the Thesis                     |

| 1.4 Structure of the Thesis                       |

| CHAPTER TWO                                       |

| <b>REVIEW</b>                                     |

| <b>2.1 Objectives of Review</b>                   |

| <b>2.2 Motivation</b>                             |

| 2.3 Hardware Redundancy                           |

| 2.3.1 Duplication With Comparison                 |

| 2.3.2 Triple Modular Redundancy                   |

| 2.3.3 N Modular Redundancy                        |

| 2.3.4 Summary of Hardware Redundant Techniques 14 |

| <b>2.4</b> Time Redundancy                        |

| 2.4.1 Alternating Logic                           |

| 2.4.2 Recomputing With Shifted Operands 16        |  |

|---------------------------------------------------|--|

| 2.4.3 Recomputing With Swapped Operands 17        |  |

| 2.4.4 Summary of Time Redundant Techniques 18     |  |

| 2.5 Information Redundancy                        |  |

| 2.5.1 Duplication Codes                           |  |

| 2.5.1.1 Alternate Data Retry                      |  |

| 2.5.1.2 Summary of Duplication Codes 22           |  |

| 2.5.2 Arithmetic Codes                            |  |

| 2.5.2.1 Non-Separable Arithmetic Codes 22         |  |

| 2.5.2.2 Separable Arithmetic Codes 23             |  |

| 2.5.2.3 Summary of Arithmetic Codes 25            |  |

| 2.5.3 Unidirectional Error Detecting Codes        |  |

| 2.5.3.1 Unordered Codes                           |  |

| 2.5.3.1.1 Non-separable Unordered Codes . 27      |  |

| 2.5.3.1.2 Separable Unordered Codes 27            |  |

| 2.5.3.2 t-Unidirectional Error Detecting Codes 28 |  |

| 2.5.3.2.1 Non-separable t-Unidirectional          |  |

| Error Detecting Codes 28                          |  |

| 2.5.3.2.2 Separable t-Unidirectional Error        |  |

| Detecting Codes 29                                |  |

| 2.5.3.3 Burst Unidirectional Error                |  |

| Detecting Codes 30                                |  |

| 2.5.3.3.1 Separable Burst Unidirectional          |  |

| Error Detecting Codes 31                          |  |

| 2.5.3.4 Summary of Unidirectional Error           |  |

| Detecting Codes                                   |  |

| 2.5.4 Parity Based Codes                          |  |

| 2.5.4.1 Bit-per-Word Parity                       |  |

| 2.5.4.2 Interlaced Parity                           | 35 |

|-----------------------------------------------------|----|

| 2.5.4.3 Parity Check Matrix                         | 35 |

| 2.5.4.4 Summary of Parity Based Codes               | 36 |

| 2.5.5 Summary of Information Redundant Techniques . | 36 |

| 2.5.6 Totally Self Checking Checkers                | 39 |

| 2.5.7 Partially Self Checking Checkers              | 40 |

| 2.6 Summary                                         | 40 |

| <b>2.7 Conclusions</b>                              | 42 |

| CHAPTER THREE                                       |    |

| OVERVIEW OF INVESTIGATIONS                          | 43 |

| 3.1 Objectives of Chapter                           | 43 |

| 3.2 Aims of Research                                | 43 |

| 3.2.1 Statement of Research Objectives              | 44 |

| 3.3 Experimental Vehicles                           | 45 |

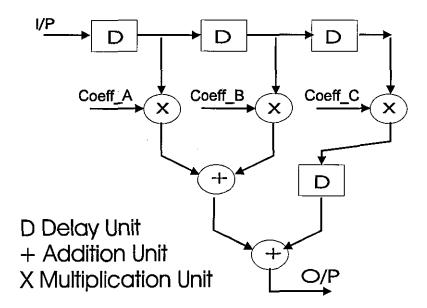

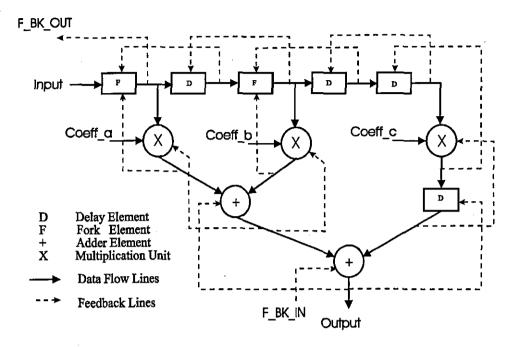

| 3.3.1 FIR Filter                                    | 45 |

| 3.3.2 UART                                          | 45 |

| 3.3.3 System Environment                            | 46 |

| 3.4 Introduction to Investigations                  | 47 |

| CHAPTER FOUR                                        |    |

| IFIS ON-LINE TEST METHODOLOGY                       | 49 |

| 4.1 Objectives of Chapter                           | 49 |

| 4.2 Motivation                                      | 49 |

| 4.3 IFIS Encoding Schemes                           | 50 |

| 4.3.1 IFIS 1 Encoding Scheme                        | 50 |

| 4.3.2 IFIS 2 Encoding Scheme                        | 51 |

| 4.4 IFIS Processing Methods                         | 52 |

| 4.4.1 Elastic Flocessing               | ) ) |

|----------------------------------------|-----|

| 4.4.2 In-Elastic Processing 5          | 54  |

| 4.4.3 Data Driven Processing           | 56  |

| 4.5 IFIS Feedback Structures 5         | 57  |

| 4.5.1 Self Feedback                    | 58  |

| 4.5.1.1 In-elastic Processing 5        | 59  |

| 4.5.2 Successor Feedback 6             | 60  |

| 4.5.2.1 Elastic Processing 6           | 51  |

| 4.5.2.2 In-elastic Processing 6        | 2   |

| 4.5.2.3 Data Driven Processing 6       | i3  |

| 4.5.3 Successor Successor Feedback 6   | 3   |

| 4.5.3.1 Elastic Processing 6           | 4   |

| 4.5.3.2 In-elastic Processing 6        | 5   |

| 4.5.3.3 Data Driven Processing 6       | 5   |

| 4.5.4 Successor and Self Feedback 6    | 7   |

| 4.5.4.1 Elastic Processing 6           | 8   |

| 4.5.4.2 In-Elastic Processing          | 8   |

| 4.5.4.3 Data Driven Processing 6       | 9   |

| 4.6 Summary of Possible IFIS systems   | 0   |

| <b>4.7 Conclusions</b>                 | 3   |

|                                        |     |

| CHAPTER FIVE                           |     |

| IFIS IMPLEMENTATION STUDY 7            | 5   |

| <b>5.1 Objectives of Chapter</b>       | 5   |

| <b>5.2 Motivation</b>                  | 5   |

| 5.3 IFIS Design Implementation Study 7 | 6   |

| 5.3.1 FIR Filter                       | 6   |

| 5.4 IFIS FIR Filter Comparisons        | 7   |

|                                        |     |

| 5.5 Conclusions                           | 32 |

|-------------------------------------------|----|

| CHAPTER SIX                               |    |

| IFIS CELL DESIGN STUDY                    | 34 |

| 6.1 Objectives of Chapter                 | 34 |

| <b>6.2 Motivation</b>                     | 34 |

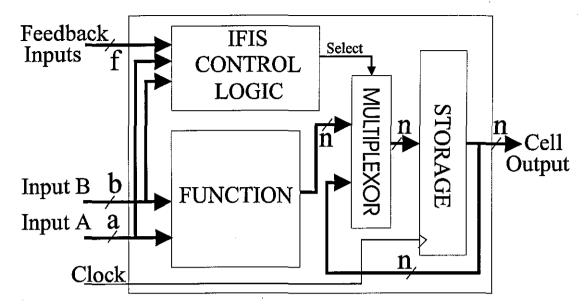

| 6.3 IFIS Cell internals                   | 35 |

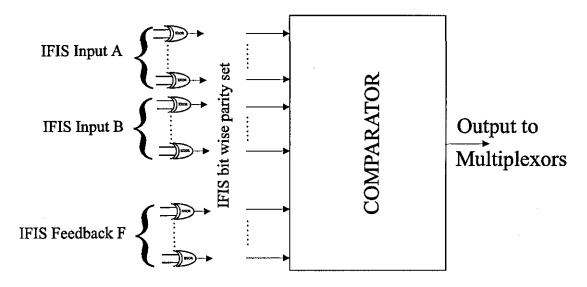

| 6.3.1 IFIS Control Block                  | 36 |

| 6.3.2 Multiplexor Block                   | 38 |

| 6.3.3 Storage Block                       | 38 |

| 6.3.4 Functional Block                    | 39 |

| 6.4 Design Solutions                      | 39 |

| 6.4.1 Behavioural Synthesis               | 90 |

| 6.4.2 Arithmetic Coding                   | 1  |

| 6.4.3 Duality                             | )3 |

| 6.4.4 Time Redundancy                     | )4 |

| 6.5 Summary of Results                    | 6  |

| 6.6 Conclusions                           | 7  |

| CHAPTER SEVEN                             |    |

| IFIS FEASIBILITY STUDY                    | 19 |

| 7.1 Objectives of Chapter 9               | 9  |

| <b>7.2 Motivation</b>                     | 9  |

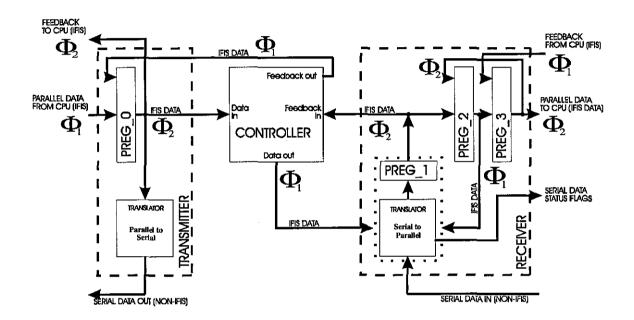

| 7.3 Design Partitioning of the IFIS UART  | 0  |

| 7.3.1 UART Controller Design              | 1  |

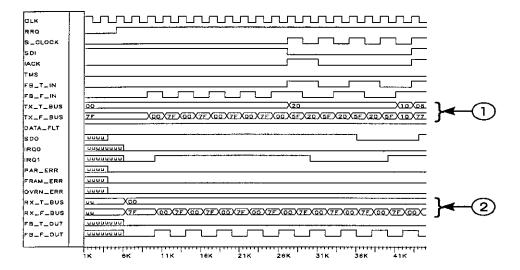

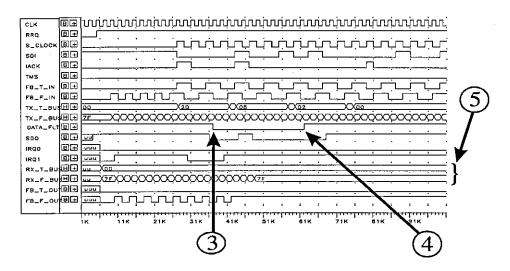

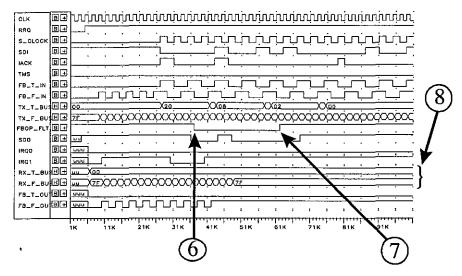

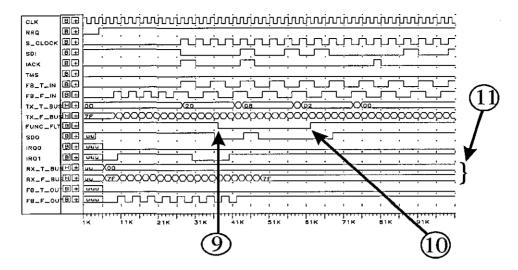

| 7.4 UART Verification 10                  | 2  |

| <b>7.5 Fault Injection</b>                | 4  |

| 7.6 The Impact of The IFIS Methodology 10 | 17 |

| 7.7 Scalability of the IFIS Methodology | 109 |

|-----------------------------------------|-----|

| 7.8 Summary of IFIS UART Case Study     | 110 |

| 7.9 Conclusions                         | 111 |

| CHAPTER EIGHT                           |     |

| CONCLUSIONS                             | 112 |

| 8.1 Objectives of Chapter               | 112 |

| 8.2 Review of Objectives                | 112 |

| 8.3 Experimental Investigations         | 113 |

| 8.4 Main Conclusions                    | 114 |

| 8.5 Measures of Success                 | 116 |

| 8.6 Limitations of the Work             | 117 |

| 8.7 Further Work                        | 118 |

| 8.8 Summary of Thesis                   | 118 |

|                                         |     |

| References                              | 119 |

| Bibliography                            | 125 |

| Published Paners                        | 126 |

#### **CHAPTER ONE**

#### INTRODUCTION

#### 1.1 Introduction

Integrated circuit technology currently enables highly complex circuit designs containing hundreds of thousands of gates to be realised. Along with the increase in gate count has come a decrease in gate cost and improvements in performance. The ability to integrate several millions of transistors into a monolithic integrated circuit (IC) offers many advantages. However, a major concern in the production of these complex devices is the ability to verify their fault free operation. The testing of digital circuits has been difficult since the beginning of the electronics industry. The problems associated with test have been aggravated by several effects arising from the increase in complexity and reduction in the pin to gate ratio. These include:

- Technological advances have enabled the prolific use of complex devices in many applications ranging from consumer products to critical commercial controllers and consequently reliability is highly important.

- The widespread deployment of ICs means reliability is an important attribute for electronic systems (Williams (1983)). Williams states that the cost of detecting a fault increases by a factor of ten from chip to board, board to system and system to 'in the field' fault.

Commercial applications are demanding higher levels of integration and higher levels of reliability. These demands need to be met with high levels of testing. Fault

coverages of greater than 99% are routinely expected during the testing of complex ASIC devices as noted in Bahram (1992).

#### 1.2 Motivation

The objectives in testing an electronic design are twofold:

- To ensure that the pre-fabrication circuit behaviour satisfies the intent of the designer and it is free from timing and functional design errors.

- To detect post-fabrication faults.

The testing of devices after fabrication is one of the most difficult problems confronting designers and test engineers as noted by Williams (1983). The problems met are:

- Test pattern generation and evaluation times are increasing with circuit complexity.

- An increase in the volume of test data needed, namely the number of input vectors and output response pairs required to test the circuit.

- The increased requirement for complex devices has driven the development of more sophisticated CAD tools. However, the greatest advances have been in layout and simulation areas and less of an improvement in the area of test until recently (Bahram (1992)).

- The number of possible faults that have to be considered is large, as complex circuits can contain substantial numbers of components (e.g. memory elements, gates and interconnect lines) which are individually subject to different kinds of faults.

- The observability and controllability of the internal elements of any circuit are limited by the number of available input/output (I/O) pins. As chip complexities increase, the task of creating an adequate test to control or observe a single circuit node becomes more difficult.

• The high speed nature of contemporary devices requires high-speed test systems that can test the circuits when they are operating at their maximum speeds.

Solving the problems above increases the number of test patterns required for a successful test. This in turn increases the time required for applying the test and the computing resources required to store the test patterns and the results. Moreover, Williams (1983) shows that it has now become impracticable to attempt fully exhaustive testing of complex circuits. As a result, several alternative test methods have been suggested to alleviate the problem. The testing solutions for electronic systems fall broadly into two categories, off-line and on-line testing.

#### 1.2.1 Off-Line Testing

Off line testing, or explicit testing, separates the testing process from the normal operation process. In general, off line testing involves three steps:

- Generation of the test patterns

- Application of the test patterns,

- Evaluation of the responses obtained from the device under test

The goal of the test pattern generation phase is to produce those input patterns which will exercise the Device Under Test (DUT) in different modes of operation while trying to detect any existing faults. The production of the test patterns is a difficult task as each fault considered must be excited and then propagated to a primary output. A wide range of algorithms have been proposed to automate the test pattern production stage at both gate and transistor level, while targeting many different fault types (e.g. Aitken (1991), Bleeker (1993), Corno (1996), Goel (1981), Fujiwara (1983), Reddy (1985), Schulz (1989), Larrabee (1989), Nigh (1990), McEuen (1996) and Ferguson (1991)). It has been shown (e.g. Williams (1983) and Seth (1985)) that

computer run time to perform test generation is approximately proportional to the cube of the number of gates within the design. As circuit complexity increases, this overhead becomes more intractable, making test pattern generation increasingly complex.

The application of test patterns can be accomplished in two ways, either via external testing or through the use of Built In Self Test (BIST) structures within the design. With external testing, Automatic Test Equipment (ATE) is used to apply the test patterns externally. This gives good control over the test process and allows testing under different timing and electrical conditions.

With BIST techniques, the DUT is forced to execute a self test procedure. This is less expensive in terms of required test equipment, but requires greater design effort to incorporate the BIST structures into the design. There are numerous techniques for designing BIST structures put forward by Asaad (1996), Konemann (1979), Beucler (1984), McCluskey (1985), Avra (1993), Kothari (1993), Fertsch (1991) and Zorian (1993). These techniques have been categorised under the Design For Test (DFT) heading and aim to aid the testing of circuits using a structured design manner. These DFT methods have a variety of performance and complexity overheads associated with each implementation, and will not be discussed within the framework of this thesis. For further information see Golstein (1979), Haider (1993), Hellerbrand (1996), Abadir (1983) and Muehldorf (1981).

The process of evaluating the responses from the device under test usually aims to achieve two goals. Firstly, to distinguish between the good and faulty devices, and secondly, to provide fault location information for diagnostic purposes. There are several techniques available to aid in the evaluation of the response vectors from the device under test. All of these use some form of comparison between a known good, or 'Golden Signature' response, and the actual response from the device under test. This leads to a go/no-go decision as to the reliability of the device.

Generally, off-line testing has the following advantages:

- The test vectors, once generated, can be applied at speed to the DUT. This

allows full testing of the DUT's electrical and timing responses.

- The fault coverage of the vector set can be determined with a high degree of accuracy and test vectors generated until the desired level of fault coverage is achieved.

However, there are also several disadvantages with off-line testing, namely

- Test pattern generation requires considerable amounts of computing resource to generate vectors and to store the stimulus vector set.

- Exhaustive testing is impractical.

- Fault simulations are required to determine the level of fault coverage a

particular vector set achieves. This also requires considerable amounts of

computing resource.

- Faults occurring after production tests cannot be detected (e.g. transient faults, stress faults, wear out faults).

These problems are going to become increasingly apparent as circuit complexity grows and device dimensions shrink.

#### 1.2.2 On-Line Testing

On-line testing, or implicit testing, integrates the testing process with the normal operation of the device. Any device designed using on-line test concurrently tests itself during normal operation. This generally requires the introduction of redundancy into the circuit design. This redundancy usually takes the form of either information redundancy, time redundancy or hardware redundancy. In practice, one type of redundancy (which is predominant) usually involves introducing some other type as well. As an example, consider information redundancies such as encoding of data with

an error detecting code (EDC). This relies on introducing extra bits to any data unit, e.g. by encoding inputs and outputs of all circuits (and internal states if the circuit is sequential) with EDCs. However, it also involves hardware redundancy such as encoders, decoders, extra data path lines (to transmit) or extra memory elements (to store) these extra bits. Time redundancy is also introduced as the encoding / decoding of data may introduce some delay into the system. Although the introduction of extra redundancy is required, the benefits when compared to explicit testing can be attractive:

- Explicit testing expenses (e.g. for test equipment, down time, and test

pattern generation) are eliminated during the life of the system as the data

patterns used in normal operation serve as test patterns.

- The faults are detected instantaneously during the use of the chip, hence the first faulty data pattern caused by a certain fault is detected. The user can then rely on the output results within the degree of fault coverage provided by the error detection method used. In explicit approaches, nothing can be said about the correctness of the result until the chip is fully tested.

- Transient faults, which may occur during normal operation, are detected if they cause a faulty data pattern. These faults cannot be detected by any explicit testing method.

Unfortunately, the on-line testing approach also suffers from several drawbacks that limit its usage in testing:

- The data patterns (application patterns) may not exercise all the storage elements or all the internal connection lines within the chip. Defects may exist in places not exercised, and hence the faults produced will not be detected.

- Using information redundancy to code the information used in an IC often requires additional I/O pins. At least two extra pins are needed as error signal indicators (A single pin cannot be used, since a single pin stuck at the

good value could go undetected). Because of the constraint on pin count, however, such requirements cannot easily be fulfilled.

- Additional hardware circuitry is required to implement checkers, storage units and to transmit any coded information.

- Designing a circuit for on-line testing is often a more complex task than designing a similar circuit that is tested explicitly.

- On-Line test approaches provide no control over critical voltage or timing parameters. Hence, devices cannot be tested under marginal timing and electrical conditions.

- The degree of fault coverage usually provided by implicit methods is less than that provided by explicit methods.

The on-line and off-line methods of testing digital electronic circuits both have a common aim - to distinguish between good and faulty devices in the most cost effective manner. In Williams (1983), it is shown that the greatest commercial cost occurs if a device fails in the field, which is **after** passing its production test. It has also been shown by Sieviorek (1992) and Jha (1993) that transient faults are by far the most common types of faults occurring during the operation of contemporary electronic systems and it is these types of faults that off-line testing is unable to detect. Consequently, although off-line testing is considered to be the more comprehensive test since the fault coverage is generally higher, only on-line testing can offer any form of protection against the more expensive 'in-the-field' component failures a company may face. In addition to this, many designs which incorporate on-line test strategies also undergo an off-line test immediately after fabrication. Consequently, on-line test is an exciting area of research that is currently exhibiting rapid growth.

#### 1.3 Aims of the Thesis

This thesis focuses on a novel approach to on-line testing under development at Loughborough University. The approach, IFIS (If it Fails, It Stops), is a test methodology that uses dual-rail encoding of data and handshaking between

computation elements to achieve on-line test. This thesis attempts to evaluate the IFIS on-line test methodology and offer evidence as to its suitability for IC design. The evaluation of the IFIS methodology is achieved by employing two aims, namely

- An identification and assessment of the encoding schemes, fundamental building blocks and design methodologies for IFIS.

- An evaluation of the utility of the IFIS concept issues through the construction of a 'realistic' demonstrator IC.

#### 1.4 Structure of the Thesis

A review of related work is provided in **Chapter Two**. Firstly, the current state of online testing is examined within the context of information, time and hardware redundancy. The review shows how the various on-line test techniques are related and compares the overheads associated with each method. Comparisons of the various online test methods help to identify areas of interest; in particular it focuses on IFIS.

Chapter Three introduces the objectives of the experiments, used to fulfil the aims of the thesis. It outlines four experiments to satisfy the objectives and explains the experimental assumptions used in these investigations.

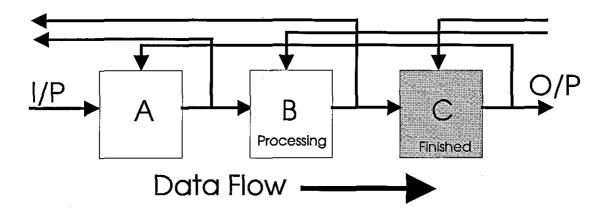

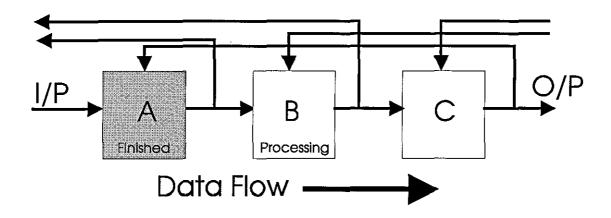

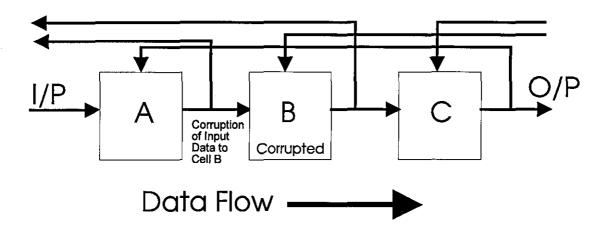

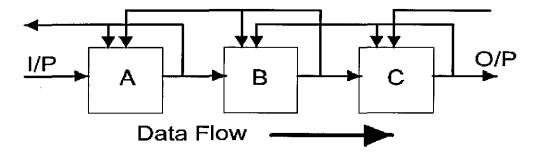

Chapter Four discusses the first experiment which provides an in-depth investigation into the IFIS methodology with the goal of identifying the required characteristics for processing data. This involves a study into encoding schemes, processing rules and of feedback structures within an IFIS system. The outcome of the experiment identifies effective encoding schemes and feedback structures for use within the IFIS methodology.

Chapter Five details the implementation impact of the IFIS methodology when targeted to ASIC and FPGA technologies. The different encoding schemes and

feedback systems undergo hardware implementation to identify and assess the more cost-effective combinations.

Chapter Six details a design study focused on producing a less complex cell design for the IFIS methodology. Several possible design solutions undergo hardware evaluation to identify the most generic and cost-effective cell design for IFIS cells.

Chapter Seven focuses on implementing the new methodology into a 'real life' design as a feasibility study. A commercial UART (Universal Asynchronous Receiver Transmitter) is re-engineered using the IFIS methodology. Comparisons are then drawn between the IFIS and conventional UARTs to highlight the impact of the methodology on 'real life' designs.

Chapter Eight draws together the conclusions from each of the four investigations and discusses whether the stated objectives have been achieved. It examines the limitations of the work and outlines possible extensions to the existing investigations, as well as further research areas that may be of interest for extended study. Finally it summarises the main points of the thesis.

### CHAPTER TWO REVIEW

#### 2.1 Objectives of Review

The main objectives of this chapter are three fold:

- To review the current state-of-the-art in on-line testing,

- To identify interesting topics which could be investigated further,

- To specify the area in which the work in this thesis will address, given the available time and resources.

With these objectives met, the experiments performed within this thesis should be in context.

#### 2.2 Motivation

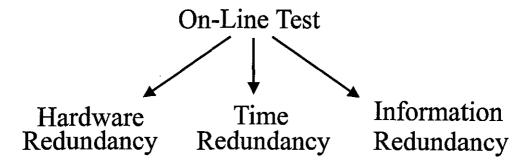

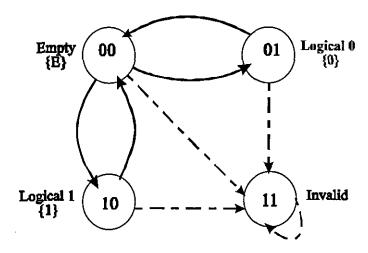

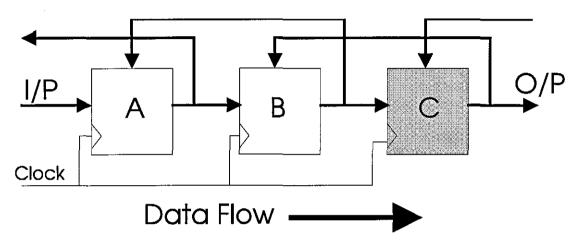

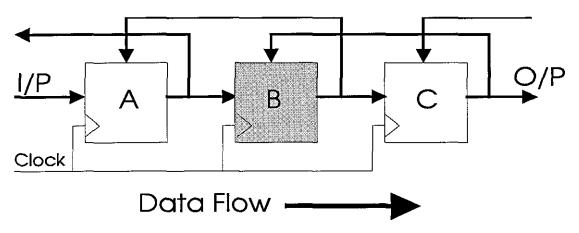

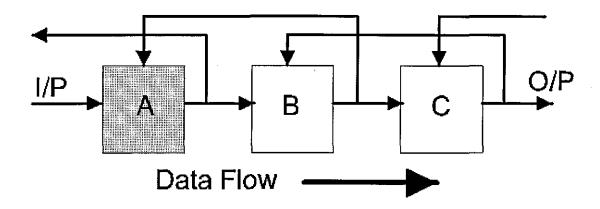

This work is necessary to help identify areas that have not been fully explored and to help clarify the direction taken by the field in general. The field of on-line test can be broken into three categories as shown in Figure 2.1:

Figure 2.1 - Redundancy Methods within On-Line Test

- Hardware Redundancy: This technique is one of the simplest, requiring

multiple copies of the design to be placed in parallel. The circuit outputs are

compared after each computation and if no errors have occurred, the results

will be identical. In the presence of a fault, the faulty design will yield an

output inconsistent with the other copies. These methods are discussed in

section 2.3.

- Time Redundancy: This technique involves the re-use of a single hardware design at successive points in time. The data is applied, the computation is performed, and the output response is stored for comparison with another calculation using the same data. If no errors have occurred, the results will be identical. However, if a fault has occurred then the results will be inconsistent. Several methods have been presented in the literature to prevent a fault from affecting both computations in the same manner, thus yielding a corrupted but undetected output response. These are discussed in section 2.4.

- Information Redundancy: The final technique uses redundancy within the transmitted data to determine if a fault is present. The information is encoded before operation, and decoded after operation. Any fault affecting the operational data alters the expected codeword and is detected. A variety of coding schemes exist which offer different degrees of protection against faults. These schemes are discussed in section 2.5.

Each redundancy technique brings benefits and penalties which make it suit a particular implementation. This review discusses the advantages and disadvantages of

each technique, and highlights areas where further work could be undertaken. This allows the direction of the work within this thesis to be identified. The three categories of hardware, time and information redundancy described above will now be reviewed further.

#### 2.3 Hardware Redundancy

Several forms of Hardware Redundancy exist which are all based on an idea originally proposed by von Neumann in 1956. The idea was to replicate the original circuit such that a single fault would affect only one copy of the circuit in question. The remaining correctly operating circuits would thus mask the fault and still produce a correct output. Although this basic technique is simple and easy to achieve, it is also limited by the addition of potentially large amounts of redundant hardware. Unfortunately, along with the increase in complexity comes an increase in power consumption and a substantial increase in the physical size occupied by the extra hardware. These factors can make the use of hardware redundancy very difficult to justify. Several variations of von Neumann's proposal have been implemented, with varying degrees of success.

#### 2.3.1 Duplication With Comparison

One form of hardware redundancy is that of duplication with comparison. This is the simplest form of von Neumann's idea and requires the duplication of the circuit as described in Johnson (1988). The outputs of the two circuits are fed into a comparator which determines if a fault has occurred. Duplication with comparison involves a simple and straightforward design style that is effective in detecting all single stuck-at faults which result in an error. Unfortunately, duplication with comparison requires careful design of the comparator to ensure that any faults within the comparator do not cause an incorrect output response or mask a fault within the duplicated units (i.e. the comparator must be self-checking). Another disadvantage is the increase in physical size and power consumption of the design. Although the increased circuit complexity

could possibly be tolerated, the increased power consumption and weight of this technique are considerable disadvantages.

#### 2.3.2 Triple Modular Redundancy

Another simple form of hardware redundancy is that of Triple Modular Redundancy (TMR) as described in Russell (1989) and Audet (1996). The logic circuits are triplicated and fed into a majority voting element which usually calculates the majority function M = XY + XZ + YZ. The logic circuits are not restricted in terms of complexity, and can be any design from a simple gate to a microprocessor or larger. The majority function ensures that if one circuit is faulty, the other two circuits will override the error and mask the fault. However, there are two main problems with this type of on-line error detection scheme. Firstly, two circuits failing in the same manner will produce an incorrect output response. Secondly, the majority voting element is a single point of failure. Consequently, although the voting element is usually much simpler than the circuits being triplicated, its design is of the utmost importance. The voting element must be the most reliable unit, as a single fault in the voter can still produce an incorrect output response. In an attempt to overcome this problem, the N-Modular Redundancy technique was proposed.

#### 2.3.3 N-Modular Redundancy

A method for fault tolerance has also been described in Russell (1989) where the technique of TMR was expanded to that of N-Modular Redundancy (NMR). The main difference between NMR and TMR is that the function circuit and the voting elements are both duplicated N times. This gives greater tolerance to faults as (N+1)/2 circuits would need to fail in exactly the same way for an incorrect output response to be generated. Statistically, the probability of the (N+1)/2 circuits all developing the same fault at the same time is considerably small. The single point of failure in TMR, the

voting element, is also duplicated N times. This eliminates the possibility of a single fault in the voting circuit causing an incorrect output response to be generated. A reliability analysis of systems using both TMR and NMR is given in Russell (1989).

#### 2.3.4 Summary of Hardware Redundant Techniques

The main penalties paid when using the hardware redundant techniques are the overheads created during implementation. Duplication requires at least twice the overhead (two circuits and a comparator), TMR requires at least three times the overhead (three circuits plus the voting element), while NMR requires more than N times (N circuits plus the N voting elements). In addition to this, duplication with comparison and triple modular redundancy both have single points of failure (i.e. the comparator or voting element) which requires careful design to ensure the hardware redundancy is not rendered in-effective by a fault within the comparator. These points are highlighted in Table 2.1. The points shown in Table 2.1 are significant disadvantages as some of the implementation characteristics are highly undesirable. For many applications which use ASIC technologies, the increase in complexity and power cannot be justified and consequently a more efficient means for implementing on-line test needs to be found.

| Redundancy<br>Method            | Area<br>Overhead | Power Consumption | I/O<br>Pins | System<br>Size | Single Point of Failure? |

|---------------------------------|------------------|-------------------|-------------|----------------|--------------------------|

| Duplication with Comparison     | > x 2            | > x 2             | > x 2       | > x 2          | Yes,<br>Comparator.      |

| Triple<br>Modular<br>Redundancy | > x 3            | > x 3             | > x 3       | > x 3          | Yes, Voting Element.     |

| N-Modular<br>Redundancy         | > x N            | > x N             | > x N       | > x N          | No.                      |

Table 2.1 - Hardware Redundancy Summary

#### 2.4 Time Redundancy

The hardware redundant methods for on-line testing require an increase of at least 100% (duplication with comparison), 200% (triple modular redundancy) or greater (n-modular redundancy) in terms of area, power consumption, weight, size and overall system cost. In an attempt to overcome some of the difficulties with hardware redundancy, time redundancy has been proposed and has received much attention (e.g. Reynolds (1978), Patel (1982) and Hana (1986)). Using redundancy in time also leads to the advantage that on-line checking of the circuit operation is achieved without increasing the number of I/O pins. In complex designs, where constraints on I/O pin counts can be of great importance, time redundancy could thus be an attractive approach. The main areas involving time redundancy that have received recent attention will now be explored.

#### 2.4.1 Alternating Logic

A design technique which uses time redundancy has been proposed by Reynolds (1978) where the successive execution of a required function and its dual is used to determine the validity of the output response. This technique requires all circuits designed in this manner to exhibit the 'self-dual' property. The 'self-dual' property is difficult to achieve as it requires a circuit to have the following property:

If a combinational circuit implements the Boolean function  $Y = F(X_1, X_2, X_3)$ , then the function  $F(X_1, X_2, X_3)$  is self-dual if inverting all of the inputs yields an inverted output, such that  $\overline{Y} = F(\overline{X}_1, \overline{X}_2, \overline{X}_3)$ .

Evidently any arbitrary function is not self-dual and cannot be immediately implemented using this design style. However, according to Reynolds (1978), it is possible to convert any non-self-dual function of n variables into a function of n+1 variables that is self-dual. The converted circuit can then be implemented using this technique. The self-dual method is also adaptable to sequential circuitry, but does require the addition of memory elements within the design. Unfortunately, transforming an arbitrary function into a self-dual equivalent usually incurs a substantial increase in the amount of circuitry required for the implementation. Johnson (1988) notes that the alternating logic technique may require an increase of 85%-100% in hardware to make a function self-dual. This technique is then comparable to duplication with comparison.

#### 2.4.2 Recomputation With Shifted Operands

Another method of concurrent error detection called Recomputing with Shifted Operands (RSO) was proposed by Patel (1982). This technique applies an input data word to an arithmetic unit and calculates the result. The result is then shifted N bit positions and stored. The inputs are shifted M bit positions and re-applied to the same unit (e.g. for addition M=N, and for multiplication,  $M^2=N$ ). Under fault free

conditions the two results will be identical, as the shift is present only to force different data paths through the arithmetic unit. This ensures a single fault will not affect both calculations in the same manner and does not affect the arithmetic operation performed by the unit. The complexity increase caused by the implementation of the RSO technique depends upon the original circuit, but has been shown by Hana (1986) to be 31.4% for an ALU. A similar technique of recomputing with rotated operands (RRO) has also been proposed by Patel (1982) and separately by Li (1992). With this technique, the operands are applied, barrel shifted and then reapplied in an attempt to detect errors. Similarly, this approach uses barrel shifting in an attempt to force different data paths through the design, and does not affect the arithmetic operation taking place. The complexity increase for this technique is similar to the RSO overhead, as RRO is a special case of RSO as noted by Patel (1982). As both the RSO and RRO techniques effectively apply different vectors to the functional circuit during the second computation, the corresponding fault coverage is considerably higher than the hardware redundancy techniques of duplication with comparison and TMR as noted in Johnson (1988). Unfortunately, both approaches only work for certain arithmetic functions (e.g. addition and multiplication) and cannot be applied to arbitrary logic functions. Although these methods do allow the detection of single faults within the arithmetic unit, the inability to implement the technique to functions other than simple arithmetic is a major disadvantage.

#### 2.4.3 Recomputation With Swapped Operands

Recomputation with swapped operands (RSWO) is a variation of the recomputation with shifted operands (RSO) as shown in Hana (1986). The encoding and decoding function is that of swapping the upper and lower halves of each operand. At time  $t_0$ , the computation is performed using the unmodified operands and the result is stored for later comparison. At time  $t_0+\delta t$ , the upper and lower halves of each operand are swapped and the computation repeated. This method has the advantage of being simple to implement, while only requiring a complexity increase of 23.8% for the same ALU implementation discussed for RSO (Hana (1986)). The advantages of this

approach are that the hardware overhead required to implement the required swapping is 5%-10% less than that required by the shifting operand technique. However, the disadvantages of this technique are that the comparison stage still requires careful design such that the extra redundancy is not rendered in-effective by a fault within the comparator itself. Consequently, the comparator must again be self checking.

#### 2.4.4 Summary of Time Redundant Techniques

The technique of time redundancy immediately brings a reduction in data throughput, as 50% of the calculations are used solely for the purpose of error detection. The time redundant methods discussed also come with some form of hardware redundancy, either in the form of extra registers required to hold a result before comparison, the comparison hardware, or the extra bits since the data word width is increased (e.g. due to shifting the operands in RSO). Although this extra hardware is usually smaller than the various overheads of hardware redundancy, it can still be significant with Alternating Logic requiring up to 85% as stated by Johnson (1988). As with hardware redundancy, careful design of the comparison hardware must be undertaken so that a fault within the comparator does not render the time redundancy in-effective. These points are highlighted in Table 2.2. From Table 2.2, it can be see that although time redundancy does have some advantages when compared to hardware redundancy, such as decreased hardware overhead and lower I/O pin counts, it also has some disadvantages which need to be considered. These disadvantages include a still significant hardware overhead and reduced data throughput. In many ASIC designs, where operational speed is crucial, the reduced data throughput incurred by time redundancy could severely limit the performance of the system.

| Redundancy<br>Method                | Data Throughput | Hardware<br>Overhead | Increase<br>in I/O<br>Pins ? | Single Point of Failure? |

|-------------------------------------|-----------------|----------------------|------------------------------|--------------------------|

| Alternating Logic                   | 50%             | 85-100%              | Negligible                   | Comparator               |

| Recomputing with Shifted Operands   | 50%             | ≈31.4%               | Negligible                   | Comparator               |

| Recomputation with Rotated Operands | 50%             | ≈40%                 | Negligible                   | Comparator               |

| Recomputing with Swapped Operands   | 50%             | ≈23.8%               | Negligible                   | Comparator               |

Table 2.2 - Time Redundancy Summary

#### 2.5 Information Redundancy

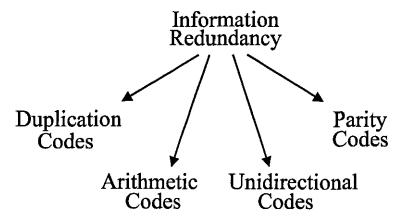

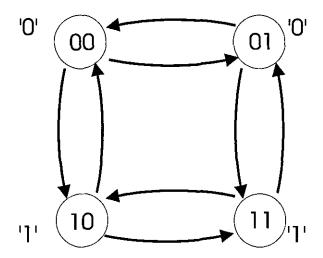

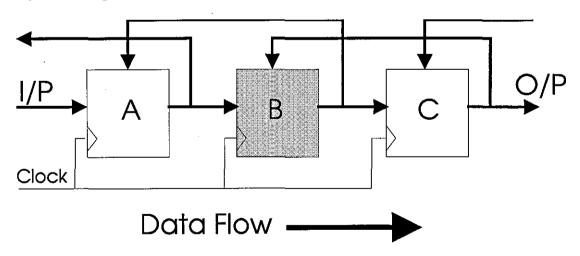

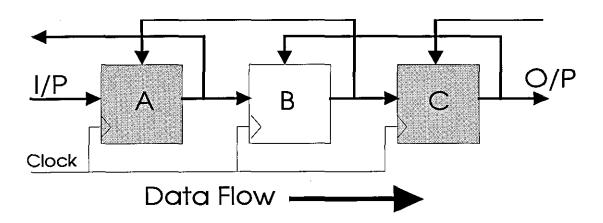

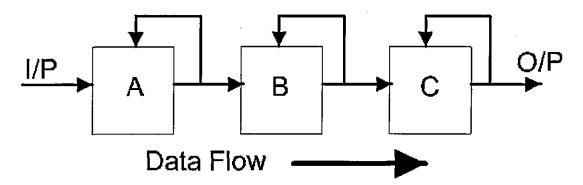

Both of the redundancy techniques previously discussed can incur substantial penalties in terms of hardware, I/O pins and power consumption. This can make them less attractive to ASIC implementation. The third technique in the on-line testing environment is information redundancy. Information redundancy is the process whereby the data to be manipulated is coded such that any faults within the system alter the expected code and are detected. Data coding introduces redundancy into the data stream which usually manifests itself in terms of extra bits in the data word being manipulated. These extra bits provide the means for the receiver to determine if an error has occurred and take the appropriate action. There are various techniques within the on-line test environment which use data coding, and these can be broken into four coding groups as shown in Figure 2.2.

Figure 2.2 - Information Redundant Code Categories

- Duplication Codes: This coding technique duplicates the entire word to be transmitted, with bit by bit inversion in the duplicated word.

- Arithmetic Codes: These coding techniques are designed specifically for arithmetic operations. Here the coding function is retained or modified in a known manner through the arithmetic operation. Some of these codes can be used for logical operations as well.

- Unidirectional Error Detecting Codes: These codes are designed specifically to offer protection against faults which manifest themselves as single, multiple or burst bit errors in the '0' → '1' direction, or the '1' → '0' direction, but not both simultaneously.

- Parity Based Codes: These codes are based purely on the generation and checking of parity bits.

Unfortunately, selection of only one error detection code that would be best suited for a particular digital system is infeasible. It is well known that the error codes suitable to protect bus data or the memory system are not preserved by the arithmetic circuitry. Conversely, error codes suitable to protect arithmetic circuitry may be too expensive to be used for data bus protection and not powerful enough to be used in memory systems (which generally require the use of an error correcting code). Consequently, all four classes of error detecting codes are required depending upon the application and consequently will now be reviewed in more detail.

#### 2.5.1 Duplication Codes

Duplication codes are the most redundant error detecting codes available with 100% redundancy, but also have the advantage that totally self checking circuits (see section 2.5.6) are generally simple to construct. Methods for translating duplication codes directly into TSC circuits are readily available in Ashjaee (1977), Nikolos (1996) and Piestrak (1995).

#### 2.5.1.1 Alternate Data Retry

One information redundancy technique that uses duplication coding is that of alternate data retry as described in Shedletsky (1978). The alternate data retry method is a reexecution of an operation which initially fails to produce an error-free result. The alternate data retry method uses an alternative data representation in an attempt to nullify the effects of any faults. The choice of alternate data representation and the design of the processing circuits combine to ensure that even an error due to a permanent fault is not repeated during retry. This is best illustrated with the example from Shedletsky (1978), where unit A sends an odd-parity vector <0001> over the bus to unit B. Due to the presence of a stuck-at fault, unit B receives the erroneous, evenparity vector <1001> and signals an error. For the retry, unit A sends the alternate data representation <1110>, which is received correctly despite the fault. In this example, both the vectors <0001> and <1110> represent the same message and convey the same information between units. This system of recomputing a result if an error condition occurs involves information redundancy as each data representation within the design must be duplicated to allow both the vector <1110> and the vector <0001> to convey the same information. This forces any implementation to be only 50% efficient in terms of transmitted information. Unfortunately, Shedletsky (1978) does not provide hardware implementation data.

#### 2.5.1.2 Summary of Duplication Codes

Duplication codes are used in areas where the information redundancy is not of great concern and the design time is necessarily short. The main disadvantage with duplication codes is the immediate information redundancy of 100%. However, the advantages with this type of encoding scheme are the ease in which totally self checking (TSC) circuits can be implemented and the conceptually simple nature of the encoding.

#### 2.5.2 Arithmetic Codes

Error correcting codes for arithmetic operations have received considerable attention and can be classified into non-separate and separate codes. Both classes of codes possess many similar properties, but differ significantly in their implementation. The non-separate code considered is the AN code as described by Brown (1960), which is formed when an uncoded operand (N) is multiplied by the check modulus (A) to give a coded operand AN. With this type of coding, the coded word cannot be separated into original data and check bits as the check is integral to the data undergoing the operation. Alternatively, the separate codes considered are the residue code, and the inverse residue code as described by Brown (1960), Garner (1966), Russell (1989), Siewiorek (1992) and Avizienis (1971). These codes are separate since the check bits are generated and appended to the original data to form the transmitted word. In this manner, the data transmitted is of the form IC (where I is the original information word and C is the appended check) and the check bits are easily determined.

#### 2.5.2.1 Non-Separable Arithmetic Codes

The AN codes described by Brown (1960) are a coded form of the operands such that two numbers X and Y are coded as AX+B and AY+B. These codes are useful since

the two coded operands can undergo arithmetic operations and the result will differ from the coded output by a constant. Consequently, the coding is preserved by the arithmetic operation. In the case of addition for example, the two coded input operands could be:

$$AX+B + AY+B = A(X+Y)+2B$$

The coded result thus differs by a constant B from the AN coded output of A(X+Y)+B. Similar results can also be shown for other arithmetic operations. However, certain requirements must be satisfied by the AN code. Firstly, the minimum Hamming distance between messages must be two for error detection and three for error correction. Secondly the complement of a coded operand must be obtainable by complementing each binary symbol in the coded message. This necessary for subtraction as noted by Brown (1960). However, some logical operations cannot be checked by arithmetic codes and as such are unsuitable for this type of coding. In this case, the operations must be performed on uncoded operands with no error protection as noted in Siewiorek (1992).

# 2.5.2.2 Separable Arithmetic Codes

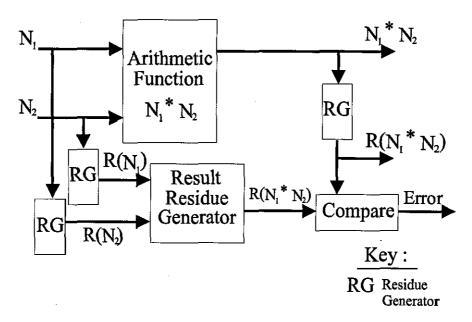

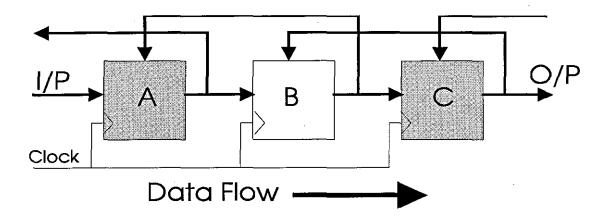

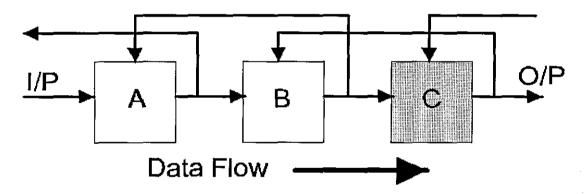

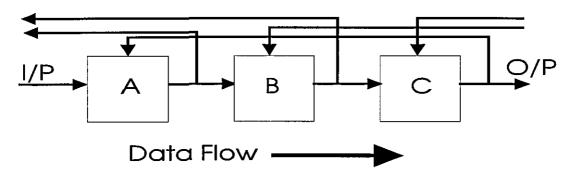

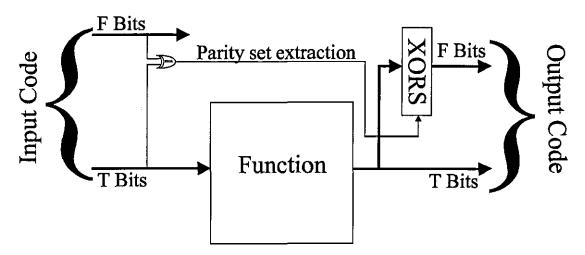

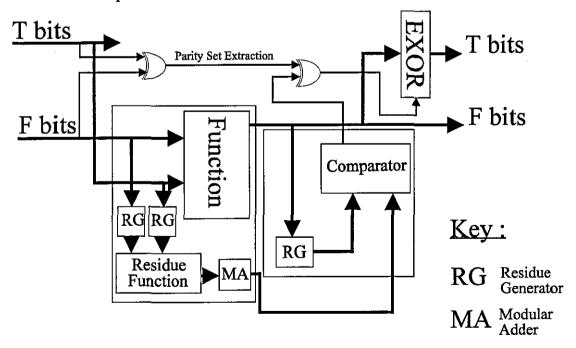

The separable arithmetic codes considered are the residue and inverse residue codes as described by Brown (1960), Garner (1966), Russell (1989), Siewiorek (1992) and Avizienis (1971). In the residue-m code, the residue of a data word N is defined as  $R(N) = N \mod m$ , with the codeword formed by concatenating N and R(N) to produce NR(N). The result after operation can be checked by comparing the residue of the result with the residue of the inputs undergoing the same operation as shown in Figure 2.3.

Figure 2.3 - Residue Coding for Arithmetic Functions

If the residues after operation are equal, no error has occurred. One variation of the residue-m code is the inverse residue-m code, where the check quantity, Q, is formed by  $Q = m - (N \mod m)$ . The inverse residue code has greater tolerance of repeated-use faults as shown in Avizienis (1971), where a sequence of operations could be performed on faulty hardware before any checking is performed (e.g. iterative circuits such as multipliers and dividers). Unfortunately, the use of residue and inverse residue codes are greatly affected by three factors:

- Generally the complexity of the checking hardware increases sharply as the base (m) increases.

- As the base increases, more bits are needed to represent the residue.

- The error detection ability of the residue increases only slowly as the base increases.

This indicates that the choice of base must be kept as low as possible to ensure a low hardware complexity and the fewest check bits. Russell (1989) states that logical operations can also be coded using residue coding, with only a slight alteration to the basic method. However, Russell (1989) also shows that although the residue code can

be used for coding logical operations, the hardware increase can be up to 35 times greater than for pure arithmetic functions depending upon the function.

### 2.5.2.3 Summary of Arithmetic Codes

In both the AN and residue codes, the error detection operations can be complex, except when the check base equals 2<sup>a</sup> - 1 (where a is the number of check bits). Thus for binary implementations with check base equal to 3, the number of check bits (a) must be 2 to achieve a low cost solution. Implementations that use the 3N (for AN coding), and mod 3 (for residue coding) schemes are termed low cost arithmetic codes as the hardware implementation requirement is minimal as stated in Avizienis (1971). Both the AN code and residue code can protect data as it is operated upon by arithmetic functions, but only the residue code can offer protection when logical functions are used. Consequently, the residue coding scheme seems to offer greater flexibility, especially when the designs contain a large proportion of arithmetic circuitry.

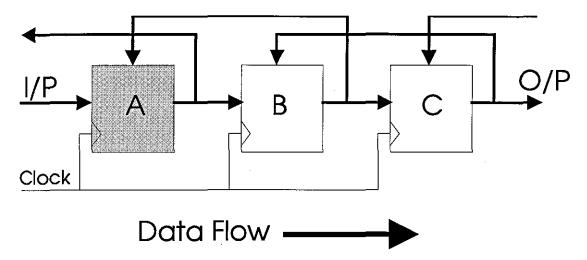

# 2.5.3 Unidirectional Error Detecting Codes

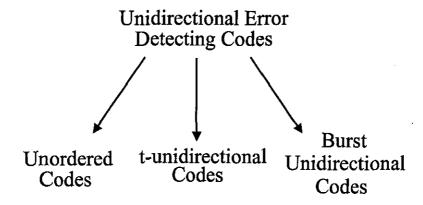

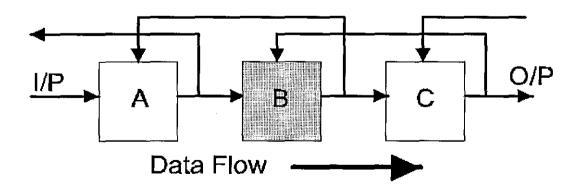

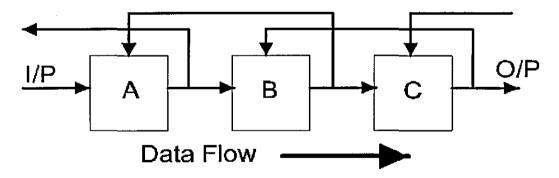

Unidirectional errors are considered to be one of the most common forms of semiconductor failure as noted in Ashjaee (1977). Consequently, unidirectional error detecting codes have received much attention (e.g. Ashjaee (1977), Burns (1992), Freiman (1962), Berger (1961), Smith (1984), Piestrak (1995), Borden (1982), Dong (1984), Bose (1985) and Blaum (1988)). A unidirectional error is a single or multiple error such that all erroneous bits are either of the '0'  $\rightarrow$  '1' or '1'  $\rightarrow$  '0' error type within a data word, but not both at the same time. These are also known as asymmetric channel transmission errors. Three types of unidirectional error codes are commonly investigated, these being the unordered codes, the t-bit unidirectional error detecting codes and the burst unidirectional error detecting codes as shown in Figure 2.4.

Figure 2.4 - Unidirectional Error Detecting Code Categories

These various coding schemes form the basis of the current work within the field of unidirectional error detection and will be reviewed in more detail.

#### 2.5.3.1 Unordered Codes

Unordered codes are a set of codes that can detect all unidirectional errors in a data word as described in Piestrak (1995). The term unordered is defined by the following conditions:

X covers Y if and only if X contains a '1' everywhere Y contains a '1'. If neither X covers Y nor Y covers X, then the binary codewords X and Y are unordered.

Consequently, a binary code C is an unordered code if for every  $\{X,Y\} \in C$ , X does not cover Y, and Y does not cover X. For example, the words 1010, 1101 and 0011 form an unordered set, and are capable of detecting unidirectional errors.

## 2.5.3.1.1 Non-Separable Unordered Codes

The unordered unidirectional error detecting code considered is the m-out-of-n code. The m-out-of-n code (also known as the m/n or constant weight code) is the set of codewords which contain exactly m '1's and (n-m) '0's. This code is non-separable as the original word is not directly identifiable from the codeword and must undergo decoding to obtain the original message. Freiman (1962) and Piestrak (1995) have both offered proofs stating that the m-out-of-n code is optimal when m = n/2, as this allows the maximum number of codewords for any code of length n. According to Piestrak (1996) totally self checking circuits can be easily achieved for both combinational and sequential circuits provided that the circuitry is realised inverter free. Also, the detection of a valid codeword within the m-out-of-n set only requires a counter to determine its weight (i.e. the number of '1's in the codeword). This is relatively simple to achieve, but does mean that the counter and the logic function that operate upon the m-out-of-n code are both of crucial importance when designing circuitry. Unfortunately, as the code is non-separable, decoding must take place to obtain the original message.

# 2.5.3.1.2 Separable Unordered Codes

The separable unordered code considered is the Berger code as originally proposed by Berger (1961) and reviewed again by Ashjaee (1976), Smith (1984) and Burns (1992). The Berger code is separable as the check bits are appended after the original information bits. The check bits are calculated by counting the number of '0's within the information word (I<sub>0</sub>) and appending the binary count after the information bits. The Berger code has the property that if all 2<sup>n</sup> information codewords are used, it requires the minimum number of check bits to form an unordered code. In this case, the Berger code is *optimal* as defined by Smith (1984). The decoding and checking of information coded as a Berger code by a totally self checking checker has been explored by Burns (1992), Chang (1996), Metra (1996), Ashjaee (1976) and again in

much detail by Piestrak (1995). Currently, the Berger code is most commonly used in applications where a separable code is needed as noted in Burns (1992). There are many totally self checking checker designs for the Berger code that have been explored and are well known (e.g. Burns (1992), Piestrak (1995) and Ashjaee (1976))

# 2.5.3.2 t-Unidirectional Error Detecting Codes

The data stored within digital systems are usually organised and operated upon in words. Therefore, provided only single hardware failures occur, instead of any number of unidirectional errors occurring as previously described, it is more likely that up to t-unidirectional errors will occur (where t is the word length). Piestrak (1995) describes a t-unidirectional EDC (t-UEDC) as a codeword where no set of t unidirectional errors can transform one codeword into another codeword. The area of t-unidirectional error codes has been the subject of much investigation (e.g. Borden (1982), Dong (1984) and Bose (1985)). As previously, the various codes for detecting t-unidirectional errors can be split into non-separable and separable codes where the check bits are either integral to the transmitted word (non-separable), or directly identifiable (separable).

# 2.5.3.2.1 Non-Separable t-Unidirectional Error Detecting Codes

The non-separable codes are the Borden codes as originally developed by Borden (1982). These are similar to the m-out-of-n codes discussed previously. The Borden codes are created by using an m-out-of-n code where the weight of n (i.e. the number of '1's or m) is given by:

$$m = \lfloor n/2 \rfloor \mod(t+1)$$

where n is the length of the codeword and t is the number of unidirectional errors. This code was shown to be optimal in Borden (1982), and stated again in Bose (1985). It should be noted that if t = 1, the Borden code becomes identical to the parity code which is separable. This is a unique case of the Borden code as all other versions are non-separable. Self checking checkers for Borden codes have recently been proposed in Piestrak (1995) and have been built using a number of self checking checkers for m-out-of-n codes cascaded. The self checking checkers for Borden codes discussed in Piestrak (1995) are complex and contain a highly irregular internal structure that consequently makes them difficult to design and thus less suitable for complex systems.

### 2.5.3.2.2 Separable t-Unidirectional Error Detecting Codes

The separable codes capable of detecting t-unidirectional errors are the Bose codes and Dong codes. The separable t-unidirectional error detecting codes were first introduced by Dong (1984) and optimised by Bose (1985). Both codes are similar in that the check bits are appended after the information word, thus forming a separable code. Dong codes are constructed by assuming that any occurring fault can also affect the check bits generated to protect the original information bits. As the check bits themselves are not protected, the Dong codes introduce extra coding to protect the check bits of the original information word. The coding method presented in Dong (1984) uses duplication to achieve check bit protection. In this manner, the entire word is generated in the following manner:

- From the original data word, count the number of '0's (I<sub>0</sub>) present and append the binary representation of this number to the original data word. This is a Berger code.

- Perform the bit-by-bit complement of the binary representation of the number of '0's, and append this number after the Berger code.

The resultant Dong code is more expensive than the Berger code in terms of both check bits and the cost of the self checking checkers. Also, their efficiency is slightly lower than the Berger codes for a given number of check bits, although the Dong codes can detect all unidirectional errors of weight less than I<sub>0</sub> (Dong (1984)). The decoding of the received data word consists of a Berger code checker and a two rail checker operating upon the two versions of the received check bits. A detailed explanation of the generation of Dong codes is given in Dong (1984), along with the error detection ability and the method for generating totally self checking checker circuitry.

The second and more optimal separable t-unidirectional error detecting code is the Bose code as described by Bose (1985). Bose codes are separable and require a fixed number of check bits for a particular level of error protection that is independent of the number of information bits. In addition, Piestrak (1995) states that the Bose codes are optimal and self checking checkers are easy to realise. The Bose codes are constructed by counting the number of '0's (I<sub>0</sub>) in the information word and taking the binary representation of I<sub>0</sub> mod 2<sup>r</sup> where r is the number of check bits. As an example, the Bose code for the information word of '00001101' with two check bits is '00001101 01'. The choice of the number of check bits to use is determined by the number of errors requiring detection. Bose (1985) shows that for double error detecting, two check bits are needed, while for triple error detecting, three check bits are needed. The proof of the optimality of the Bose codes is given in Bose (1985), along with the methods for generating totally self checking circuits for checking the received codewords.

# 2.5.3.3 Burst Unidirectional Error Detecting Codes

Certain faults in semiconductor memories tend to produce bursts of unidirectional errors. Hence, codes capable of detecting bursts of a certain length using a minimum number of check bits are important. To date, no non-separable burst unidirectional error detecting (b-UED) codes have been proposed. However, separable b-UED codes were first proposed by Bose (1986) and improved by Blaum (1988). It has been stated

in Piestrak (1995) that if b(K) denotes the maximum length of a burst error detectable by a separable b-UED code with K check bits, then the Bose codes have  $b(K) = 2^{K-1}$  for all K. Alternatively, the Blaum codes have  $b(K) = 2^{K-1}$  for K = 2,3 and  $b(K) > 2^{K-1}$  for  $K \ge 4$ . Consequently the Blaum codes are more efficient than the Bose codes for larger K. However, both are discussed for completeness.

### 2.5.3.3.1 Separable Burst Unidirectional Error Detecting Codes

The separable burst unidirectional error detecting codes considered are the Bose codes and the Blaum codes. Bose (1986) originally developed a burst unidirectional error detecting code containing r check bits which could detect any error burst of length up to 2<sup>r-1</sup>. Any of the t-unidirectional error detecting codes previously discussed are also capable of detecting burst unidirectional errors of length t. However, the Bose code is more efficient than the t-unidirectional error detecting codes in that its error detecting performance stays constant at 2<sup>r-1</sup> (where r is the number of check bits), while the t-unidirectional error detecting codes suffer from lower error detecting performances for larger numbers of check bits as noted by Bose (1986). Consequently, the Bose code is superior for a larger number of burst errors and larger numbers of check bits. The Bose code checkbits are determined by:

Check Bits =

$$I_0 \pmod{2^r}$$

where  $I_0$  is the zero weight of the information word, and r is the number of check bits. The most significant check bit is then inserted into the information word while the remainder of the check bits are appended to the end of the information word. As an example, if k = 12, r = 3, and the information symbol is '1100 0100 0000', then the check is given by 9 mod  $2^3 = 9 \mod 8 = 1 = 001_2$ . Thus the code word will be as follows:

The MSB of the check is placed between the information bits  $I_2^{r-1}$  and  $I_2^{r-1}$  as shown. Full details of the code construction are given in Bose (1986), along with the design of encoding and decoding circuitry.

The second burst unidirectional error detecting code considered is the Blaum code as presented in Blaum (1988). Blaum (1988) shows that the Blaum code is capable of detecting bursts of errors of length greater than  $2^{r-1}$  when the number of check bits (r) is  $\geq 4$ . In contrast to this, the previously discussed Bose code is capable of detecting burst errors of length  $2^{r-1}$  when the number of check bits (r) is  $\geq 3$ . The Blaum code is thus superior to the Bose code and is constructed in the following manner:

check number =

$$I_0 \mod 2^r$$

where I<sub>0</sub> is the zero weight of the information part and r is the number of check bits. The check bits are found by looking up the check number in tables found in Blaum (1988). The check bits are then inserted into the information word at specific bit positions determined by the minimum of the formula in Blaum. The tables are constructed from mathematical formulae which are beyond the scope of this review but are discussed in detail in Blaum (1988). As an example, consider the case of the information word '101001110', which has weight 4. From the tables in Blaum, the check bits are '010' and the minimum is 4. The constructed code is thus:

This code will detect all burst errors up to length 4. A comparison of the burst error detecting ability of the Blaum and Bose codes for increasing number of check bits is

given in Blaum (1988), where it is shown that the Blaum codes are superior for check bit numbers of  $\geq 4$ . Methods for constructing encoding and decoding circuits are also given in Blaum (1988), along with totally self checking checker designs.

## 2.5.3.4 Summary of Unidirectional Error Detecting Codes

The unidirectional error detection codes presented possess a variety of error detection properties, including the ability to detect single, multiple and burst unidirectional errors. The codes usually implemented are the separable codes as these can be easily constructed and checked with simple encoding and decoding of the information bits. This usually involves smaller delays and lower hardware overhead than the generally more complex non-separable codes. The unordered codes considered were the m-out-of-n and Berger codes. It has been stated that the m-out-of-n codes are optimal when m = n/2 as this allows the maximum number of codewords, while the Berger codes are optimal in check bits if all codewords are used. However, the m-out-of-n code is non-separable while the Berger code is separable. Consequently, the Berger code is used more due to the difficulty and complexity in encoding and decoding the non-separable m-out-of-n code.

The t-unidirectional error detecting codes considered were the Borden, Dong and Bose codes. Again it was stated that the Borden and Bose codes were more efficient than the Dong codes for a fixed number of unidirectional errors. The Borden codes were shown to be optimal t-unidirectional error detecting codes provided the weight of the codewords was  $\lfloor n/2 \rfloor \mod (t+1)$ . Unfortunately, they are non-separable with all the associated problems. The Bose codes were stated to be separable and optimal in check bits.

Finally, the burst unidirectional error detecting codes considered were the Bose and Blaum codes. It was stated that the Blaum codes were more efficient than the Bose codes if the number of check bits is greater than four. Both codes were separable

hence making encoding and decoding easier. To date, no non-separable burst unidirectional error detecting codes are known.

## 2.5.4 Parity Based Codes

Parity based codes are the simplest coding technique to implement, with the parity bit generated by the EXOR of all the bits in the data word. The parity bit is then appended to the data word to form a code which is capable of detecting single bit errors. Any single bit error is easily detected as the parity will change from odd to even or vice versa. The ability to detect errors can be quantified by the Hamming distance, which is the number of bits by which any two codewords differ. For the simple parity code, the Hamming distance is two, which allows the detection but not correction of single bit errors. Consequently, if two errors occurred, the parity scheme would not be able to detect the errors. In general, any code of Hamming distance (d+1) is capable of detecting d errors, while a code of Hamming distance (2c+1) is capable of detecting and correcting up to c errors. If the Hamming distance is 3, then the code can detect double bit errors and correct single bit errors. The parity code can be generated by several different methods as described below.

# 2.5.4.1 Bit-per-Word Parity

Bit-per-word parity is a technique where one parity bit is appended to the entire data word. This causes the least hardware overhead as it requires a minimum of redundancy in the information transferred. It also allows a single parity tree to be used for both encoding and decoding of the data provided the data is transmitted in full duplex mode. According to Siewiorek (1992), bit-per-word parity codes can detect all single-bit errors and all errors that involve the corruption of an odd number of bits. A slightly different approach is that of bit-per-byte parity, where an extra bit is appended to each byte of data rather than the entire word as previously discussed. This technique

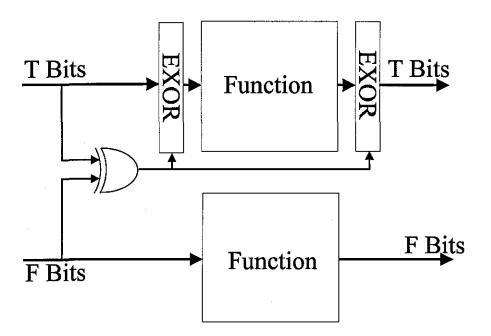

also detects single or odd numbers of errors in each byte. Another advantage of the bit-per-byte technique is that fewer bits are covered by each parity bit, thus improving the resolution of any diagnostic procedures. This technique also suffers less from the encoding and decoding speed penalties since the parity trees are more compact.

## 2.5.4.2 Interlaced Parity

Interlaced parity is a technique where i parity bits are appended to the data word. Each parity bit is associated with a group of (b/i) bits (b is the data word length). This is achieved by forming the parity over every b/i<sub>th</sub> bit, starting in a different bit position for each parity group. Siewiorek (1992) states that interlaced parity covers single bit errors in each group, and multiple errors providing at least one group has an odd number of errors. Siewiorek (1992) also states that if the parity is alternated from group to group, the interlaced parity code also covers a large number of unidirectional errors. As for the bit-per-byte parity technique, the resolution of any diagnosis is to the parity group in error. The speed of error detection and initial encoding is also increased due to the more compact parity tree.

# 2.5.4.3 Parity Check Matrix

To determine the number of check bits required by any given parity code, the Hamming relationship can be used. This is given by:

$$2^k \ge m + k + 1$$

where m is the number of information bits, and k is the number of check bits required. If, for example, an 8 bit single error correcting code was required, then m = 8 and k = 4 corresponding to four check bits and 12 bits in total. In a parity check matrix representation, the check bits are inserted into the original message at the power of two bit positions. This has the advantage that comparing the regeneration of the check

bits at the receiver with the received check bits can lead to the correction of a single bit error as described by Russell (1989).

### 2.5.4.4 Summary of Parity Based Codes

Parity based codes are perhaps the easiest information redundant code to implement as the encoding / decoding consists purely of an EXOR tree and an extra data bit (and storage element if the circuit is sequential). This is easily realised and also provides a reasonably low cost solution to on-line error detection. However, the parity based coding schemes are limited by their ability to detect only an odd number of errors within the group of bits the parity is covering. A trade-off is then apparent between the hardware implementation cost and the level of protection offered by the parity code. Consequently, the parity based codes are best suited to implementations which require a low hardware overhead and can tolerate a lower level of data protection. A totally self checking checker for the parity code consists of a tree of EXOR gates split into two parts such that a two-rail code is generated as described in Khakbaz (1984) and Piestrak (1995).

# 2.5.5 Summary of Information Redundant Techniques