This item was submitted to Loughborough's Research Repository by the author. Items in Figshare are protected by copyright, with all rights reserved, unless otherwise indicated.

# Study of self-alignment of µBGA packages

PLEASE CITE THE PUBLISHED VERSION

**PUBLISHER**

© IEEE

**VERSION**

VoR (Version of Record)

LICENCE

CC BY-NC-ND 4.0

REPOSITORY RECORD

Hung, K.C., Y.C. Chan, P.L. Tu, H.C. Ong, D. Patrick Webb, and J.K.L. Lai. 2019. "Study of Self-alignment of Mbga Packages". figshare. https://hdl.handle.net/2134/4105.

This item was submitted to Loughborough's Institutional Repository (https://dspace.lboro.ac.uk/) by the author and is made available under the following Creative Commons Licence conditions.

Attribution-NonCommercial-NoDerivs 2.5

#### You are free:

• to copy, distribute, display, and perform the work

### Under the following conditions:

Attribution. You must attribute the work in the manner specified by the author or licensor.

Noncommercial. You may not use this work for commercial purposes.

No Derivative Works. You may not alter, transform, or build upon this work.

- For any reuse or distribution, you must make clear to others the license terms of

- Any of these conditions can be waived if you get permission from the copyright holder.

Your fair use and other rights are in no way affected by the above.

This is a human-readable summary of the Legal Code (the full license).

Disclaimer 🗖

For the full text of this licence, please go to: http://creativecommons.org/licenses/by-nc-nd/2.5/

# Study of Self-Alignment of $\mu$ BGA Packages

K. C. Hung, Y. C. Chan, Senior Member, IEEE, P. L. Tu, H. C. Ong, D. P. Webb, and J. K. L. Lai

Abstract-In this paper, a detailed study of the self-alignment of  $\mu$ BGA packages is presented. Complete self-alignment can be achieved even for a misalignment of the package of larger than 50% off the test board pad centres. A small residual displacement of the package from perfect alignment after reflow is observed. The reason for this displacement is the action of gas flow viscous drag on the package during reflow. The use of eutectic SnPb solder paste slightly reduces self-aligning ability, due to the increase in the solder volume, which reduces the restoring force. Exposure of the solder paste to a 25  $^{\circ}\text{C}$  and 85% RH humidity environment also has a detrimental effect on the self-alignment of the  $\mu BGA$ package, due to solvent evaporation and moisture absorption in the paste causing solderability degradation. The self-alignment of the package is also affected when there is slow spreading of molten solder on the pad surface. This is attributed to the reduction of restoring force due to the decrease in effective wetting surface area of the board pad.

Index Terms—Gas flow effect, self-alignment,  $\mu BGA$  package, wetting.

#### I. Introduction

$\mathbf{R}$  OR the portable electronics market, the size and weight of the product are among the most significant issues determining market share. This in turn drives the need for electronic components and electronic packages that are as thin, small, and lightweight as possible [1]. A consequence is burgeoning interest in chip scale packages (CSP) [2]. As is typical with an emerging market, there are many different CSP solutions offered by a variety of companies. The micro ball grid array ( $\mu$ BGA) package is one such package that has been successfully deployed for portable devices by big companies like Intel [3].

The  $\mu$ BGA package is unique in its construction. It uses a flexible circuit film as the substrate material. The chip is die attached to this material with a low stress, elastomeric adhesive. The circuit traces are formed into leads on certain sections of the tape and these leads are bonded directly to the bond pads on the chip. An elastomeric encapsulant-type of material surrounds the lead and chip bond pads, and finally solder bumps are attached to bump pad openings in the circuit tape. Since the size and pitch of the solder bumps are quite small (only 0.35 and 0.75 mm, respectively), high pick and place accuracy compared to older SMT standards is necessary. It is known that slightly misaligned parts (less than 50% off the pad centre) will auto-

Manuscript received May 22, 1999; revised April 14, 2000. This work was supported by the Direct Allocation Grants (Project 7 100 071) and the Strategic Research Grants (Project 7 000 955), City University of Hong Kong.

K. C. Hung, Y. C. Chan, P. L. Tu, H. C. Ong, and D. P. Webb are with the Department of Electronic Engineering, City University of Hong Kong, Kowloon, Hong Kong.

J. K. L. Lai is with the Department of Physics and Materials Science, City University of Hong Kong, Kowloon, Hong Kong.

Publisher Item Identifier S 1521-3323(00)07197-5.

matically self-align during reflow for the ball grid array and similar packages [4], [5]. However, up to now, detailed study of the self-alignment of the  $\mu$ BGA packages is lacking. This paper studies the self-alignment ability of the  $\mu$ BGA package. Some important parameters that affect the self-alignment will also be discussed.

#### II. EXPERIMENTATION

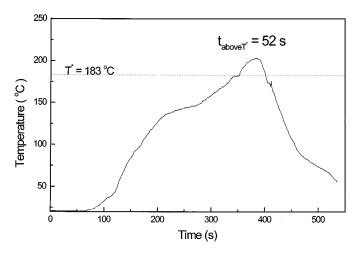

The samples used in this study are the dummy versions of Tessera's  $\mu$ BGA package in which the bump size and pitch are respectively 0.35 and 0.75 mm, and the solder bump material is eutectic 63Sn/37Pb. The test board for assembly of the  $\mu$ BGA packages is composed of FR4. There are two categories of test board pads. Both are of copper plated with nickel but with different thickness of thin layer of gold flash on top. The diameter of the test board pads is 0.30 mm. Before mounting the  $\mu$ BGA packages onto the test board, no-clean flux is dispensed onto the test board pads. Two flux formulations, low viscosity (LV) and high viscosity (HV), are used in this study. Alternatively, no-clean 63/37 solder paste is printed onto the test board pads using a screen printer with a stencil of 0.1 mm thickness. The stencil life of this solder paste as claimed by the supplier is longer than 8 h. Following application of flux or paste, the  $\mu$ BGA samples are mounted on the test boards by a high-precision, high-speed flexible mounter (CASIO YCM-5500V). We make use of the high accuracy of the mounting machine to control the misalignment of the  $\mu$ BGA samples on the board pads. The misalignments chosen are 0, 0.05, 0.10, 0.15, and 0.20 mm. Before reflow, the mounted samples are inspected to ensure the correct misalignment by use of a SOFTEX real time x-ray inspection system. A five-zone reflow gas-forcedconvection oven (BTU VIP-70N) is used to reflow the mounted samples in a compressed air environment. The time-resolved temperature during reflow between the component and the test board is measured using a wireless profiler (Super M.O.L.E, E31-900-45/10). A typical reflow profile is shown in Fig. 1. In this figure, the time above the melting temperature T\*=183 °C of the eutectic solder is  $t_{above T^*} = 52$  s. After the assembly process, the samples are inspected by the x-ray inspection system again. Additionally, electrical tests, cross sectioning, and optical microscopic analysis are performed.

## III. RESULTS AND DISCUSSION

A. Effects of Different Levels of Misalignment, Sample Flow Direction, and Viscosity on Self-Alignment of µBGA Packages

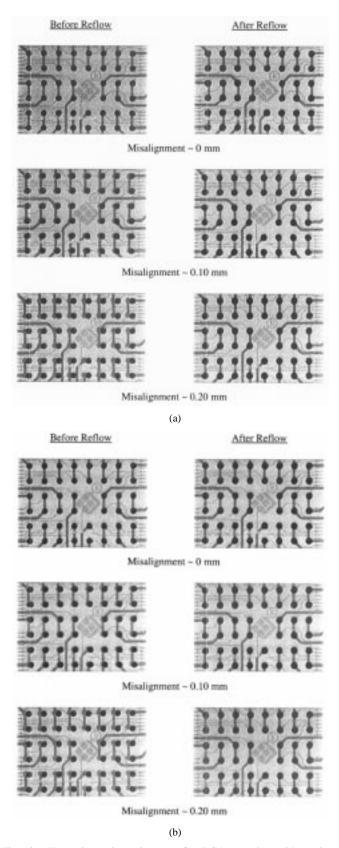

X-ray pictures of  $\mu$ BGA samples with various initial misalignments before and after reflow are shown in Fig. 2, in which (a) the sample flow direction is from left to right, and (b) the sample flow direction is reversed. The no-clean flux used is the

Fig. 1. Measured temperature reflow profile used with the  $\mu$ BGA packages. The time spent above the melting temperature T\*=183 °C of the eutectic solder is 52 s.

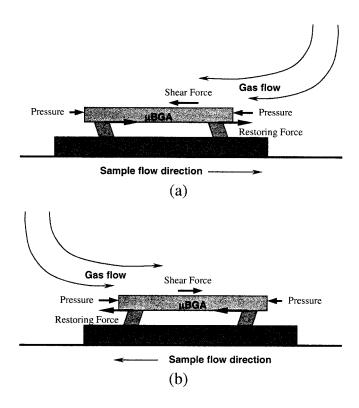

low viscosity type. It can be seen that even for a misalignment of larger than 50% off the pad centre, the package is still able to self-align. It is interesting that in all cases a small residual displacement toward the side opposite to the sample flow direction of around 20 to 40  $\mu \rm m$  after reflow can be observed. This displacement can be explained by using the schematic force balance diagram shown in Fig. 3. Since the mounted  $\mu \rm BGA$  samples are reflowed in a compressed air environment, the gas flow produces a viscous drag which can pull the package away from the desired position. In fact, the drag force caused by the gas flow includes both the shear force and the pressure acting on the sides of the package. In this figure, the vertical component of pressure is ignored since it will only affect the stand-off height in between the  $\mu \rm BGA$  and PCB. The force balance is governed by

### Drag force + Restoring force = 0.

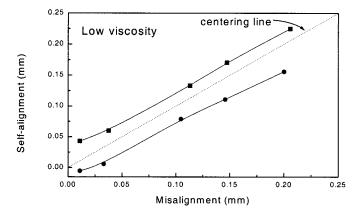

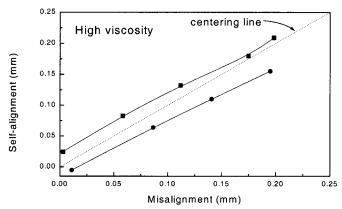

The slight misalignment of the package in the balance position creates an opposing restoring force to balance the drag force due to the gas flow effect. Therefore, in Figs. 2(a) and 3(a), since the sample flow direction is from left to right, there is a drag force created in the opposite direction, and the solder joints are slightly misaligned to the left. In Figs. 2(b) and 3(b) the drag acts from left to right so the solder joints are slightly off-center to the right. Figs. 4 and 5 show plots of self-alignment against misalignment for the  $\mu$ BGA packages using low viscosity and high viscosity flux respectively. The self-alignment is the distance moved from the initial misalignment to the final equilibrium position. The centering line is a reference line for a solder ball aligned at equilibrium exactly at the pad centre. The upper curve represents the self-alignment results in which the initial misalignment is on the same side as the sample flow direction, while the lower curve represents the self-alignment results in which the initial misalignment is opposite to the sample flow direction. It can be seen that both curves show offset from the centering line. Even when there is no initial misalignment of the package, there is still a displacement from the ideal position. Therefore, the gas flow effect must be considered when

Fig. 2. X-ray inspection pictures of  $\mu$ BGA samples with various misalignments before and after reflow, in which (a) the sample flow direction is from left to right and (b) vice versa.

using lightweight advanced packages like CSP and flip chip. Comparing Figs. 4 and 5, the viscosity of the flux seems to have

Fig. 3. Schematic force balance diagram of the  $\mu$ BGA package during reflow, in which (a) the sample flow direction is from left to right and (b) vice versa.

Fig. 4. The relationship between self-alignment and misalignment of  $\mu$ BGA samples using low viscosity flux. The centering line indicates perfect self-alignment.

no effect on the self-alignment of the  $\mu$ BGA packages. However, it is known that the higher the flux viscosity, the lower the defect rate at reflow. This has been attributed to the fact that it is more difficult for a component to move through a high viscosity flux during board preparation, handling and initial reflow [6]. In addition, it can be seen that the greater the misalignment, the greater the self-alignment. Theoretically, increasing the misalignment will lead to increase the restoring forces that move the package toward the balanced position [7], and thus increase the distance moved to the desired balance position, i.e., restoring force  $\propto$  self-alignment  $\propto$  misalignment.

Fig. 5. The relationship between self-alignment and misalignment of  $\mu$ BGA samples using high viscosity flux. The centering line indicates perfect self-alignment.

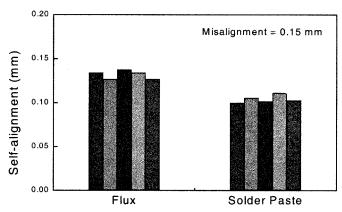

Fig. 6. Comparison between self-alignment of two groups of samples using flux and using solder paste, for an initial misalignment of 0.15 mm.

### B. Effect on Self-Alignment Using Flux and Solder Paste

Fig. 6 shows a bar chart of the self-alignment of two groups of samples using flux and solder paste at a misalignment level of 0.15 mm. This figure shows that the self-alignment using flux is larger than that using solder paste. Based on the simple-estimation formulas [8], the restoring force  $f_s(P)$  is a function of misalignment P as follows:

$$f_s(P) = \frac{\pi}{2} \gamma (r_c + r_s) \left\{ \frac{P + r_c - r_s}{[(P + r_c - r_s)^2 + h^2]^{1/2}} + \frac{P - r_c + r_s}{[(P - r_c + r_s)^2 + H_c^2]^{1/2}} \right\}$$

(1)

$$H_c = \frac{3V}{\pi (r_c^2 + r_c r_s + r_s^2)}$$

(2)

where  $\gamma$  is the surface tension coefficient,  $r_c$  the package pad radius,  $r_s$  the board pad radius, h the height of solder joint, and V the solder volume. If  $\gamma$ ,  $r_c$ ,  $r_s$ , h, and P are all fixed, an increase in solder volume V will lead to a reduction in the restoring force  $f_s$ . By adding solder paste to the board pad, the total solder volume per joint will be slightly increased at reflow. As a result, the addition of solder paste reduces the restoring force and thus the self-alignment.

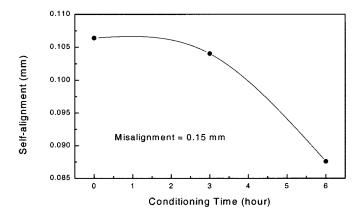

Fig. 7. Self-alignment against conditioning time for solder paste conditioned at 25  $^{\circ}\mathrm{C}$  and 85% RH humidity.

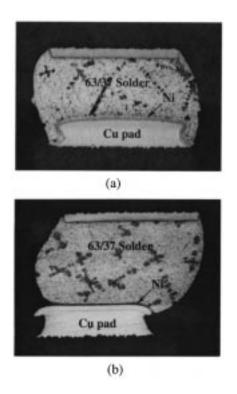

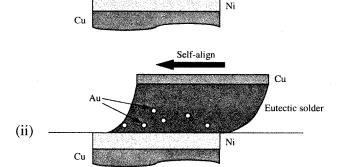

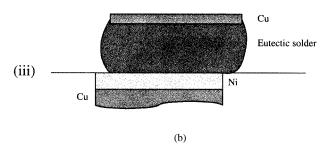

Fig. 8. Optical micrographs of cross sections of  $\mu$ BGA solder joints using (a) a pad of copper plated with nickel and 1000 Å gold flash on top and (b) a pad of copper plated with nickel and 100 Å gold flash on top.

# C. Effect of Time Exposed to the Environment on Self-Alignment

Fig. 7 shows a plot of self-alignment against conditioning time for solder paste conditioned in a humidity chamber. In this experiment, we first stencil the solder paste onto the board pads and then condition these test boards in the temperature and humidity chamber at 25 °C and 85% RH. After removal from the chamber the boards are loaded with  $\mu$ BGA packages and reflowed. From Fig. 7, it may be seen that the self-alignment is only slightly reduced after the first 3 h conditioning but drops greatly after 6 h. In fact, as solder paste is worked and exposed to the environment, solvent evaporates and moisture from the air is absorbed [9]. As a result, the fluxing ability of

(i)

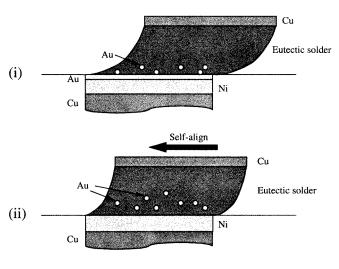

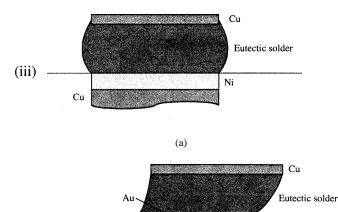

Fig. 9. Schematic diagrams depicting the process of self-alignment of the package for (a) a 1000 Å-Au/Ni/Cu pad and (b) a 100 Å-Au/Ni/Cu pad. Stage (i) is the initial wetting reaction of eutectic solder and Au thin layer on the Au/Ni/Cu board pad; stage (ii) is the dissolution of Au into the eutectic solder and self-alignment to the desired position; and stage (iii) is the final position of the solder.

the solder paste will be degraded, affecting the self-alignment of the  $\mu BGA$  packages.

# D. Effect of Different Au Thickness Coating of Test Board Pad on Self-Alignment

Fig. 8 shows optical micrographs of cross sections of solder joints using (a) a board pad of copper plated with nickel and about a 1000 Å thin layer of gold on top, and (b) a board pad of copper plated with nickel and about a 100 Å thin layer of gold flash on top. The initial misalignment of the  $\mu$ BGA packages for these two figures is 0.20 mm. The self-alignment of the  $\mu$ BGA package shown in Fig. 8(a) is very good and the  $\mu$ BGA package is almost aligned to the centre of the board pad even though the initial misalignment was larger than 50% off the pad centre. However, in Fig. 8(b), it can be seen that the self-alignment is much worse. Closer inspection reveals that the solder has not wet the pad properly. In our previous work of wetting dynamic experiment [10], it is found that the spreading of molten solder on 1000 Å Au layer pad is faster than that on 100 Å Au layer pad. In order to have a clear interpretation, the effect of different degree of spreading on the self-alignment of the package is illustrated by the diagrams in Fig. 9(a) and (b) for the 1000 Å Au layer pad and the 100 Å Au layer pad, respectively. There are three stages. The first stage (i) is the reactive wetting of the eutectic solder on the Au thin layer in the initial stages of reflow following the action of the flux on the surfaces to be joined. However, since the spreading of molten solder on 100 Å Au layer pads is much slower, the effective board pad surface area that can be wetted by the molten solder may be smaller. That is, the molten solder may not wet the whole area of the 100 Å Au layer pad due to the slow spreading of molten solder. In the meantime, the thin Au layer starts to dissolve into the molten solder. The second stage (ii) shows the very thin Au layer dissolving into the eutectic solder exposing the Ni surface to the eutectic solder at the interface. At the same time, the package self-aligns to the desired position. Actually, in Fig. 9(b), the restoring force for the solder joints using 100 Å Au layer pads will be reduced due to the smaller board pad surface area that can be wetted by the molten solder. As a result, the change of equilibrium condition will cause less better self-alignment of the package using 100 Å Au layer pad, which is shown in stage (iii) of Fig. 9(b).

# IV. CONCLUSION

In summary, we have made a detailed study of the self-alignment of  $\mu BGA$  packages. It is found that a  $\mu BGA$  package can still self-align even for an initial misalignment of larger than 50% off the pad centre. It is found that the gas flow during reflow causes a small residual displacement of the package away from the ideal position due to drag forces. The flux viscosity seems to have no effect on the self-alignment of the  $\mu BGA$  package. The use of solder paste is found to slightly reduce the self-alignment ability due to the increase in solder joint volume during reflow. Exposure of the solder paste to conditioning at 25 °C and 85%

RH for 6 h significantly reduces the self-alignment. This is attributed to evaporation of solvent and absorption of moisture leading to the degradation of solderability and thus reduction in the self-alignment of the package. Finally, we have observed less better self-alignment for 100ÅAu/Ni/Cu board pads. The probable cause is the reduction of restoring forces due to slow spreading of the molten solder on the pad surface.

#### REFERENCES

- [1] M. Teska, "Fine line PCB assembly leads to new test issues," *Electron. Packag. Prod.*, pp. 54–56, Jan. 1998.

- [2] S. Crum, "Chip scale packages moving into the mainstream," *Electron. Packag. Prod.*, pp. 43–46, Jan. 1997.

- [3] Intel Program Overview, μBGA Package Technology, May 1998.

- [4] S. Greathouse, "Self-centering of BGA's and solder interconnects," Electron. Packag. Prod., pp. 65–72, Aug. 1997.

- [5] Y. C. Lee, "Studies on solder self-alignment," in *Proc. LEOS'94 Conf.*, 1, pp. 73–74.

- [6] S. Greathouse, "Surface tension and the self-centering of BGAs," Surface Mount Technol., vol. 11, no. 5, pp. 82–86, May 1997.

- [7] S. K. Patra and Y. C. Lee, "Modeling of self-alignment mechanism in flip-chip soldering—Part II: Multichip solder joints," in *Proc. 41st Elec*tron. Comp. Technol. Conf., 1991, pp. 783–788.

- [8] —, "Quasistatic modeling of self-alignment mechanism in flip-chip soldering process, Part I: Single joint," ASME J. Electron. Packag., pp. 337–342, Dec. 1991.

- [9] C. Bastecki and S. Breed, "Measuring solder paste printing performance," *Circuits Assembly Asia*, pp. 36–38, Nov./Dec. 1998.

- [10] K. C. Hung, Y. C. Chan, H. C. Ong, P. L. Tu, and C. W. Tang, "Effect of pinhole Au/Ni/Cu substrate on self-alignment of advanced packages," *Mater. Sci. Eng. B*, vol. 76, no. 2, pp. 87–94, 2000.

**K. C. Hung** received the B.Sc. degree in applied physics from the City Polytechnic of Hong Kong (now City University of Hong Kong) in 1993 and the Ph.D. degree in physics and materials science from the City University of Hong Kong in 1998.

He currently works in the Department of Electronic Engineering, City University of Hong Kong, as a Research Fellow. He has authored or co-authored over 30 technical publications in refereed journals. His current research interests include advanced electronics packaging technology, reliability engineering, failure analysis, and nondestructive testing.

Y. C. Chan (SM'95) received the B.Sc. degree in electrical engineering, the M.Sc. degree in materials science, and the Ph.D. degree in electrical engineering, all from the Imperial College of Science and Technology, University of London, London, U.K., in 1977, 1978, and 1983, respectively.

He joined the Advanced Technology Department, Fairchild Semiconductor, Pasadena, CA, as a Senior Engineer, and worked on integrated circuits technology. In 1985, he was appointed to a Lectureship in Electronics at the Chinese University of Hong

Kong. Between 1987 and 1991, he worked in various senior operations and engineering management functions in electronics manufacturing (including SAE Magnetics (HK) Ltd. and Seagate Technology). He set up the Failure Analysis and Reliability Engineering Laboratory for SMT PCB, Seagate Technology, Singapore. He joined the City Polytechnic of Hong Kong (now City University of Hong Kong) as a Senior Lecturer in Electronic Engineering in 1991. He is currently Professor in the Department of Electronic Engineering and Director of EPA Centre. He has authored or co-authored over 100 technical publications in refereed journals and conference proceedings. His current technical interests include advanced electronics packaging and assemblies, failure analysis, and reliability engineering.

P. L. Tu received the B.S. degree from the Beijing University of Aeronautics and Astronautics, Beijing, China, the M.S. degree from the Nanjing University of Aeronautics and Astronautics, Nanjing, China, in 1988, and is currently pursuing the Ph.D. degree in the Department of Electronic Engineering, City University of Hong Kong.

His research interests are in reliability study of area array solder joint, such as BGA, CSP, and flip chip, in degradation mechanisms of ACF, and in adhesion strengths of underfill.

H. C. Ong received the B.A. degree in chemistry/biochemistry (with distinction) and the Ph.D. degree in materials science and engineering from Northwestern University, Evanston, IL, in 1992 and 1996, respectively. His doctoral work involved the deposition of diamond-related materials and material characterizations

In 1997, he was employed as Research Fellow at Northwestern University working on the development of polycrystalline ZnO as a new generation of optoelectronic material. He was then appointed as Research Assistant Professor in Materials Research Center, Northwestern University, in 1998. He joined the City University of Hong Kong as Assistant Professor of electronic engineering in 1998. He has published over 20 papers in international refereed journals and supervised one master thesis. His research interest covers the areas of thin film growth, plasma spectroscopy, and material characterization.

Dr. Ong is one of the finalists in the Graduate Student Award, Materials Research Society. He is a member of Phi Beta Kappa and the Materials Research Society.

**D. P. Webb** received the B.Sc. degree in mathematical physics (with honors) from the University of Science and Technology, Manchester, U.K., in 1988, the M.Sc. degree in amorphous and microcrystalline electronic materials from the University of Dundee, Dundee, U.K., in 1990, and the Ph.D. degree from the University of Abertay, Dundee, in 1994.

He took up a position in the Department of Electronic Engineering, City University of Hong Kong, in 1995 and is currently a Research Fellow. Projects at the City University of Hong Kong have included improvement of the wear properties of organic photoreceptor layers in xerography, and evaluation of a new fabrication technique for amorphous silicon. He is currently Principal Investigator on a City University Strategic Research Grant to study charge transport in organic electroluminescent device materials.

**J. K. L. Lai** received the M.S. degree in physics (with first class honors) from Keble College, Oxford University, Oxford, U.K., in 1974 and the Ph.D. degree from the Department of Mechanical Engineering, City University of London, London, U.K., in 1982.

From 1974 to 1985 he was employed as Research Officer at the Central Electricity Research Laboratories, Surrey, U.K. In 1984, he was appointed Project Leader of the Remaining Life Study Group and a member of the Remainent Life Task Force, Central Electricity Generating Board, U.K. He returned to Hong Kong and joined the City University of Hong Kong (previously City Polytechnic of Hong Kong) in 1985. He is now Chair Professor of Materials Science, Director of the Materials Research Centre and Associate Dean of the Faculty of Science and Technology. He has been very active in serving the local community. He is the joint inventor of a novel temperature indicator called "Feroplug" which has been patented in the U.K., USA, and Europe with financial support provided by the British Technology Group. He has acted as consultant for the Hong Kong Government and local industries on over forty cases of accidents/disputes involving the failure of metallic components. He has published over 80 papers in international refereed journals.

Dr. Lai received the Applied Research Excellence Award from the City University of Hong Kong in 1995 and the Teaching Excellence Award in 1996. He is a member of the Vocational Training Council, the Consumer Council, the City University Council, the Research Grants Council's Physical Sciences Panel, the Council and Executive Board of the Hong Kong Institution of Science, the Pressure Equipment Advisory Committee of the Labour Department, and the Electricity Ordinance Disciplinary Tribunal Panel.