This item was submitted to Loughborough's Research Repository by the author. Items in Figshare are protected by copyright, with all rights reserved, unless otherwise indicated.

# The continuous measurement of arterial pulse wave velocity

PLEASE CITE THE PUBLISHED VERSION

**PUBLISHER**

Loughborough University of Technology

LICENCE

CC BY-NC 4.0

REPOSITORY RECORD

Wheaton, Oliver J.. 2020. "The Continuous Measurement of Arterial Pulse Wave Velocity". Loughborough University. https://doi.org/10.26174/thesis.lboro.13128908.v1.

THE CONTINUOUS MEASUREMENT OF

ARTERIAL PULSE WAVE VELOCITY

This thesis was submitted to

the Department of Electrical Engineering of

Loughborough University of Technology, for the award

of the degree of Master of Science. June, 1966.

by.

Oliver J. Wheaton, D.L.C. (Eng)., Dip.Tech. (Eng).

Supervisor: J.M. Ivison, B.Sc., Ph.D., M.I.E.E.

Loughborough University

Of Technology Library

Date

Class

Acc. 0378570

#### ABSTRACT

This thesis describes a system which has been developed to continuously monitor the pulse wave velocity in the main systemic arteries in man, without surgical intervention.

The production of the pulse wave and its mode of propagation are discussed and the possible applications of a device of this nature.

Pulse wave velocity is surveyed in terms of its analytical relationship to blood pressure, its clinical information and the measurement techniques used by previous experimenters.

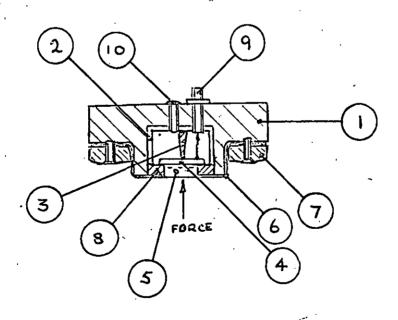

The problem, as considered, is stated and a system based on a novel measuring technique is developed to enable a high resolution to be obtained. The pulse wave velocity is defined as the speed of propagation of the wave peak between two points on the artery, a short distance apart. The wave is monitored by transducers which are designed with a fluid sac to avoid mounting and centering difficulties.

The system functions by first controlling signal amplitude from the transducers to give a constant output, exponential amplification is then used to selectively amplify the peak value. From this signal the peak is defined by differentiation. The velocity is obtained by measuring the delay, and then computing it from this using am analogue system.

A Simulator is described which produces a signal, which has a waveform similar to that of the pulse wave.

The simulator provides two channels with a variable time delay between them.

The design of the constituent parts of both systems is discussed in some detail.

The report concludes by giving suggested modifications to the systems described, and also indicates fields in which future work should proceed.

## CONTENTS

|           |       |                                                | Page | No. |

|-----------|-------|------------------------------------------------|------|-----|

|           |       | Abstract                                       | 1    |     |

|           |       | Contents                                       | 3    |     |

|           |       | List of Symbols and Abbreviations              | 5    |     |

|           |       | Acknowledgements                               | 7    |     |

| Section   | 1.    | Introduction and Summary of Earlier Works      | 8    |     |

| 11        | 2     | The Proposed System                            | 20   |     |

| 11        | 2.1   | Gain Control                                   | 22   |     |

| 11        | 2.2   | Delay Measurement                              | 22   |     |

| 11        | 2.2.1 | The Actual Delay Measuring System              | 25   |     |

| ŧŧ        | 2.3   | Analogue Divison                               | 28   |     |

| 17        | 2.3.1 | The Actual Analogue Divison System             | 30   |     |

| 11        | 2.4   | Display Facilities                             | 31   |     |

| <b>f1</b> | 2.5   | System Standardisation.                        | 32   |     |

| 11        | 3     | Pulse Wave Simulator                           | 36   |     |

| 11        | 4     | Design Consideration and Procedures            | 43   |     |

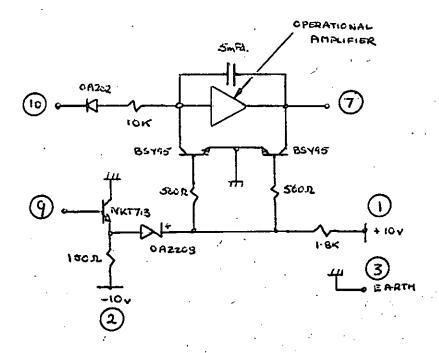

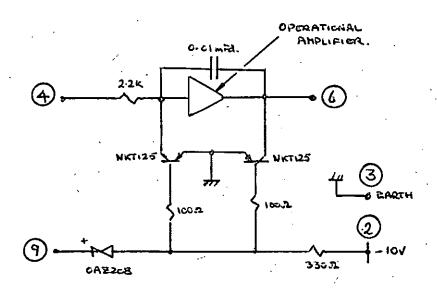

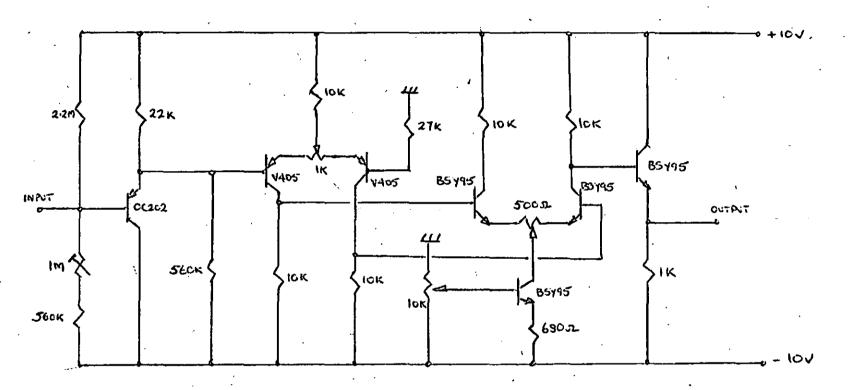

| 11        | 4.1   | Operational Amplfier Design                    | 43   |     |

| 11        | 4.2   | Integrator Resetting Gate Design               | 49   |     |

| 11        | 4.3   | Simple Operational Amplifier Design            | 52   |     |

| 11        | 4.3.1 | The Exponential Amplifier                      | 53   |     |

| Ħ         | 4.3.2 | The Differentiator                             | 55   |     |

| 11        | 4•4   | Astable and Monostable Pulse Generator Design. | r 57 |     |

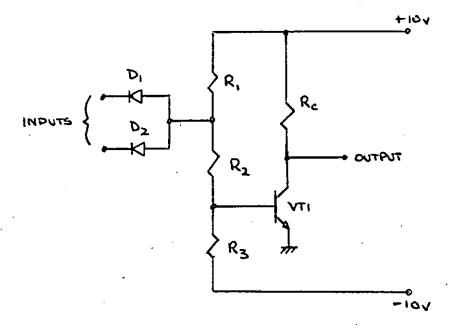

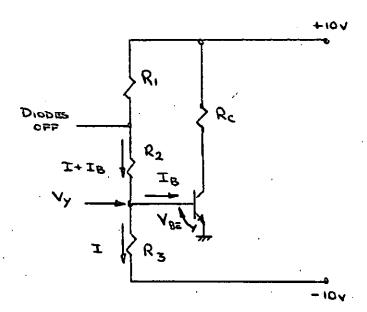

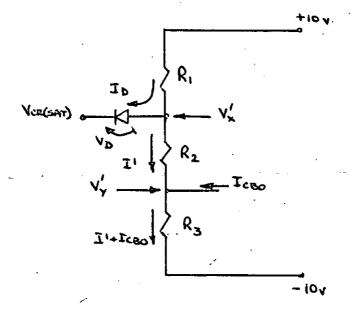

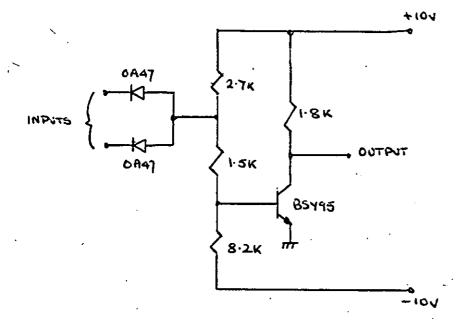

| 11        | 4.5   | Gate Design                                    | 61   |     |

| 11        | 456   | Analogue Gate, for Pulse Wave<br>Simulator     | 65   |     |

| 11        | 4.7   | Schmitt Trigger Design                         | 67   |     |

| Ц.,       | 4.8   | Automatic Gain Control Design.                 | 69   |     |

| 11        | 4.9   | Emitter Follower Design                        | 74   |     |

| 11        | 4.10  | DC Phase Correcting Amplifier                  | 7.7  |     |

| 11        | 4.11  | The Power Unit                                 | 78   |     |

• '

.

|                                         |     |                                                        | Page No.    |

|-----------------------------------------|-----|--------------------------------------------------------|-------------|

| Section:                                | 5   | The Transducer and its Pre-amplifier                   | 79          |

| 11                                      | 5.1 | Transducer Design.                                     | 80          |

| 11                                      | 5.2 | Transducer Pre-amplifier Design                        | 81          |

| 11                                      | 6   | Conclusions                                            | 84          |

| _ 11                                    | 6.1 | The Computer                                           | 84          |

| 11                                      | 6.2 | The Simulator                                          | 87          |

| 11                                      | 6.3 | Future Work                                            | 88          |

| 11                                      | 7   | Appendices                                             | 92          |

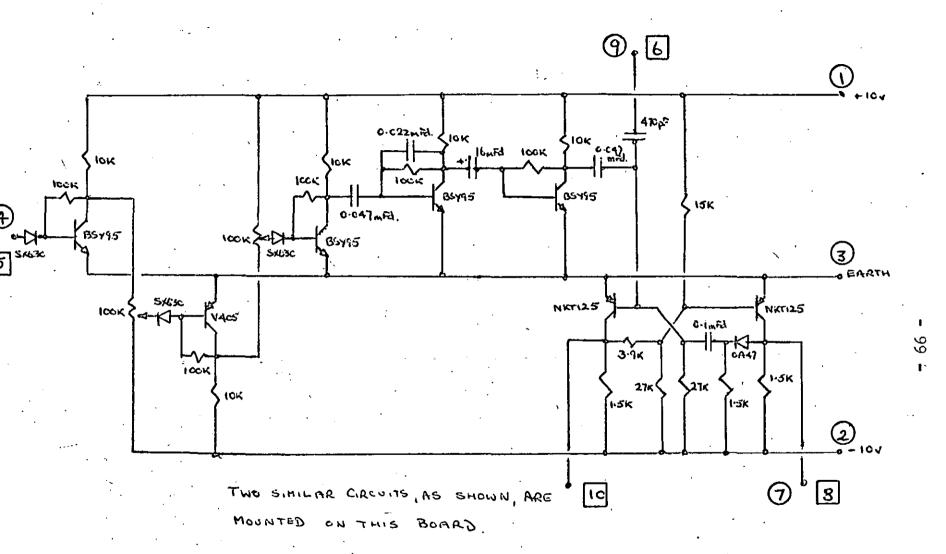

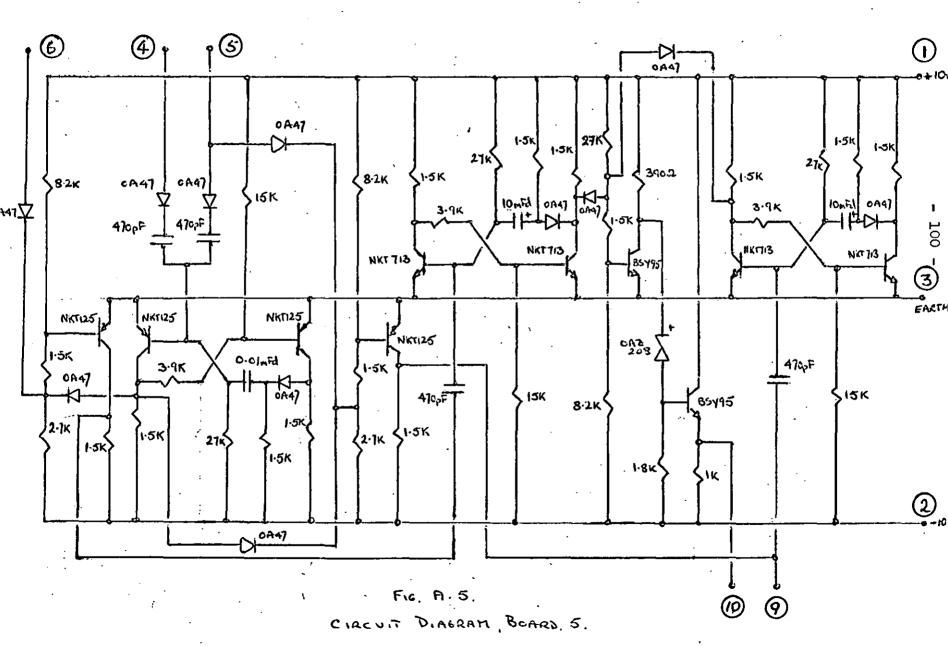

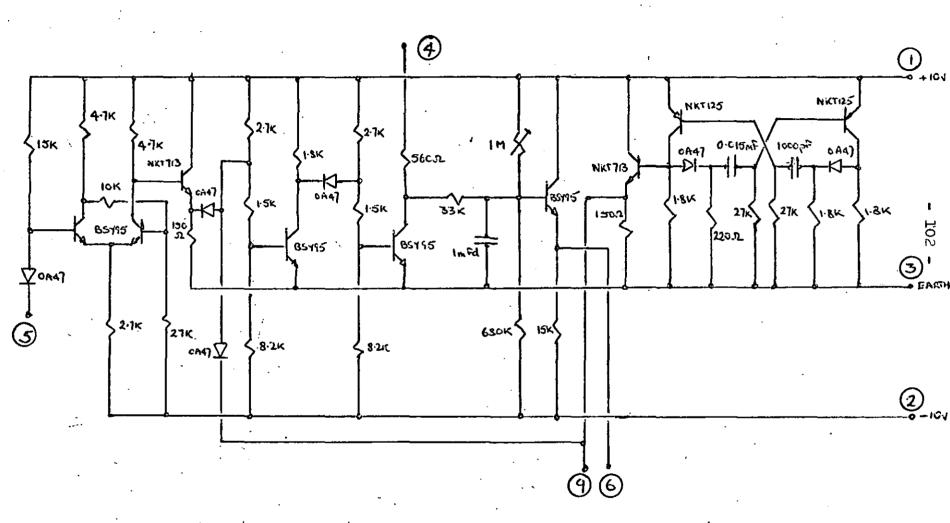

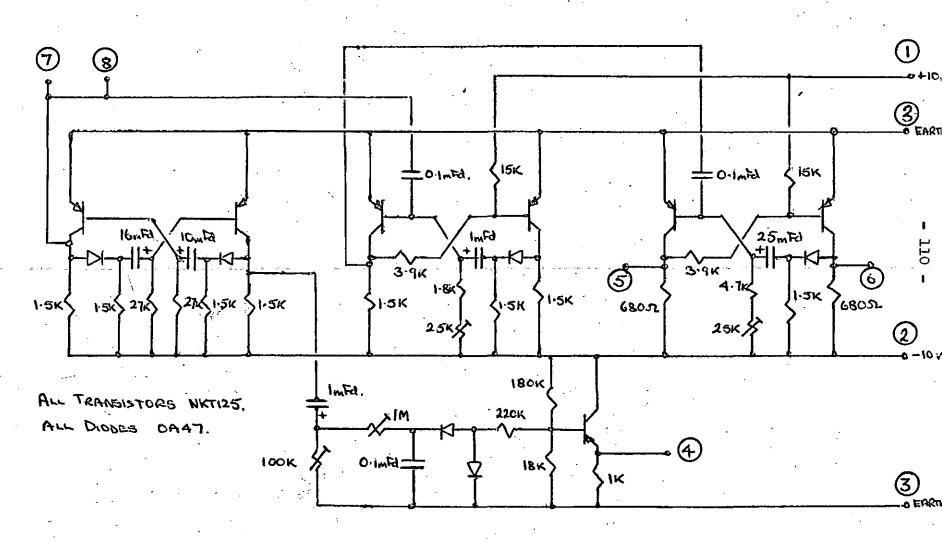

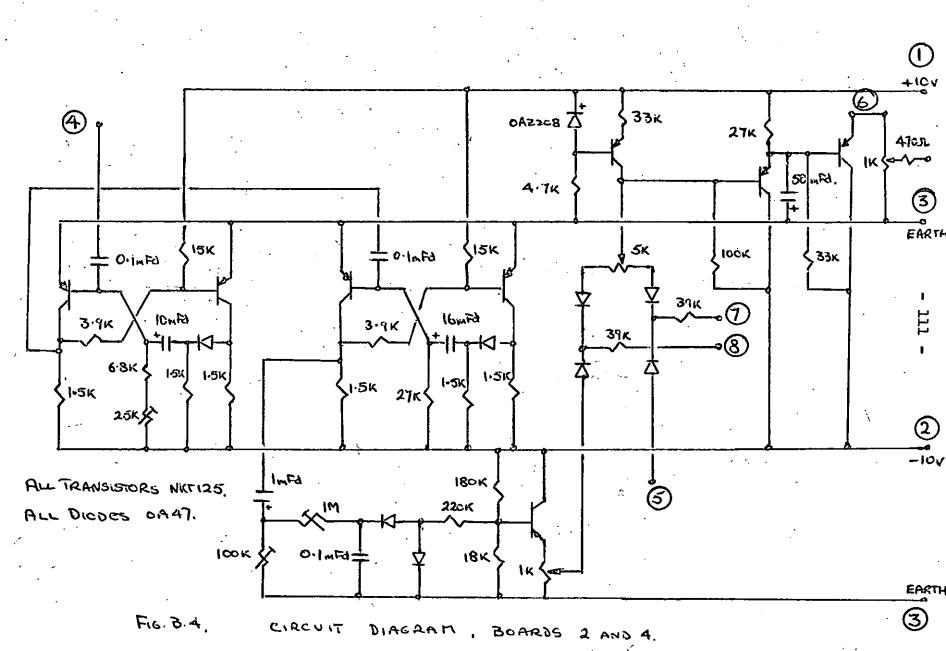

| Appendi                                 | x A | Computer construction and Circuit diagrams             | 92          |

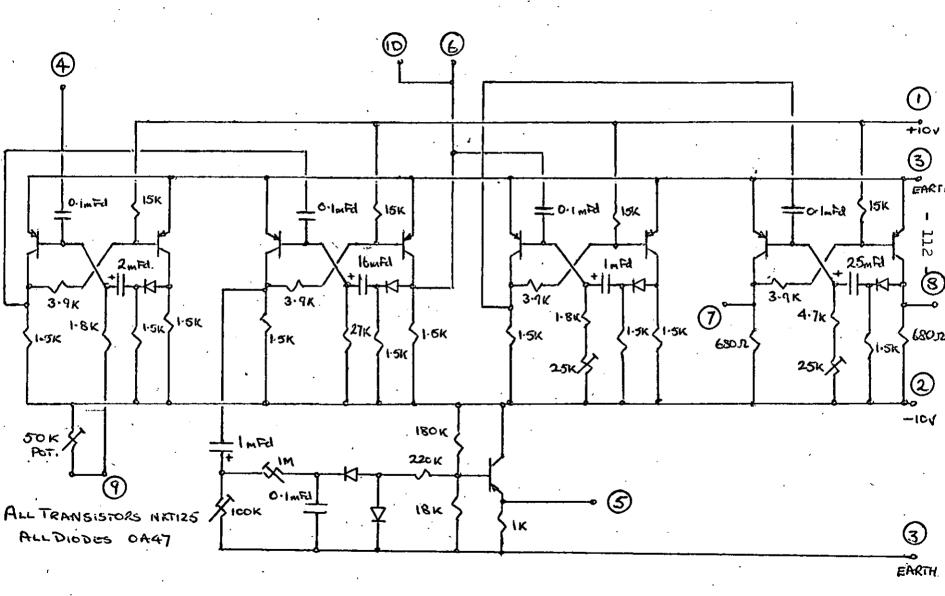

| 11                                      | В   | Simulator Construction and Circuit diagrams            | <b>1</b> 05 |

| 11                                      | C   | Current/Voltage Relationship for a Semiconductor Diode | 113         |

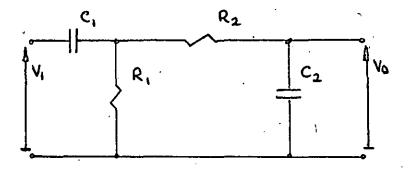

| tt                                      | D   | The Shaping Network for the Simulator                  | 114         |

| * · · · · · · · · · · · · · · · · · · · | E   | Fourier Analysis                                       | 117         |

| Section                                 | . 8 | References and Bibliography                            | 119         |

.

·

## List of Symbols and Abbreviations

Amplitude

Capacitor X

Delay

Diff. Differentiator

$D_{\mathbf{x}}$  Diode X

E.F. Emitter Follower

Exp.Amp. Exponential Amplifier

f<sub>k</sub> Pulse Wave Ordinate (Fourier Analysis)

Gen. Generator

h<sub>FE</sub> Transistor current gain at dc. Common Emitter.

Int. Integrator

I Current X

k Boltzmann's Constant.

P.G. Pulse Generator

q Electron charge

RVX Potentiometer X

Resistor X

S.C. Shaping Circuit

SD " " , Differential Control.

SI " Integral Control.

S/D Switch Delay

S/G Switch Generator

T Absolute Temperature

$T_{\mathbf{x}}$  Time period X.

V<sub>BE</sub> Transistor, Base: Emitter Voltage.

${

m V}_{

m CE}$  , Collector: Emitter Voltage.

VTX Transistor X

V Voltage X

Z Impedance Z

AGC Automatic Gain Control

ECG Electrocardiograph

PRF Pulse repetition frequency

PWV Pulse Wave Velocity

I/P Input

O/P Output

#### **ACKNOWLEDGEMENTS**

I wish to express my sincere thanks to Dr. J.M. Ivison, my supervisor, for the many interesting discussions we have held during this work and the help he has given me in preparing this report. Also, Mr. M. Wright, for his services in constructing the devices, in their present form; and to many other members of the University's Academic and Technical Staff for their guidance and assistance.

Last, but not least, I wish to thank my wife

Mrs. S.M. Wheaton, for converting my humble script into its

present form.

#### SECTION 1

### Introduction and Summary of Earlier Works

Before one can attempt to measure the velocity of the phenomenonknown as the arterial pulse wave, one must consider the physiological 'mechanism' which produces this wave.

In addition one must justify that the measurement of this parameter will be of some value.

Considering the latter point first, it is common, in an engineering environment, to express the 'performance' or 'reactions' of a device, circuit or system as a set of parameters. For example one can specify the performance of an amplifier circuit in terms of its bandwidth, gain, and input and output impedances.

However in dealing with a physiological system, the full data is generally complex and not easily measurable. Thus medical science has been built up on those parameters which lend themselves being measured with comparative ease. Blood pressure cam be included in this category, since its measurement can easily be effected with the aid of an occluding bandage or cuff, and a simple manometer. Blood pressure can be used, in conjunction with other information, to diagnose various illnesses and deficiencies occurring in the body. But is it necessarily the most useful parameter to measure? Would a knowledge of the "pulse wave velocity" be a more useful factor in determining the state of the arterial system? Questions

such as these do not as yet appear to have an answer, so only time and further work can give it. However, the parameter known as "Pulse Wave Velocity" may be of value, either alone or in conjunction with blood pressure, provided that it can be measured easily and accurately.

Before extending this argument, or considering any previous work in the field, an understanding of the circulatory system and the production of the pulse wave is required.

The circulation is divided into the three categories:i) Pulmonary ii) Systemic iii) Portal.

The pulmonary circulation is for the reoxygenation of the blood, which is pumped to the lungs via the pulmonary artery from the right ventricle of the heart. The venous return from the lungs is fed into the left antrium via the pulmonary veins, this is the complete pulmonary circulation.

The systemic and portal circulations are both derived from the left ventricle, and are the circulation of the blood round the body. The systemic circulation feeds the body tissues, whereas the portal circulation feeds the digestive system and liver. Both are derived from the Aorta and the venous return is via the Venae Cavae into the right antrium.

Heart action is controlled by a small bunch of nerves and muscles located in the right antrium, to which the venous return from the body comes. The nerve cells act a pacemaker for the heart and are called the sino-antral node. They also give rise to the electrical signal known as the electrocardiograph. The normal rate of excitation is approximately 72 beats per minute, in an adult. Each period of contraction is followed by a period of rest of approx imately the same duration.

The contracting period is known as the systole and the rest period as the diastole, each being approximately 400 msec long. The complete action is referred to as the cardiac cycle. The systole is subdivided into two parts, the atrial systole and the ventricular systole. The atrial systole is of a short duration and consists of a contraction wave sweeping over both atria and forcing the blood there into the ventricles, through the tricuspid and mitral valves. The ventricular systole commences as soon as the pressure in the ventria exceeds that in the atria. The valves shut and blood is forced into the aorta and pulmonary artery. The process ends when the pressures in the ventria are equal to those in the aorta and pulmonary artery.

The rest period or diastole now commences and blood pours into the ventria from the atria, and also into the atria from their own sources. This again continues until equal pressures are produced. The pacemaker then fires again and the .

cardiac cycle is repeated.

The 'pulse' is created by the alteration in tension of the walls of the arteries due to blood being pumped through them in spasmodic bursts. Its propagation over the arterial system thus takes the form of a pressure wave, which travels along the arterial walls. Obviously like any other wave propagation, the pulse wave becomes attenuated, delayed and distorted by reflections.

during systole is referred to as the Systolic pressure and the value maintained during diastole is the diastolic pressure.

The systolic pressure is produced by the pumping action of the heart, whereas the diastolic level is maintained by the contraction of the arteries, which is observed as the pulse wave.

In this work, the measurement of the pulse wave velocity will only be considered with reference to the principal systemic arteries; since these can be located easily and the pulse wave can be monitored with suitably designed transducers, through the relatively thin layers of surface tissue. Thus no surgical intervention, which could interfere with the physiological processes is necessary. The 'transducer pickups' and their design and performance are to be discussed in detail in Section 5.

A survey of previous work in the field follows.

Basically the work can be divided into three categories:

- Analytical relationships between pulse wave velocity and blood pressure.

- 2) The clinical aspects of pulse wave velocity.

- 3) Methods of measuring pulse wave velocity and blood pressure.

Considering the category 1) it appears that the first consideration was by Moens in 1878, when he stated that the pulse wave velocity, v, could be expressed as:-

$$\mathbf{v} = \mathbf{F} \left[ \frac{\mathbf{E} \cdot \mathbf{e}}{2 \rho \mathbf{r}} \right]^{\frac{1}{2}}$$

Where E = Young's Modulus

r = Internal Radius of the tube

e\_= Wall thickness

F = Constant found <math> 0.8 in man.

$\rho$  = Density of Blood  $\simeq$  1.055

The expression as it stands has too many unknown factors and thus it was shown by Bramwell and Hill (1), that we can express the term  $\begin{bmatrix} 2r \\ E & e_0 \end{bmatrix}$  in terms of a volume modulus as  $\frac{1}{V} \cdot \frac{\lambda V}{\delta \rho}$ .

This simplifies the expression to the one given below:-

P.W.V. = v = 3.57/(% Increase in Volume per mm Hg increase in pressure)  $\frac{1}{2}$

The above expression was accepted as approximate, but usable by most authors until much later when King, (12), takes into account changing wall thickness and other factors and expresses

the pulse wave velocity as,

$$v^{2} = \frac{A}{4\rho} \left[ \left( \frac{2Br'}{r_{c}} - 1 \right) \left\{ \frac{P' - P_{c}}{A} + \left( \frac{\Gamma_{c}}{r'} \right)^{3/2} \right\} + 3 \left( \frac{\Gamma_{c}}{\Gamma'} \right)^{3/2} \right]$$

Where A =  $e_0 \rho / 2r_0$

$$B = \beta u^{1} \sinh^{2} u^{1} / (\sinh^{2} u' - (u')^{2})$$

and u is defined by:-

$$\coth u' = \frac{1}{u'} + \frac{\beta r'}{r_0}$$

In these relationships  $\beta$  is an age dependant constant, characterising the elastomeric wall, which is the ratio of circumference of the tube to the maximal length of the molecular chain. The 'o' suffix refers to the dimensions considered when the pressure is zero, and 'symbols refer to the values when the pressure is p. He defined mean blood pressure as the mean value of the systolic and diastolic values. The above relationship gives increased velocity with increase in the pressure or age as found in practice.

In his report he plots sets of curves given by the above expression, of pulse wave velocity to pressure and age. After this period certain texts have chapters devoted to the subject. (19), (26), (30). In the most recent of these the author is Hardung (30), whose treatment of the subject is thorough, but too long to condense into this report. He, like King, derives the Moens expression and extends the work to take into account factors not previously considered.

The true analytical relationship between pulse wave velocity and blood pressure is complex, and thus many of the early workers ignored this relationship and concentrated on a more clinical study.

Bramwell and Hill (2), studied the relationship of PWV to age on excised arteries and found that the velocity increased with age. Bramwell, Downing and Hill (3), noted that an S shaped curve was obtained for PWV with respect to pressure, which was fairly linear over the normal range of blood pressures. Also that the shape of this curve was related to age. Bramwell, McDowall and McSwiney (4), studied the effect of varying pressure on the PWV in living subjects by applying a syphygmomanometer bandage around the patient's arm, and varying the pressure in this manner. The PWV was measured, directly as a time delay. The results, they obtained, suggested a linear relationship with pressure. This work was verified by Hemingway, McSwiney and Allison (7).

Hickson and McSwiney, again working with living subjects measured the pulse wave velocity over approximately 50 cm. of brachial artery, by direct time measurement, and compared their results with the blood pressure.

The previous investigators accepted the modified Moens equation relating PWV to blood pressure and found that in certain circumstances it could be applied.

A good summary paper of work up to this stage is that by Hallock (8), who lists the findings of most of the previous authors.

Dow and Hamilton appear to be some of the earliest workers to attempt to verify Moens modified equation, and in their studies of PWV in dogs, found that the velocity varied with the distance from the aorta. They were however, able to account for the variations in terms of the change in elasticity of the arteries concerned. They also made a comparison between diastolic pressure and PWV.

Porje's (11), is a later report (1946) which summarizes eadier papers in some detail. He, experimentally, has taken - a sample of 58 healthy persons and examined their pulse waves with the aid of Fourier Analysis. The system he used was that of a piezo-electric pulse microphone coupled to an ECG am plifier/recorder. He takes his studies into some detail but a brief summary of his conclusions is given. The waveform itself is almost completely defined by the fundamental, second and third harmonies, of which the fundamental is the strongest. It consists of both initial and reflected components, and the reflected wave consists basically of the fundamental frequency. The higher harmonics present are transmitted, virtually without reflections, and the velocity of all components increases with the age of the artery. For interest, he also studied a number of pathological cases. In several cases he noted various differences in the waveforms. These included a more dominant fundamental component.

The reflected waves were increased, and the second harmonic was also reflected. The overall wave velocity was increased.

This report is of some value in that he gives typical pulse curves and also details of his pulse microphone, including a frequency response. He also appears to have been the first to analyse his waveforms by Fourier analysis.

However after this point little interest appears to be shown in PWV as a clinical parameter until Weltmann (21) produced what appears to be one of the first continuous pulse wave velocity monitoring devices. In his report he includes the action of the pulse wave under certain conditions, of stress etc. PWV measurement as a replacement for blood pressure is considered unsuitable at the moment by Webb Associates, (28),(31), due to the inaccuracies in the measuring systems, and hence this is sufficient licence for this work to be started.

The measurement of pulse wave velocity is a relatively simple process which consists of merely timing a pulse along a known length of artery. From these figures one can then easily compute the velocity. The early researchers, in general, used Not wire sphygmographs in conjunction with Einthoven galvanometers. The recordings were compared and the delay computed. However to obtain reasonable results large delays were required and hence the measurement of the arterial path became another problem. Porjé (11) used a similar method with his pulse microphone pickups. However for continuous recordings Weltmann, (and Sullivan), (21), (29),

and Salisbury and Wickham (27), appear to be the sole contributors to the field.

In the field of automatic blood pressure recording significantly more work appears to have been done, Gilson (10), Noble (13), Landsman (14), Green (16), Cooper and Richardson (22), Webb Associates (28),(31), ITT Federal Laboratories (33), Thompson (34), Van Bergen (35). The above is merely a selection of the references which are available. The basic technique is that described by Gilson (10), and uses an occluding cuff. However Van Bergen (35) estimates that this kind of measurement is subject to errors of 25%, or more. Thus production of a device which can measure pulse wave velocity, automatically, to a higher accuracy, could well have some useful applications.

Reviewing the measurement techniques adopted previously shows that Weltmann (21), computes the pulse wave velocity, by measuring the delay between the ECG and the pulse recorded at some peripheral artery. He defines this as:-

PWV = L/I\*

Where L = Arterial length between the aortic arch and the peripheral pulse transducer.

I\* = Time interval between pulse expulsion from the heart

and pulse arrival at the peripheral transducer.

I\* = I - 40 msec.

Where I = Actual time period measured which he states is that intervening between detection of the 'R' wave of the ECG complex

and detection of the leading edge of the arteral pulse.

To present this information in terms of a velocity, he utilises the time interval to produce a proportionate analogue voltage, which is fed into an analogue, division circuit, with another analogue voltage representing the length of artery 'L'. The solution is then fed to a suitable recording device.

Consideration of his approach shows that the computation of the velocity from the time measurement is best achieved with an anlogue circuit, since this produces sufficiently accurate results (1%) with the minimum of components. However as to the actual quantities used, there is some doubt as to whether his figures for PWV are entirely relevant to the case being considered here. The actual length of artery car only be estimated, and in addition the dimensions and constants for the artery are continually changing along its length. Thus, even if one accepts that the method of measurement is justified, the value obtained for the PWV can only be a 'mean' figure.

The object of this work is to measure the velocity over a shorter piece of artery, and so correspondingly the time measured will be proportionately shorter, and hence must be measured more accurately.

One can assume a typical figure of 5 msec for PWV (Porjé) (11), and a period of 800 msec, thus in one pulse period the pulse will travel, 4 m, which is some considerable distance. A typical length of artery which we can measure to a suitable accuracy

(2%) would be 10 cm, from which a delay of 20 msec would be obtained. This is extremely small when compared with its 800 msec period, and thus the real crux of the measurement problem appears. Also one must bear in mind that one cannot rely upon the waveform to be propagated without changing its shape, nor upon its amplitude remaining constant over a period of time. Thus, despite these difficulties a suitable solution has to be found.

Salisbury and Wickmann (27) have designed a system which overcomes these troubles by superimposing a sharp edge on the trailing edge of the pulse wave, and then detecting this edge at a known distance away, with a suitable pick-up. The edge is superimposed on the pulse waveform by a small pneumatic device mounted above the artery. The delay time is taken as that from when the pulse is injected to its detection after propagation.

This method offers a solution to the measurement of the small delay involved, but in doing so interferes with the physiological system. And thus until proven, otherwise, it must be assumed that this will affect the velocity of propagation. Hence one cannot at present take the results as reliable, and so the problem still remains of how to measure a time, of the order of 20 msec, as a delay to an ill-defined waveform of period 800 msec, to an accuracy of say 1%

### SECTION 2

### The Proposed System

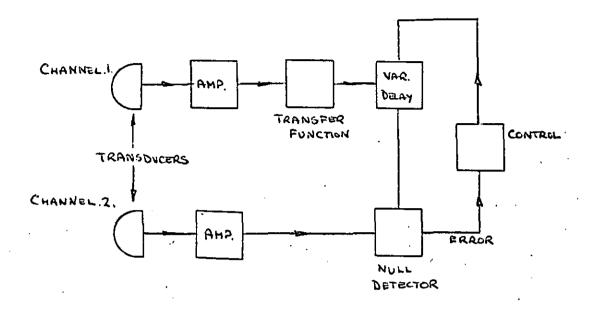

In the previous section the problem has been stated and previous work in the field has been surveyed. From this the conclusion is that the crux of the problem is to measure a delay of the order of 20 msec in an ill-shapen waveform of 800 msec period. The waveform, which presents itself as a pressure wave in the arterial walls, must also be monitored with suitably designed transducers.

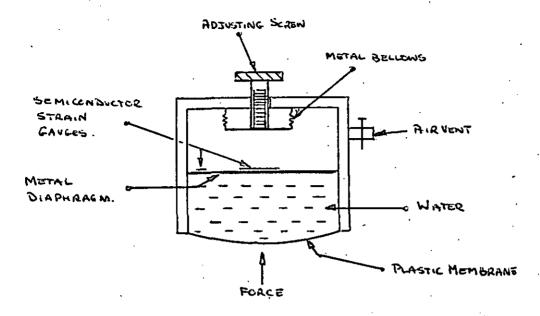

Thus the first consideration is that of a suitable transducer to convert this pressure wave into an electrical signal. Such a device is described by Davies et al (32), in a recent paper. They indicate that faithful recordings of the pulse wave can be obtained with a device of the kind they are using. The transducer to be used here, is of a similar design to that used by Davies, and its development will be discussed in Section 5. It was considered that the scope of this project was already sufficient and the development of the transducer would be undertaken as a separate exercise. To enable the system to be developed without a transducer it was decided to make a 'Simulator', which would produce an electrical signal similar to that delivered by the transducers. The detailed requirements and design of this Simulator are discussed in Section 3.

The method of measurement of pulse wave velocity here will be to monitor the delay over a known length of artery, and from this compute the velocity at which the wave is travelling. Thus for ease of description it will help to divide the work into various sub-sections.

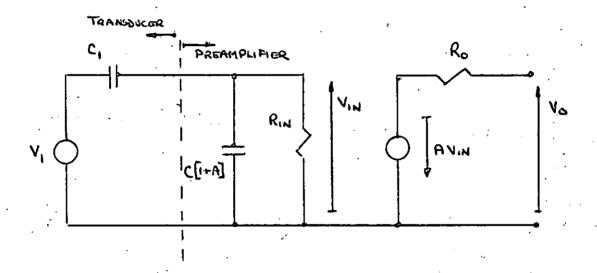

The transducer will require some form of pre-amplifier to isolate it from the main system. The pre-amplifier design is governed by the characteristics of the transducer and will be considered in Section 5, with the transducer.

In addition a gain-controlled stage will be required to enable the signal obtained from the transducer to be of a constant output amplitude, and independent of the operating conditions.

Following these initial stages, the main system can be considered. The first function required is to measure the time delay between the two waveforms. This delay must also be presented in a suitable form to drive the division system which follows it. An analogue system can achieve the accuracy required (1%), with the minimum of expense. Here, as with previous authors, the delay is translated into an analogue voltage by the delay measuring system. Thus, the division system also becomes an analogue device. The two inputs to the division system are the time delay and the arterial length used. The arterial length can be supplied from a previously calibrated voltage source.

After obtaining the output from the division system, that is, the pulse wave velocity, it must be displayed in a suitable manner.

The salient features of the system are now discussed.

Section 2.1

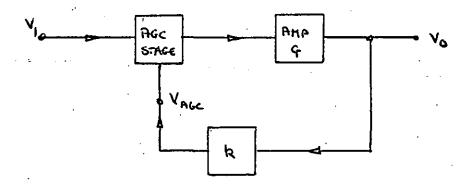

## Gain Control

The various methods of gain control, and the system selected are discussed in Section 4. The purpose of this stage is to enable a constant output signal to be provided from the transducers. This apparatus is intended for general application and the design of the system should allow for a maximum variation of the input signal.

A Gain control system, can, in general, be made to respond to either the mean or peak values, of the input signal. Here, for reasons that will become obvious, a system has been selected that responds to the peak value.

### Section 2.2

#### Delay Measurement

Assuming that the signals supplied by the gain control amplifiers differ only in phase, and are of a constant amplitude, then a number of measuring techniques are available.

A possible method would be to define a point on each waveform by its dc level, and then use a level sensitive detector, such as a Schmitt trigger circuit, to produce a pulse edge at this instant in time. However, the resolution obtainable in this way is low, since the edges of the signal are extremely slow.

|     |            | ' |

|-----|------------|---|

|     | •          | 1 |

|     |            |   |

|     | ·          | 1 |

|     | •          |   |

|     | •          | 1 |

|     | •          |   |

| •   |            | I |

|     |            |   |

|     |            | I |

|     |            |   |

|     |            | ı |

|     |            |   |

|     |            |   |

|     |            | 1 |

|     |            |   |

|     |            | I |

| ·   | ·          |   |

| ,   |            | 1 |

|     |            |   |

|     |            |   |

|     |            | - |

|     |            |   |

|     |            | • |

|     |            |   |

|     |            |   |

|     |            |   |

| •   |            |   |

| •   | <b>-</b> • |   |

|     | <b>-</b> • |   |

|     |            |   |

| · - |            |   |

|     |            |   |

|     |            |   |

|     |            |   |

|     |            |   |

|     |            |   |

|     |            |   |

|     |            | • |

|     |            |   |

|     |            | • |

|     |            |   |

|     |            |   |

|     |            |   |

|     |            |   |

|     |            | • |

|     |            |   |

|     |            |   |

|     |            |   |

|     |            |   |

|     |            |   |

|     |            |   |

A technique based on the Lissajou figures, could be used to measure the phase difference of the fundamental components of the two signals. The frequency of this component may, however, change by a factor of 3 in a healthy subject and active filters would be required. This is a problem that could be solved, but still remains the problem of the high resolution required.

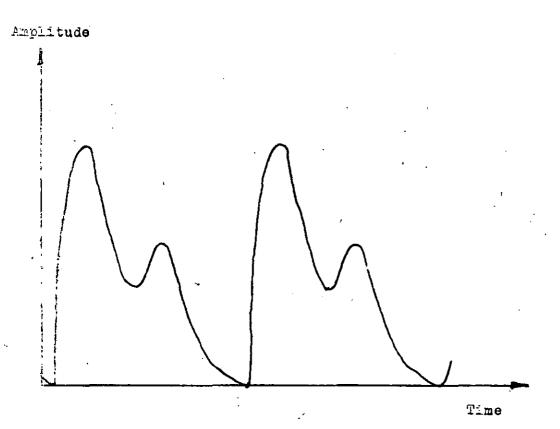

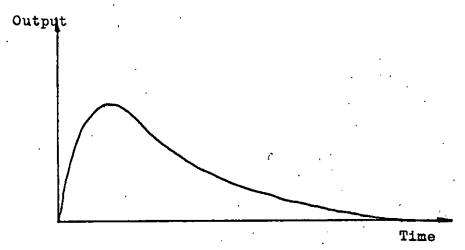

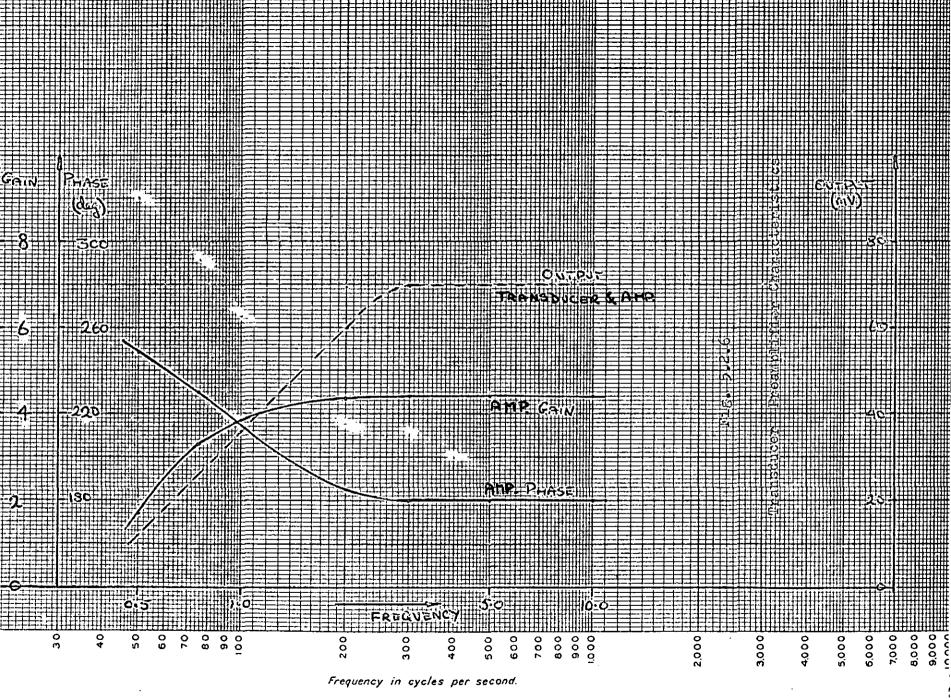

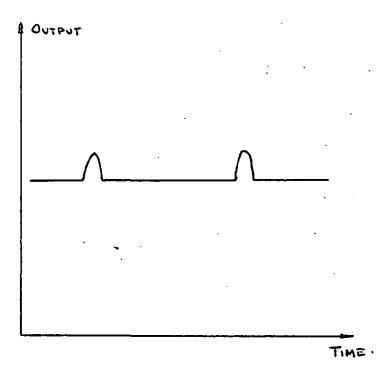

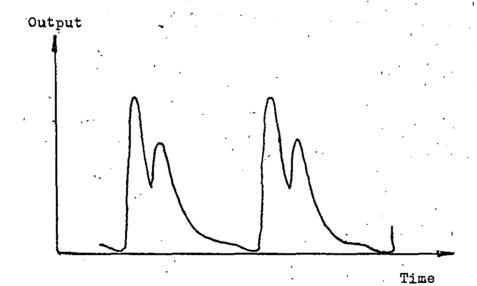

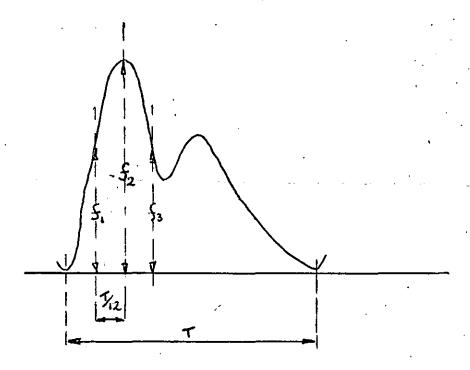

Here a novel approach has been considered, and a suitable system built round it. If one assumes that the length of artery is small and of a uniform nature, then apart from the phase shift the signal at either end will be the same. This being so the phase shift could be defined as the delay between the two peak values. (A typical pulse waveform is shown in fig. 2.2.1.). The peak value is a significant point which occurs in all pulse waves, and thus, this definition would be valid for all cases.

To measure the delay between the two pulse peaks the signal is 'processed' by amplifying it exponentially. That is with an amplifier with a characteristic of the form:-

$$V_o = A \exp(BV_1)$$

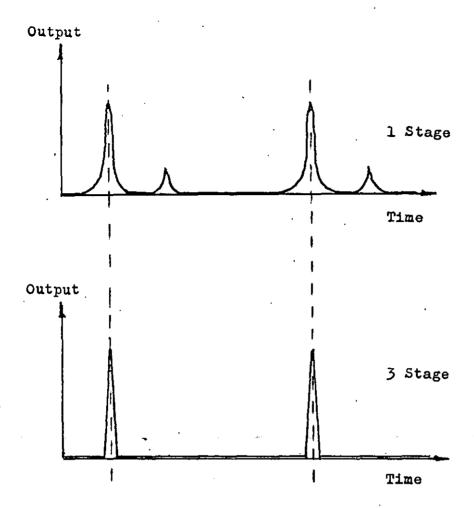

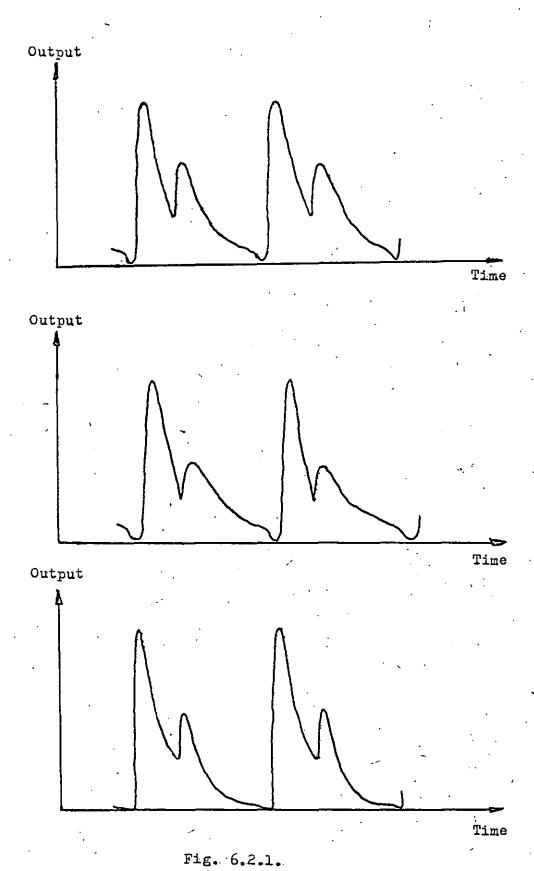

This kind of amplification selectively amplifies the peak value of the signal and in doing so 'sharpens' it. The effect on the waveform is shown in fig. 2.2.2. and obviously as many stages as required cam be used. There is, however, the

|      |   |       |   |     | • |          |

|------|---|-------|---|-----|---|----------|

|      |   |       |   |     |   |          |

|      |   |       |   |     |   |          |

|      |   |       |   |     |   |          |

|      |   |       | • |     | • |          |

| •    |   |       |   |     |   |          |

|      |   |       |   |     |   |          |

| •    |   |       |   |     |   |          |

|      |   |       |   |     |   |          |

|      |   |       |   |     |   |          |

|      |   |       |   |     |   |          |

|      |   |       |   |     |   |          |

| .*   | * | <br>ø |   | ÷ . |   | ~        |

| .,   |   |       |   |     |   | <i>"</i> |

|      | * |       |   |     |   | u.       |

|      |   |       |   |     |   | *        |

| ., . |   |       |   |     |   |          |

|      |   | •     |   |     |   |          |

|      |   | •     |   |     |   |          |

|      |   | •     |   |     |   |          |

|      |   | •     |   |     |   |          |

|      |   | •     |   |     |   |          |

| •    |   | •     |   |     |   |          |

requirement that the agc stage goes 'hand in hand' with this amplification since too large or small an input signal will result in an overloaded or zero output.

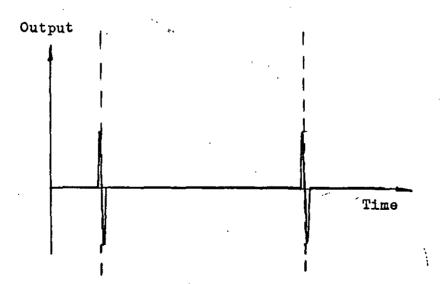

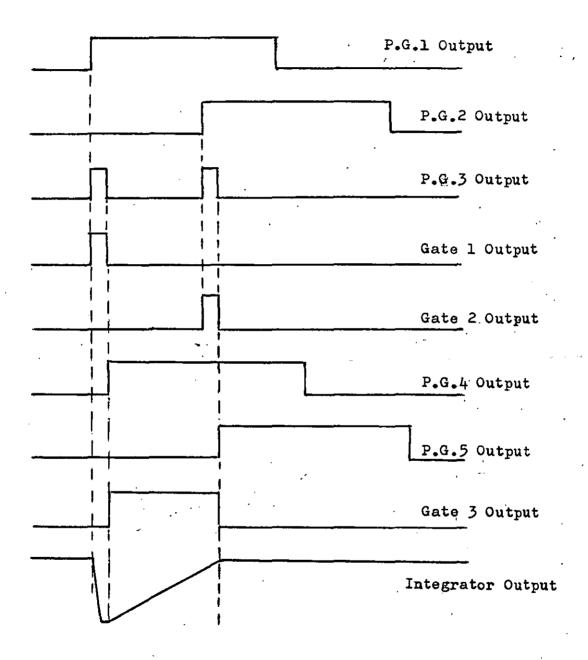

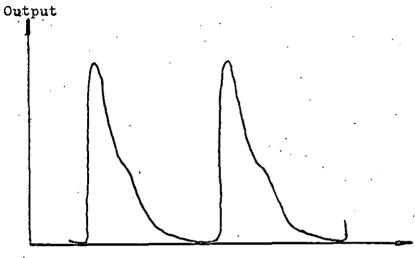

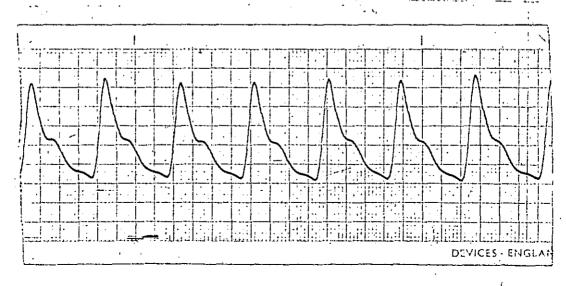

Exponential amplification does not remove any information from the signal since the original can be reconstituted by logarithmic re-amplification. Thus, providing the gain control is effective, then this system will perform the task required. In order to define the time at which the peak occurs, the signal is differentiated as shown in fig. 2.2.3. and gives a fast negative going edge coincident with the peak. This edge is used to trigger a pulse generator and produce a pulse of finite length, the leading edge of which defines the time at which the peak occurs.

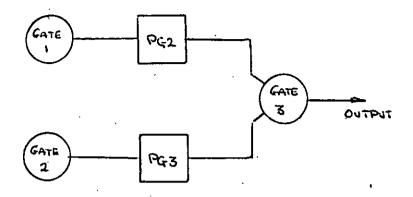

To measure the delay this pulse is applied to a gating circuit together with the signal from the second channel.

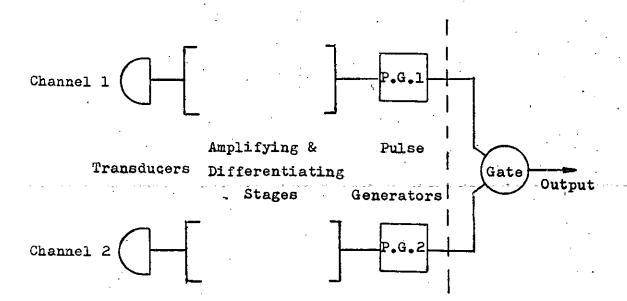

The output of the gate is a pulse, the length of which is the measured delay. This system is shown in fig. 2.2.4.

It is necessary to present the output in analogue form, which will require that the pulse is integrated. As continuous operation is required, a time period, and trigger signal, with which to reset the integrator are required. This period is produced by delaying the front edge of each of the pulses by the same amount. This delay period can

Fig. 2.2.1.

Typical Pulse Wave

Fig. 2.2.2. Exponentially Amplified Pulse Waves

Fig. 2.2.3. Differential of Above Signal.

Fig. 2.2.4

Proposed System

## Integrator Reset Signal

Fig. 2.2.5

Modification to Provide for an Integrator Resetting Signal

Fig. 2.2.6

Integrator Configuration

Fig. 2.2.7

Theoretical Waveforms Related to the Delay Measuring System (as shown in fig. 2.2.4 - 2.2.6)

Actual Delay Measuring System

Fig. 2.2.9

Fig. 2.2.9 (Contd.)

Actual Waveforms for the Delay Measuring System.

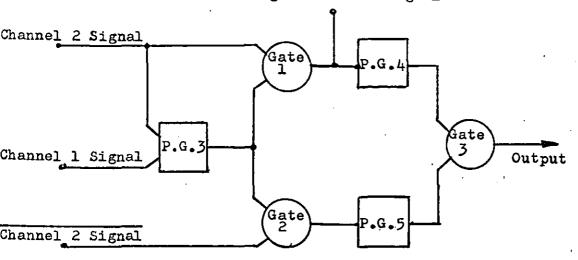

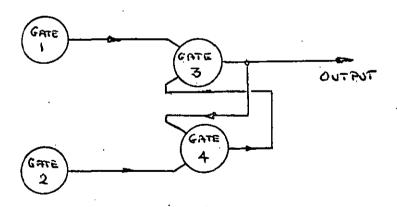

then be used to reset the integrator. To perform this function the system as shown in fig. 2.2.5., is used. The original pulses are both fed into PG3 as shown. This generator produces a short delay pulse from each leading edge, these delay pulses are then routed back to their original channels by the logic shown. From the rear edge of these delay pulses further pulse generators are triggered to give the original signals in their delayed forms. The integrator reset drive is the channel 1 delay pulse, as shown. Waveforms relating to this figure, and to fig. 2.2.6, are shown in fig. 2.2.7. However, these waveforms may not apply directly to the real system since they are all assumed positive. The real system is discussed in Section 2.2.1.

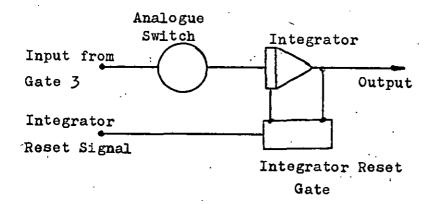

The integrator is shown in fig. 2.2.6, and in addition to translating the pulse into an analogue signal, it serves as an analogue storage element for the system.

# Section 2.2.1

# The Actual Delay Measuring System

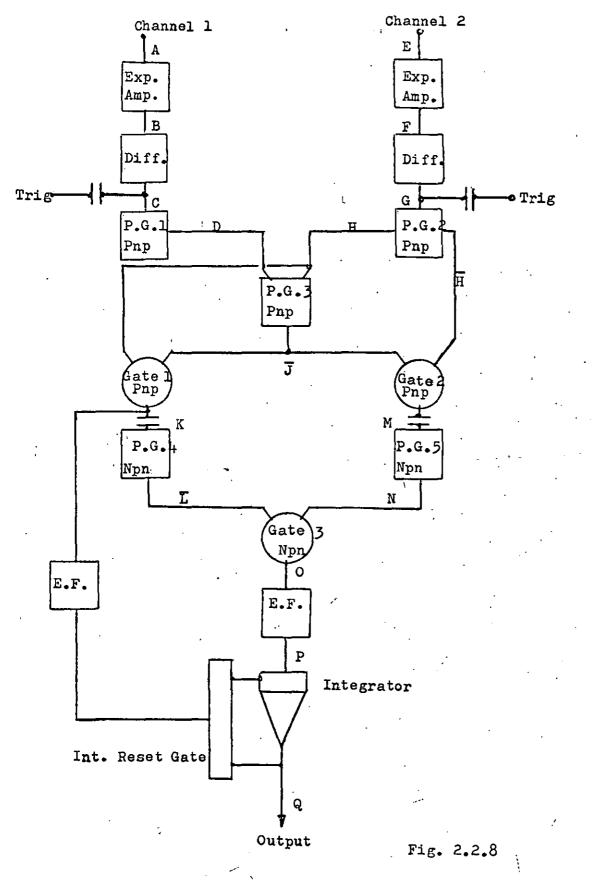

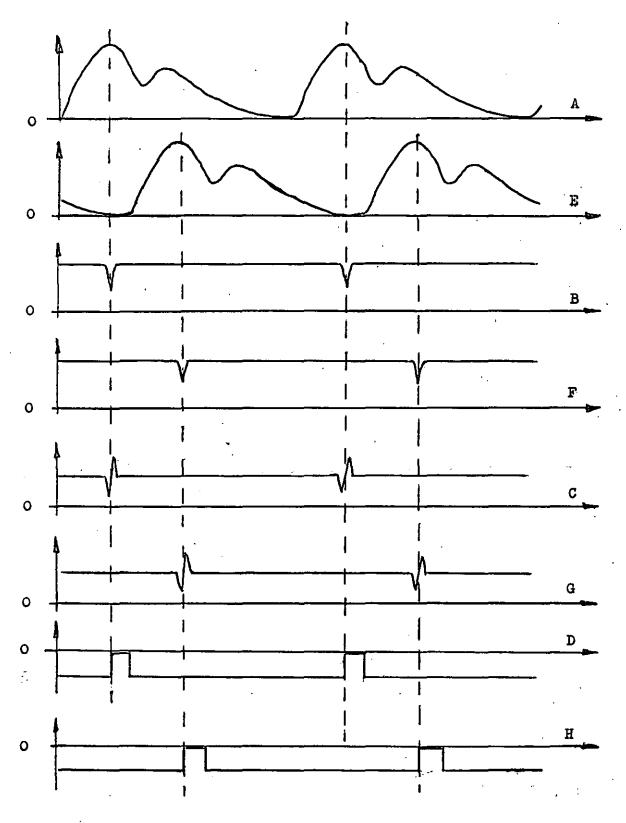

The actual system used for the delay measurement is shown in fig. 2.2.8, and the waveforms related to this system are shown in fig. 2.2.9. The input to both channels is required to be positive since simple exponential amplifiers have been used and they will only function for a single polarity input.

A three stage exponential amplifier is used to give the required definition to the system. The amplifier response cam be found in Section 4.

\$1

The differentiator consists of a single stage performing the differentiation, ac  $\infty$  upled to a voltage amplifying stage which is needed to give sufficient output to drive the pulse generator following it.

The pulse generator produces a 2msec pulse which is a positive going pulse, between negative and earth. An additional input capacitor is provided to this stage to enable the system to be run without using the exponential stages if required. The pulse wave simulator will have a facility provided so that it can also drive the system at this point, if required.

From these outputs a 0.2 msec pulse is generated by PG3, for each pulse. Diodes have had to be included on the inputs to PG3 to avoid feedback. From this pulse generator the inverse output is taken, that is a negative going pulse between earth and negative. This signal is then fed into gates 1 and 2, as shown. For the channel 1 'delay pulse', it is necessary to gate this signal with the previous channel 2 output in its normal form, since this signal will inhibit the gate when a channel 2 output is present. Thus for the channel 2 output the gating is with the inverse original channel 2 signal. From these 'delay pulses', a pulse is produced from the rear edges by pulse generators 4 & 5, of 200 msec duration.

These pulses are then combined in gate3to give a pulse, the duration of which is the required delay. This is achieved by gating the inverse channel 1 signal and the normal channel 2

signal. The inverse channel 1 signal inhibits the gate until the pulse is present, the channel two signal choses the gate on the front edge of the pulse. Thus the gate output signal is of the required duration. This signal consists of a negative going pulse between positive and earth. This is then fed via a zener diode voltage shifting network into an emitter follower to provide a suitable low source impedance for the integrator.

The output is fed into the integrator via a silicon diode. The purpose of this diode is to avoid the necessity of setting the quiescent state of the output pulse to earth potential, since only that portion of the output negative with respect to earth will be transmitted. This facility is particularly important since the integrator also stores the delay as an analogue voltage, and slight discrepancies of the quiescent levels would cause the output to either continue rising slightly or to fall slightly, over the storage period. Using a diode, prevents this by ensuring that the diode is cut-off in the quiescent state; thus giving only its leakage current as an error input. For silicon devices the leakage is extremely small.

The integrator itself has been 'patched' to a gain of 20, as will be discussed later in this Section. The integrating capacitors are of a polystyrene type, which are suitable for this application, due to their low leakage characteristics.

Silicon transistors, which have low leakage characteristics, are used in the reset circuit. The drive to the reset gate

Pulse Width Analogue Division System

Fig. 2.3.2.

Waveforms Related to the System as shown in Fig. 2.3.1.

is fed via an emitter follower, to avoid loading the gate from which the signal is derived.

### Section 2.3

### Analogue Division

Analogue division cam be accomplished by a number of standard techniques. However, in this case a single quadrant system will be sufficient. With this in mind a possible approach using logarithmic and exponential amplifiers was considered, similar to the system described by Cowell et al (48). This was rejected since the accuracy is solely dependent upon the manner in which the functions are generated. The simple approach using the non-linear characteristics of a junction diode has the disadvantage that the expression is dependent on temperature, (see Appendix C), and hence fluctuations in the temperature would affect the accuracy in a random manner. A second disadvantage is the large number of operational amplifiers that the system requires.

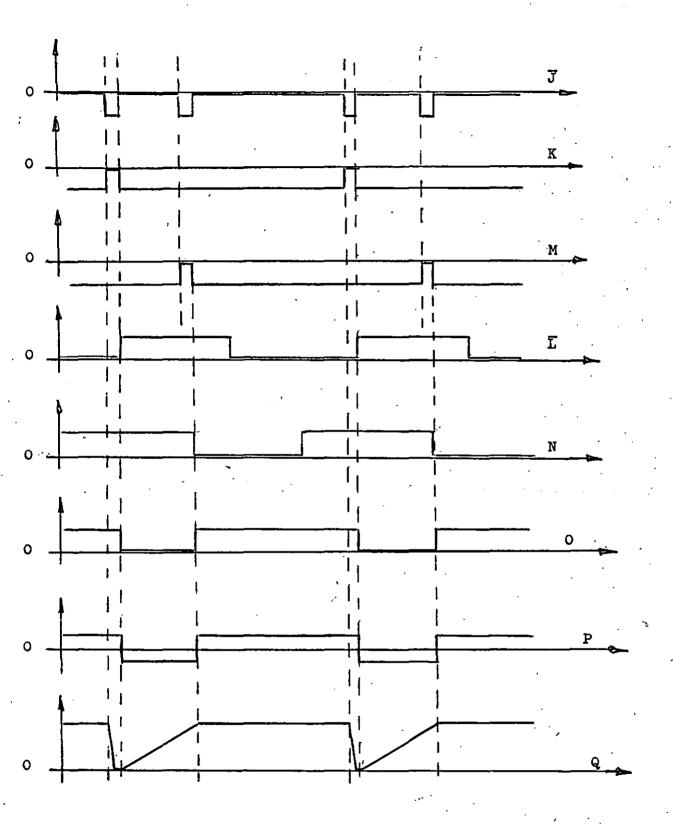

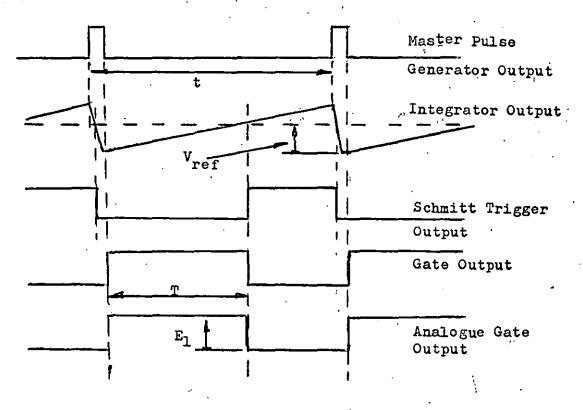

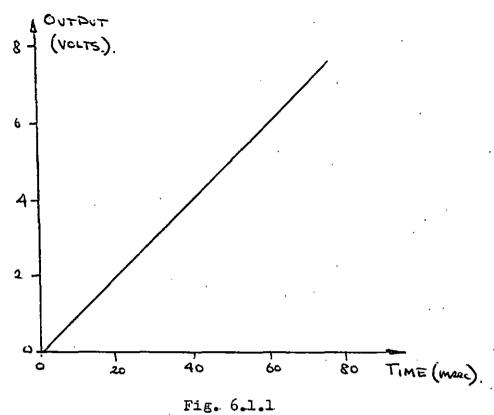

The system adopted, uses a pulse width technique, and the accuracy is dependent on the linearity of an integrator. The basic system is shown in fig. 2.3.1, and the related waveforms in fig. 2.3.2. Again all the waveforms are assumed positive.

The operation is as follows; an analogue voltage  $E_2$ , is fed into an integrator with an overall gain of A. After time period T, the integrator output will be given by,  $V_0 = E_2$  A.T.

When this integrator output exceeds a value of  $V_0 = V_{REF}$ , which is set by the Schmitt trigger circuit, this circuit changes its state, as shown in fig. 2.3.2, and in doing so inhibits the gate, which had been previously opened at the initiation of the integration, by the master generator. Thus for this condition one obtains:-

$$V_o = V_{REF} = E_2A.T.$$

Thus  $T = V_{REF}/AE_2$

To complete the cycle the master generator resets the integrator, via the resetting gate, and the reset integrator output resets the Schmitt trigger circuit. The master generator then inhibits the integrator's operation until the start of the next cycle. The process is then repeated at a high repetition rate.

The signal from the gate is used to switch am analogue gate on for period T, as shown. The dc component of the analogue gate output is given by:-

$$Vdc = \frac{E_1}{t} = \frac{E_1}{t} \frac{V_{REF}}{E_2 A} = k \left[ \frac{E_1}{E_2} \right]$$

$$Where K = \left[ \frac{V_{REF}}{A t} \right]$$

The dc component of this signal can be obtained by passing the signal through a low-pass filter as shown. As can be seen this dc voltage is directly proportional to the quotient  $(E_1/E_2)$ , also the constant of proportionality is known =  $(V_{REF}/At)$

Fig. 2.3.3.

Actual Analogue Division System

Thus an analogue division has been performed, without using non-linear characteristics, upon which the accuracy is dependant.

The accuracy here is dependent upon linear operation of the integrator, stability of the reference voltage set by the Schmitt trigger circuit, and compensation for the saturation voltage of the analogue switch.

## Section 2.3.1

### The Analogue Division System

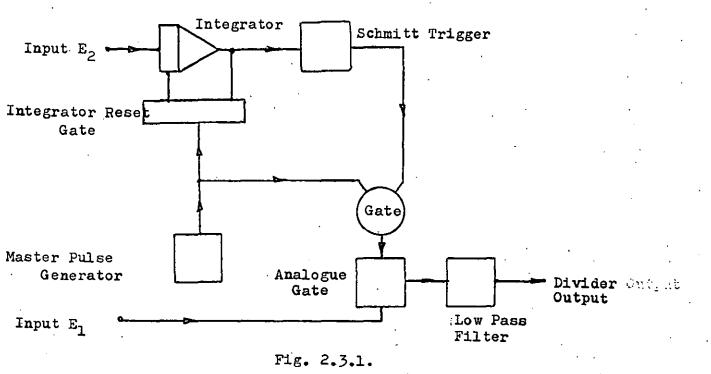

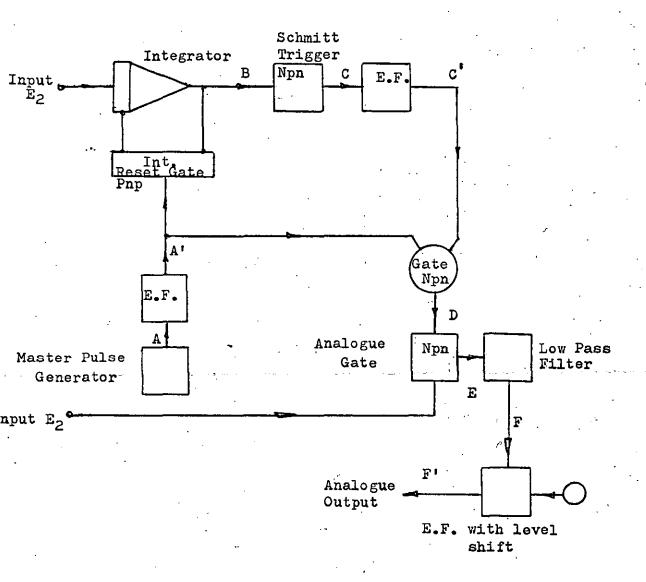

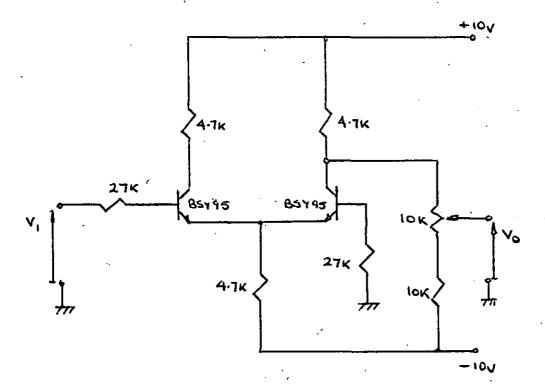

The system used for the analogue division is shown in fig. 2.3.3. As cam be seen the system remains as before apart from the addition of several 'emitter follower' stages.

The input E<sub>2</sub> is from the delay measuring integrator and is a positive voltage. The inversion in the integrator produces a negative ramp. This ramp feeds into a Schmitt trigger circuit which consists of two npn transistors. The reference level of this circuit is set to approximately -4 volts, and when the ramp exceeds this level, in a negative sense, the device changes its state. The output is a negative going pulse edge from +10 volts to earth. This edge is used to close an npn gate, as shown, which was previously opened by the master generator. This generator is an astable pulse generator using two pnp transistors and operating between +10 volts and earth. The mark:space ratio is approximately 6:1 with an overall prf of 7 kc/sec.

Fig. 2.3.4.

Waveforms Related to Fig. 2.3.3.

The large mark: space ratio is used for two reasons.

- i) Only a short period is required in which to discharge the integrator.

- ii) The accuracy of the system is directly related to this ratio.

The master generator also drives the integrator reset circuit, consisting of two pnp germanium transistors. The integrator has been 'patched' to a gain of approximately 50,000. This high gain is required for the system to function correctly at the high repetition frequency.

The npn gate is followed by a similar gate, used as an analogue switch, to which the E<sub>1</sub> input, representing the arterial length, is taken. The switched analogue output is then fed into a low pass RC filter with a 3dB cut-off frequency at approximately 5 c/sec. The output then appears as a dc voltage and is fed via a high input impedance emitter follower, to the output voltmeter. This circuit has variable biasing, to enable the output level to be set as required.

The waveforms relating to this system are shown in fig. 2.3.4.

The results of tests performed on the system are given in

Section 6.

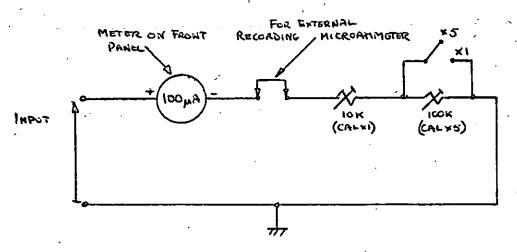

## Section 2.4

# Display facilities

With apparatus of this kind it is normal to display the results in analogue form on a roll of paper tape. In this case the display facilities are simple and consist of a moving

coil volt meter, mounted on the front of the apparatus which gives a direct reading of the divider output signal. To avoid loading the filter an emitter follower, with a variable bias facility is included as a buffer stage.

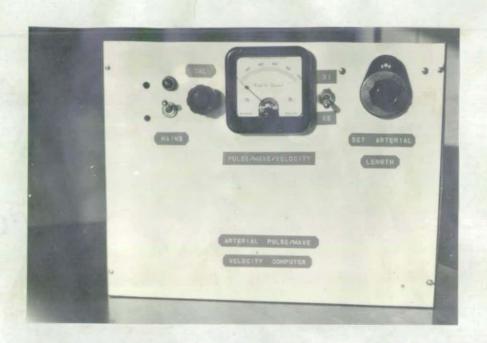

The voltmeter has two ranges so that the PWV can be read on a 0-10 m/sec or 0-50 m/sec scale.

A facility is provided for the addition of an external 100µA recording ammeter.

The calibration of the device, is described in the following section.

A circuit diagram is included in Appendix A.

## Section 2.5

## System Standardisation and Calibration.

In order that the individual units will function correctly when combined they must be compatible. The range of transducer output signals must be determined, and the required range of operation of the device in terms of arterial length and velocity must also be considered.

The change in transducer output affects only the requirements of the gain control system and will be discussed in Section 4.

The standard pulse wave velocity appears to be of the order of 5 m/sec,, the delay can be measured in the range 10 msec to 100 msec. At 'standard' velocity this would give distances of 5 cm to 50 cm, arterial length, which would seem acceptable dimensions.

Let the gain of the Delay Measuring Integrator be, A, and that of the Division Integrator, G. The input pulse to the delay measuring amplifier is approximately 5 volts. Thus for a time period of length t, the output from the delay measuring integrator will be;  $V_0 = 5$ At volts.

With the division integrator, the minimum input voltage required is set by the timing period, the gain and the Schmitt reference level. In the complete integrating period the integrator output should be equal to  $V_{\rm REF}$ , when the input voltage is a minimum. This time period is approximately 120  $\mu$  sec (with 20  $\mu$  sec off).

Thus

$$V_{IN}(Min) = V_{REF}/G 120.10^{-6}$$

volts.

The minimum output from the delay measuring integrator is given by:-

$$V_0(Min) = 5A.10^{-2}$$

volts.

The maximum output from this integrator must not exceed 8 volts, otherwise the amplifier will saturate; thus

$$V_o(Max) = 8 = 5A.10^{-1} \text{ volts.}$$

The gain A is thus 16, in the actual circuit the gain is nominally 20, using preferred values.

This then gives a minimum output of

$$V_{O}(Min) = 1 \text{ volt.}$$

Now  $V_{REF} \simeq 4$  volts, and hence G = 33,000.

In an attempt to improve on the 10 msec figure, stated earlier, the actual gain, on preferred values, has been set to 50.000.

The final task requires choosing suitable multipliers for the output meter. These were found experimentally and the values are given in Appendix A.

The calibration of the system requires that the component parts are functioning correctly and that the simulator has been standardised. Standardisation of the simulator infers that the position of the 50 msec delay is known accurately on the scale.

The 'Set L' arterial length control consists of a 10 turn helical potentiometer, the total output of which represents 50 cm.; the full scale reading is 100, this must be divided by 2 to obtain the arterial length in cm.

To calibrate the computer the unshaped simulator outputs are fed into the computer at the trigger points provided in the delay measuring system. The delay should be set to 50 msec, and the input to the delay-measuring integrator examined.

This output should be set to a steady d.c. value by means of the 'Set Zero' control on the 'Set L' voltage generator.

This sets the zero level of the dc woltage from the 'Set L' control to  $V_{CE}(SAT)$  to compensate for the saturation voltage of the switching transistor.

With the meter on the Xl range, the variable biasing of the emitter follower, which drives the meter, is used to set the zero position. This compensates for the offset voltage produced by the preceding circuits.

Set the 'Set L' scale to 25 cm (50 div), and with a 50 msec delay, set the meter to read 5 m/sec on the X1 range using the appropriate multiplier; then to 5 m/sec on the X5 range by adjusting the series multiplier.

This completes the callibration and the device is now ready for use. The above procedure has assumed that the integrators are functioning correctly and that the amplifiers are balanced. The balancing procedure for the amplifiers is given in Appendix A.

Fig. 3.1.

Typical Arterial Pulse Wave

## SECTION 3

#### The Pulse Wave Simulator

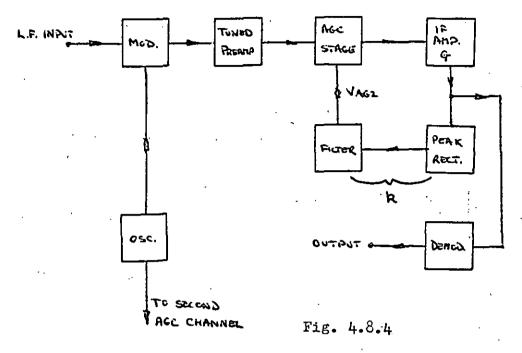

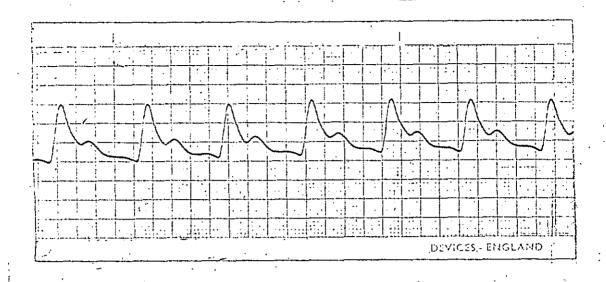

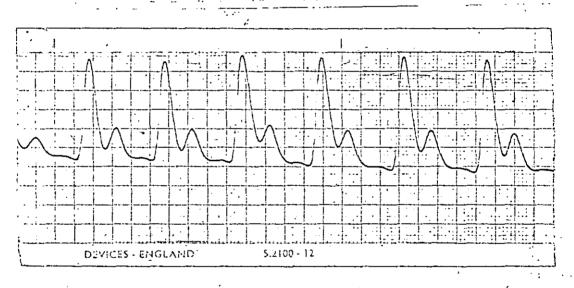

As stated in section 2, a refinement that can be used for the development and testing of the system, is that of a signal source simulator. The body is not an ideal source of signals for the development of the 'electronics', since the shape, rate, and amplitude of the signal depend upon the conditions under which the body is functioning.

The simulator will be required to give an electrical signal, which represents the transducer output under typical conditions; but is sufficiently flexible, in its design, to enable the waveform to be modified if required.

The degree to which the simulated signal compares with the real one can be found by performing a harmonic analysis on each of the waveforms, and then comparing the results.

The results from such harmonic analyses can be found in Section 6.

The basic shape of the arterial pulse wave is well established and equipment is now available on the consumer market to display pulse waves. A typical pulse wave is shown in fig. 3.1, and obviously there are many ways in which a waveform of this nature could be simulated. However, in addition to the requirements mentioned above, there are certain specific requirements here. These are that two outputs are required, one delayed by a variable amount from the other. The two channels should produce similar, or dissimilar, signals as required by the real system. The output amplitude should be

variable from zero, and independent on both channels. Also the signal should come from a low impedance source so that any kind of transducer output impedance cam be simulated. For example for a piezo-electric transducer the signal would be fed via a capacitor, of the same value as the device.

A brief survey of the methods of simulation of such a signal, bearing these points in mind should justify the use of the final system.

Both mechanical and electrical techniques are available, in this instance, due to the low frequency nature of the signal. A possible mechanical method would be to cut a cam to the required profile, and this coupled to a motor could be used to drive the wiper of a potentiometer, thus giving the required signal output. This technique does not lend itself to a second channel, delayed by a variable quantity, or to a variably shaped waveform. It could be used to give a variable frequency signal, by altering the motor speed. But, the worst case frequency, that is the lowest frequency required would be sufficient, to test the system.

Of the electrical methods of simulation, the simplest, in theory, would be to sum the various harmonic components of the signal. Variable shape could be obtained by altering the amplitude and or the phase of these components. However to produce a second waveform, with a variable delay would be extremely difficult to achieve.

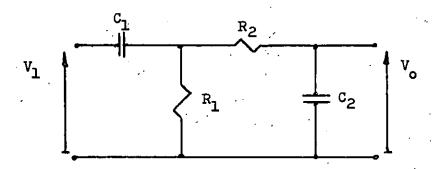

Fig. 3.2.

Exponentially Shaped Step Input

Fig. 3.3.

RC Shaping' Network

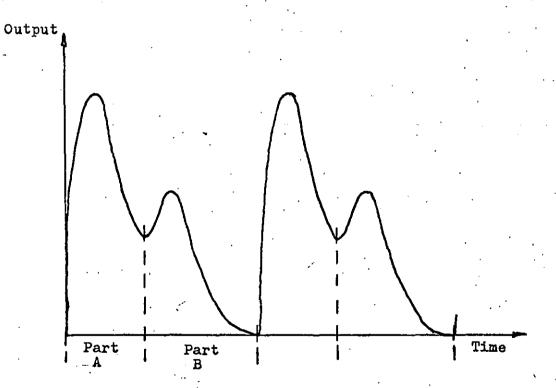

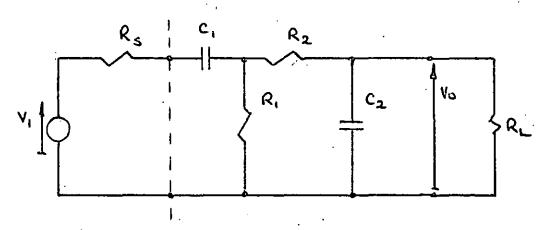

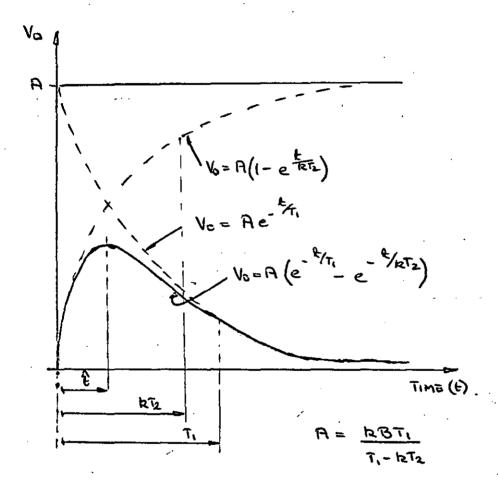

A simple, yet practical solution is to produce the waveform by shaping one or more square waves, and then adding them together. Obviously, the technique has limitations in that continuous curves are forced to be exponentials. However careful consideration of the typical pulse wave as shown in fig. 3.1.; shows that the wave consists, or could be considered to consist, of two parts, A and B in the diagram, each of which is similar in shape, there being a difference in phase and amplitude. Fig. 3.2 gives the double exponential shape produced when a step input is fed into an RC network as shown in fig. 3.3. This double exponential curve could be used to simulate part A of the pulse wave, and a similar, but delayed and attenuated signal, could be used to simulate part B.

The output could be produced by adding the signals algebraically, or by switching the output from one waveform to the other. The latter technique has been adopted since the two parts are then completely independent of each other. The circuit used to perform this switching is described in Section 4.6, and it is sufficient to say here that the 'Analogue Gate' requires switching signals, from low impedance sources, of both polarities. The analogue input is required to be of a small amplitude, less than 500mV, and appear from a source with a quiescent dc level that is negative by approximately 1 volt with respect to earth.

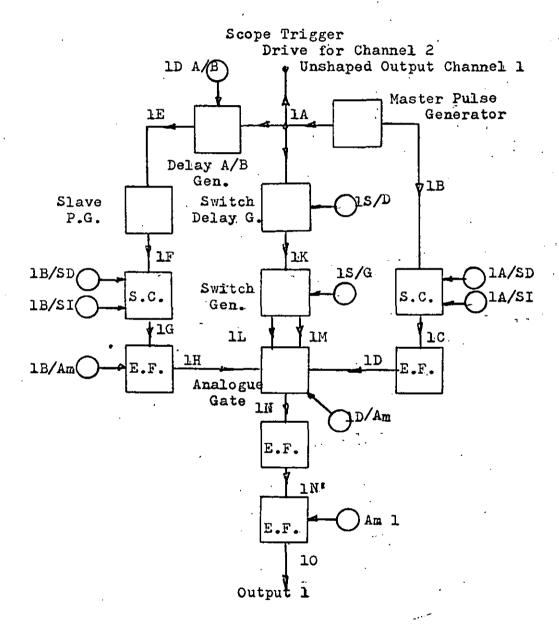

Fig. 3.4.

Pulse Wave Simulator Channel 1 Block Diagram

Fig. 3.6

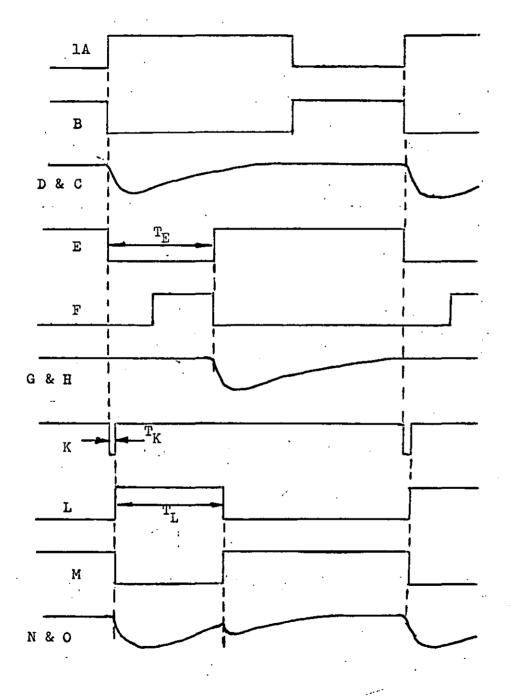

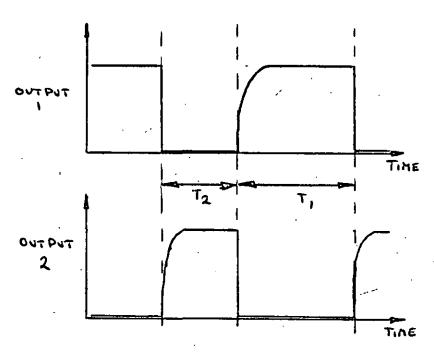

Simulator Waveforms for Channels 1 and 2

Fig. 3.7.

Attenuating Emitter Follower Circuit.

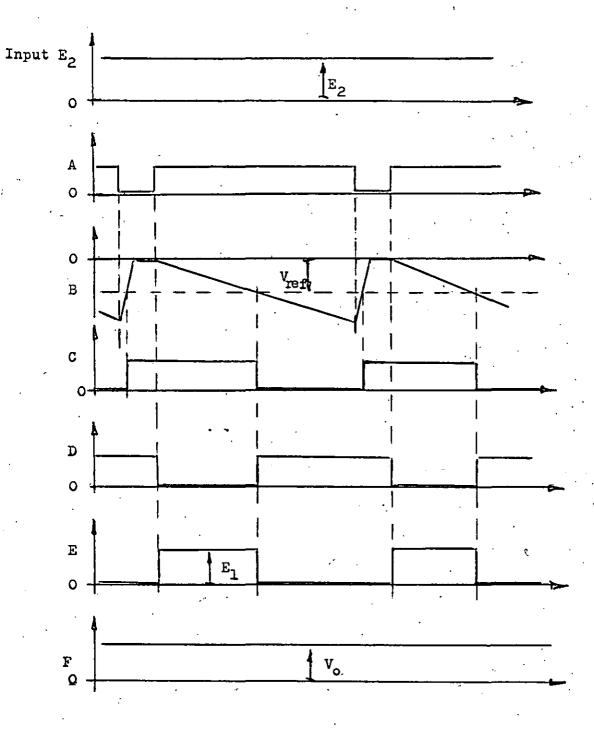

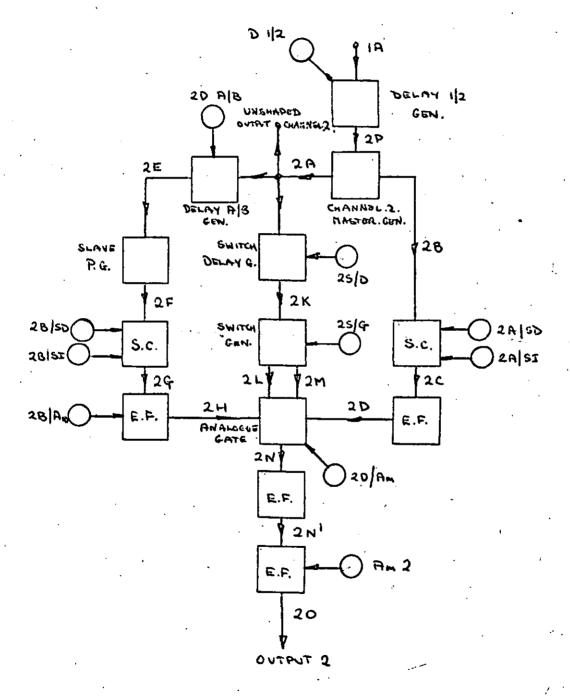

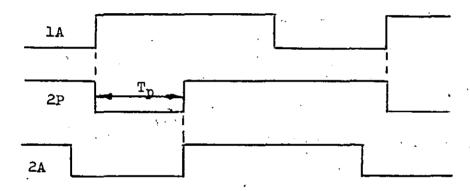

The simulator is timed by a master astable pulse generator, which is set to standard heart rate, and provides the step from which part A of the waveform is generated. In addition it triggers a delay generator from which a slave pulse generator is driven. This slave generator provides the signal from which part B of the waveform is produced. Note that the delay (A/B) generator cannot be used to produce part B of the waveform directly, since it has been found desirable to 'overlap' the waveform at both ends. The output from the master and slave generators are then fed into shaping circuits as discussed previously. Reference should be made to fig. 3.6, where the waveforms for the complete system, as shown in fig. 3.4, are given. The master generator output is given in its normal and inverted forms, as waveform A and B, and the shaped signal is produced from the B waveform and is shown as waveform C. The delay A/B generator produces waveform E, and from this the slave generator is triggered. The shaped output used to generate part B, of the waveform is shown on waveform G.

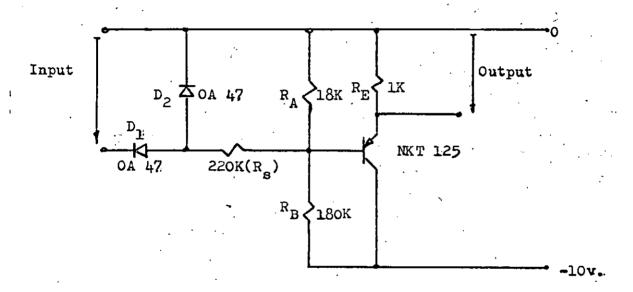

To make these shaped waveforms compatible with the input requirements of the Analogue Gate, requires that they are attenuated and biased to approximately -lvolt. This is achieved by using the emitter follower circuit as shown in fig. 3.7, the diodes D<sub>1</sub> and D<sub>2</sub> accept only the negative going signal from the shaping circuit and clamp the quiescent dc level to earth. The signal is attenuated by the divider formed by the series resistor and the input impedance of the emitter follower stage.

The dc conditions are set up by the bias applied to the emitter follower.

For the B part of the waveform, a variable amplitude is obtained by replacing the emitter resistor by a potentiometer, and taking the output from the wiper.

The output is taken from the Analogue Gate by using a high input impedance emitter follower, to avoid loading the gate. This is then fed into a second emitter follower to give a low output impedance. A variableamplitude output is obtained as above. The first emitter follower has a large capacitor across the emitter resistor, which acts as a low pass filter and prevents any discontinuities in the waveform appearing on the output.

The switching signals for the analogue gate are shown as waveforms L and M in fig. 3.6. These are derived from the two sides of a pulse generator which is driven by the master generator via a delay stage as shown. To provide a low output impedance this generator has 680\$\Omega\$ collector loads.

This gives the basic single channel system, the location of the various variable controls are shown on the system diagram. The period  $\mathbf{T}_E$  is a variable, controlled by the delay A/B generator. The shaping circuits have both their resistive components variable to enable the signal shape to be  $\infty$  ntrolled (See Appendix D). The periods  $\mathbf{T}_k$  and  $\mathbf{T}_L$  are both variable so that any desired proportion of A to B can be selected.

The overall amplitude, and the amplitude of the B part of

Fig. 3.5.

Pulse Wave Simulator Channel 2 Block Diagram

Fig. 3.8.

Simulator Waveforms for Channel Delay Production

the waveform are variable, and to facilitate balancing of the two parts of the waveform the Analogue gate incorporates a differential level shifting control.

For a second channel, which is delayed from the first by a variable quantity, it is only necessary to duplicate the original system and replace the astable master generator by a monostable master generator. This generator is then driven from the master generator via a variable delay stage. Thus a continuously variable delay is achieved, and the two output waveforms can be made similar, or dissimilar as required, by using the variable controls.

The system diagram for the second channel is shown in fig. 3.5, and in general the related waveforms are similar to those for Channel 1, those waveforms which are different, are given in fig. 3.8.

The Simulator provides the facilities which are listed below:-

- (1) Both simulated outputs are available from a low impedance source and short circuit protection is provided.

- (2) Waveform 1A is provided as a scope trigger signal.

- outputs, which can be used to drive the simulator

via the inputs provided after the exponential amplifiers,

for calibration purposes. Also these waveforms can

be used as start and stop signals to a counter to

enable the delay to be measured accurately for

standardisation.

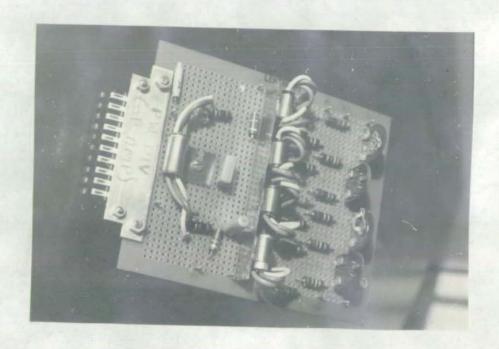

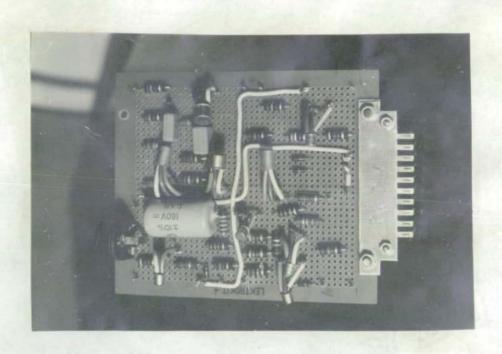

The simulator construction incorporates its own power supplies and uses plug-in boards. The amplitude controls for both channels and the delay control are mounted on the front panel. All the other variable controls use skeleton potentiometers and are mounted on the rear edge of the plug-in boards. Full circuit diagrams, photographs and wiring details of the Simulator are given in Appendix B.

Copies of the waveforms produced by the simulator can be found in Section 6.

This simulator has been constructed using pnp transistors operating between earth and -10 volts, and thus a negative going output is provided. The exponential amplifiers are however designed to operate from a positive going signal. Thus to invert the output a special phase correcting amplifier has been designed and it is described in Section 4, with the design of the various other components in this system.

#### SECTION 4

### Design Considerations and Procedures

#### Introduction

In the following sub-sections of this section, the design of the various circuits discussed in the thesis, is given.

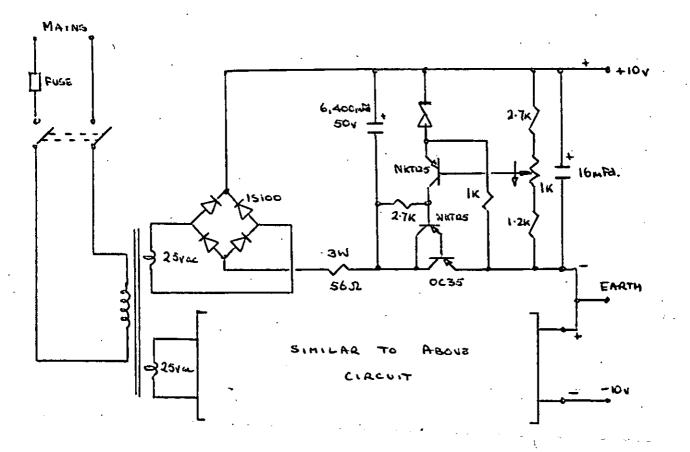

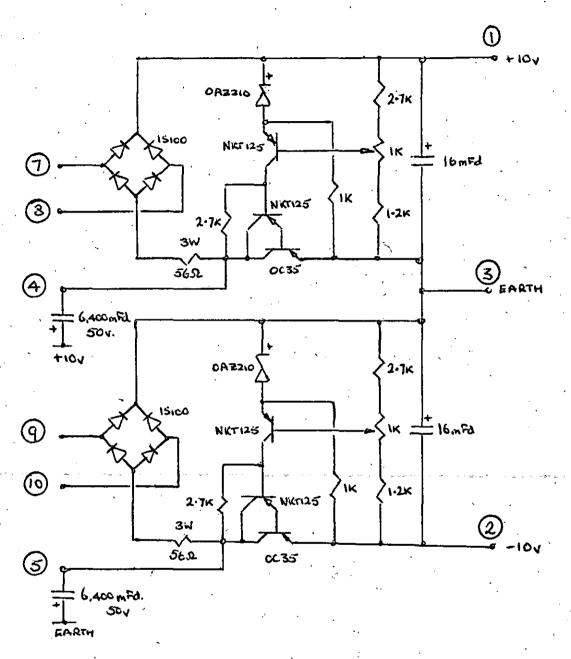

In all cases the circuits have been designed to operate from either + or - 10 volt rails, or both. The power supplies are described in sub-section 11.

In certain cases; for example gates, pulse generators etc, a pnp circuit is used in one instance, and an npn circuit is used in another. The design here considers only the npn case, since the pnp circuit can be obtained by inverting the polarity of any diodes in the circuit, and replacing the +10 volt rail by the -10, and vice versa.

### Section 4.1

# Operational Amplifier Design

For a dc amplifier to perform successfully as an operational device its performance must conform to the specification shown below:-

- 1. Very large internal voltage gain.

- 2. High input impedance.

- 3. Low output impedance.

- 4. Both input and output should have quiescent dc. levels at earth potential.

Fig.4.1.1

Dc Amplifier.

Fig. 4.1.2

DC Amplifier.

Fig. 4.1.3

DC Amplifier.

- 5. The dc operating points and gain should be stable with temperature.

- 6. The amplifier should have a bandwidth suitable to the application intended.

Experience shows that the above requirements are conflicting in nature, and that the final design must, as always, be a compromise.

The temperature sensitivity can be reduced to a minimum by using all silicon semiconductors. Obviously the circuit will require more than one stage of amplification and some form of dc coupling, between the stages, will be required.

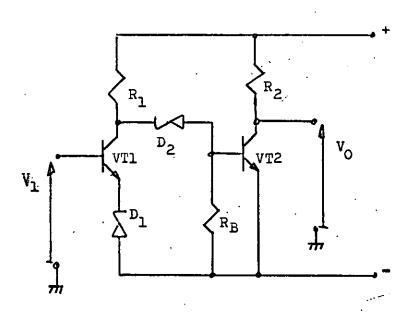

The circuit given in fig. 4.1.1. gives a possible form of coupling, that will enable the zero input/output condition to be satisfied, but the undecoupled emitter resistor, and the resistive divider chain limit the gain. These components can be replaced by zener diodes as in fig. 4.1.2. which will give the required level shifting, without the degeneration, given by their resistive counterparts. Another modification is to replace the second transistor by its complement, that is pnp for npm, as shown in fig. 4.1.3., this eliminates the resistor R<sub>B</sub>.

However the circuit now relies on the dc shift produced by the zener diodes for its operation. This voltage is temperature sensitive, and leads to poor temperature stability,

Fig. 4.1.4

DC Amplifier.

in a circuit where discrete circuit components are used. This would not necessarily be the case in an integrated circuit (57).

Thus an alternative approach must be adopted and there are two basic methods available. These being a chopper stabilised amplifier and a differential amplifier.

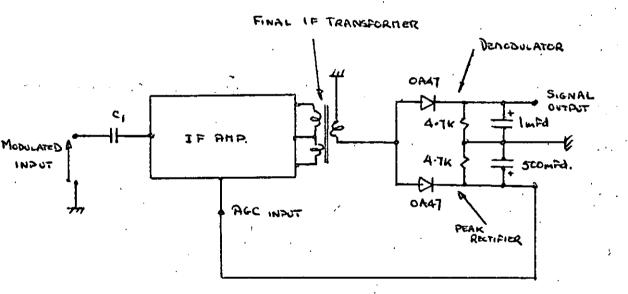

In the chopper stabilised amplifier (47), (58) the input signal is modulated, by using a chopping device, and the chopped signal is then amplified in an ac coupled amplifier. The amplified carrier signal is then demodulated to give the output. In this way an extremely large gain can be achieved with excellent temperature stability.

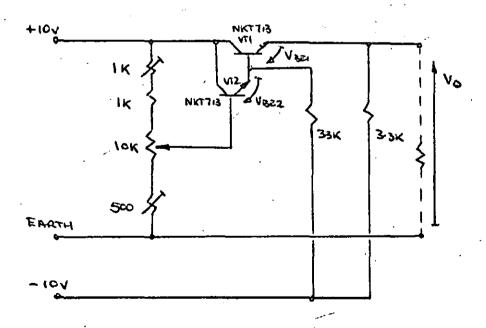

However in this work it was decided to use a differential amplifier (55), (56) since the gain with two differential stages can easily be made in excess of 1,000, which is considered to be large emough for this application.

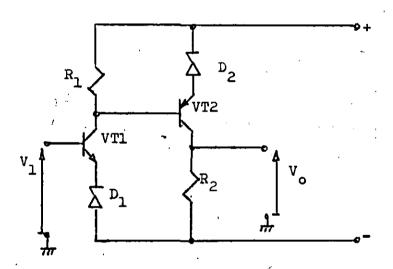

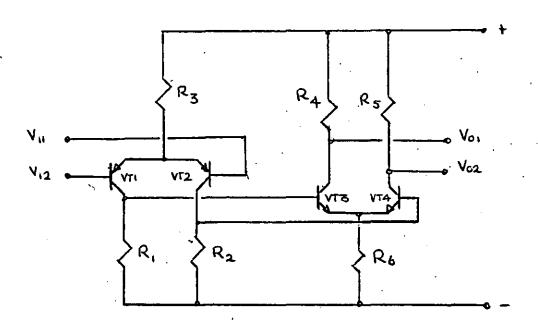

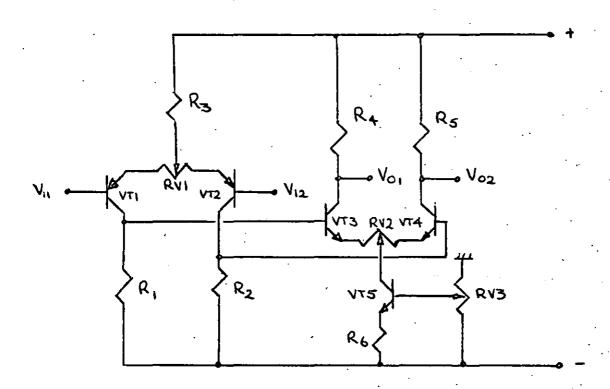

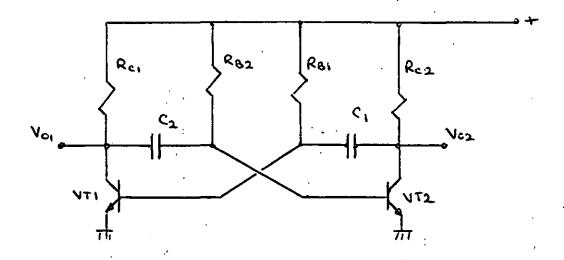

The basic circuit diagram of a two stage differential amplifier is shown in fig. 4.1.4., and to achieve the zero input/zero output condition a pnp stage is followed directly by an npn stage, as in the manner of the single ended amplifier in fig. 4.1.3. The input is applied across the bases, and in true differential applications, the output is taken from the collectors of VT3 and VT4.

Fig. 4.1.5.

DC Amplifier.

If the differential pair are similar, both electrically and thermally, drift due to temperature variation will be equal on both sides and will not affect the relative states of the transistors. Also the drift produced by the pnp pair will tend to be compensated for by the drift of the npn pair.

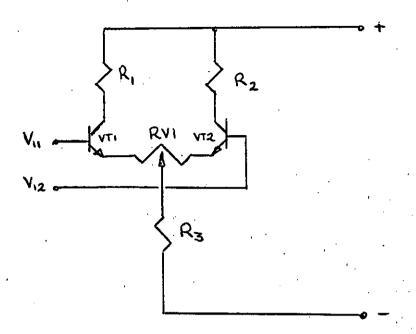

In practice the transistors can be made similar thermally by clamping them in the same heat sink, but they must be matched, or compensated, to achieve similar electrical operation. The compensation normally takes the form of a small potentiometer inserted in series with the transistor emitters, as shown in fig. 4.1.5. This enables the two transistors to be balanced, provided that they are matched for gain. The resistance inserted also produces a small degree of feedback, which both stabilises the gain and increases the input impedance.

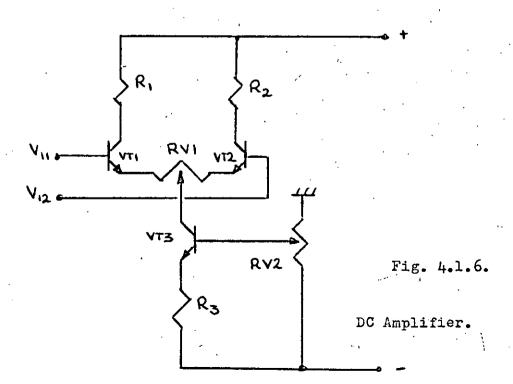

It can be shown to be desirable, (52) to make the tail resistor as large as possible, since this will then approximate to a constant current source, which is the optimum. As a rule of thumb, it cam be said, that for stability,  $R_3$  should be greater than, or equal to  $R_1$  (or  $R_2$ ). This is not always possible, due to the limitations set by the voltage rails, and in these cases, the tail resistor can be replaced by a transistor acting as a constant current source, as shown in fig. 4.1.6. For constant current operation the transistor must be biased into its linear region and supplied with a constant base current. This will produce a constant collector current set by the gain of the transistor. The biasing is produced by  $R_3$  and potentiometer

Fig. 4.1.7

DC Amplifier

Fig. 4.1.8

# DC Amplifier Final Circuit.

| R <sub>1</sub> . | 2°2M | R9                | :<br>10K | • | VTl  | 00202  |

|------------------|------|-------------------|----------|---|------|--------|

| R                | 560K | R <sub>10</sub>   | lok      |   | VT2  | V405   |

| R <sub>3</sub>   | 22K  | R <sub>11</sub>   |          | _ | VT 3 | V405   |

| R <sub>4</sub>   | 560K | R. a              | lK       |   | VT4  | BSY95A |

| R <sub>5</sub>   | lok  | 12<br>R <b>V1</b> | •        |   | VT5  | BSY95A |

| R <sub>6</sub>   | lok  | RV2               |          |   | VT6  | BSY95A |

| R <sub>7</sub>   | lok  | RV3               |          |   | VT7  | BSY95A |

| R <sub>8</sub>   | 27K  | RV4               | -        |   | :    | -      |

Fig. 4.1.9

Component values in above fig.

RV2, as shown.

Variation of the setting of RV2 will alter the base and collector currents, and can thus be used to set the dc operating conditions for VT1 and VT2.

A two stage differential amplifier with the refinements considered is shown in fig. 4.1.7., but as yet it does not conform to the specifications required for an operational device. Since the operational amplifier is basically single-ended, true differential operation cannot be applied. One of the input bases must be grounded and this is done via a suitable resistor. This gives a single ended input, with respect to earth, and an input impedance of approximately the grounding resistor. The amplifier is required to be inverting and thus this determines the cutput that is taken.

High input and low output impedances are provided by emitter followers at both ends of the basic circuit. The input circuit has variable biasing to enable the zero input condition to be set. The zero output is set, as described earlier, by the variable biasing in the constant current driver circuit.

The final circuit for the operational amplifier is shown in fig. 4.1.8., and a list of component values is given in fig. 4.1.9. The amplifier was designed to have a standing dc current in VT2 and VT3 of  $\frac{1}{2}$  mA, with a collector-emitter

voltage of 6 volts. The standing current in VT4 and VT5 is 1 mA with a collector-emitter voltage of 8 volts.

The measured performance of the amplifier is given below:-

Voltage Gain > 1,000

Input Impedance > 600 k 1

Output Impedance < 500 \$\mathcal{I}\$.

Bandwidth > 400 kc/sec

Fig. 4.2.1

Integrator Resetting Gate

Fig. 4.2.2

Gate Drive for above fig.

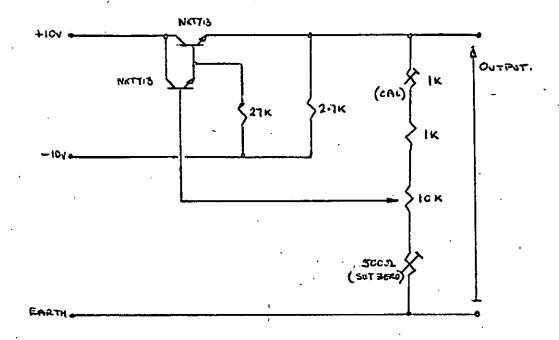

#### Section 4.2

#### Integrator Resetting Gate Design

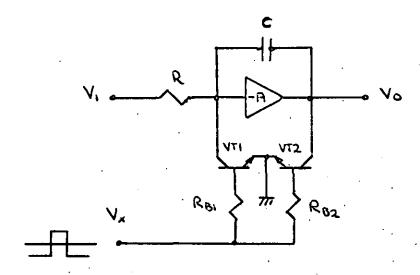

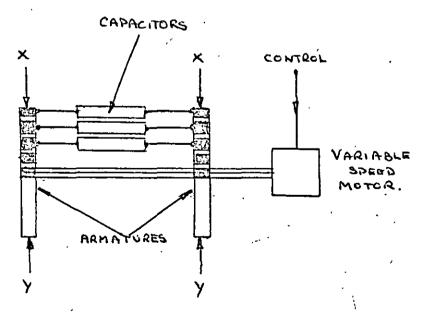

In the previous section a dc amplifier suitable for operational applications has been developed. However, for the applications intended, this amplifier will be operating as an integrator, which requires resetting to its initial conditions electrically. The method usually applied on analogue computers is to use electromechanical relays for resetting, but the analogue division system operates the integrator at a high repetition frequency, and conventional relays could not operate fast enough. A reed-relay would be a possibility, but another solution which appears to give satisfactory results has been used.

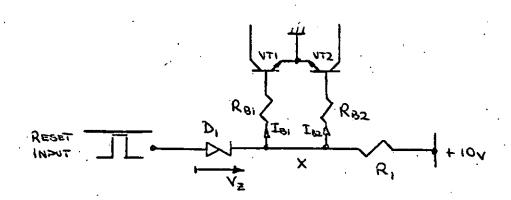

is zero, that is a fully discharged capacitor. This simplifies the problem in that no initial charge has to be set on the capacitor. Consider the configuration as shown in fig. 4.2.1, with the transistors biased off the arrangement is a simple integrator, since the transistors will appear as a large, ideally infinite, impedance across the capacitor. If silicon transistors are used the leakage current will be very small.

When the transistors are turned on, the capacitor will discharge since both ends are tied to earth via a low impedance.

The time taken to discharge the capacitor is determined by the base current provided. Consider the circuit in fig. 4.2.2., this is the method used to provide the switching signal  $V_{\chi}$ .

since the integrator is an inverting device a positive output indicates a negative input and thus the derived reset pulse appears as a positive going pulse between. -10 and earth, and thus requires level shifting which is achieved by the Zener diode.

If the source impedance of this pulse is  $R_S$ , then as far as the transistors are concerned the signal appears to be a pulse of approximate amplitude  $V_Z$  from a source impedance of  $R_S$  and  $R_S$  in parallel.

Thus the total base current 2I<sub>B</sub> will be given approximately by:-

$$2I_B = (V_Z - V_{BE})/R_1 liR_s + R_B/2$$

If this current flows for a time, t, then the charge removed from the capacitor by the resultant collector current will be approximately

$$Q = I_B h_{FE} t$$

But the initial charge on the capacitor is given by  $Q = CV_{\mathbb{C}}$ . Thus equating these two figures gives:-

$$t = \frac{c \ V_c}{I_{B}h_{FE}}$$

or t =

$$\frac{2C V_c \left[R_s 11R_1 + R_B/2\right]}{\left(V_z - V_{BE}\right) h_{FE}}$$

A knowhedge of the maximum voltage to which the capacitor will charge, its value, and the other circuit parameters can then be used to predict the discharge time for a given base resistor.

However the value taken for  $h_{\mbox{\it FE}}$  must be investigated, since at the end of this discharge this must fall from its normal value due to the transistor characteristics.

In practice the values have been found empirically, but the results fit reasonably with the above theory.

For example for the analogue divider system, typical values are:-

$$C = 0.01 \text{ mFd}$$

$$(R_s ll R_l + R_B/2) \le 3K\Omega$$

$$V_Z - V_{BE} \ge 5 \text{ volts}$$

$$V_c \le 8 \text{ volts}$$

Thus assuming an h<sub>FE</sub> of 50 gives a discharge time of approximately 2 usec, which is of the order of the discharge times obtained experimentally.

The component values in the actual circuits cam be found by reference to the full circuit diagrams for the computer, given in Appendix A.

Fig. 4.3:1.

Simple DC Amplifier

Fig. 4.3.2

Simple Operational Amplifier

### Section 4.3

# Simple Operational Amplifier Design

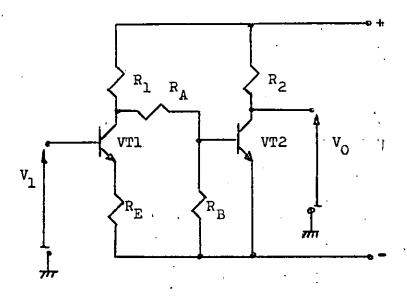

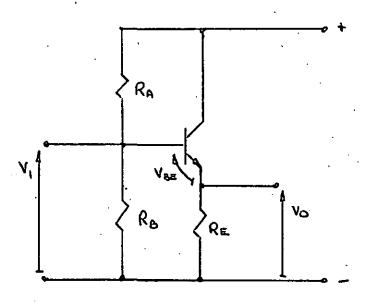

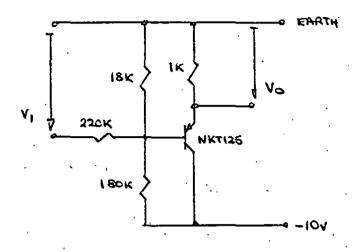

In certain applications it is necessary to perform an analogue function, to a minimal accuracy, over a limited range of input conditions. The use of the operational amplifier as described in Section 4.1, would be expensive and unnecessary. In this case a simple one transistor inverting amplifier has been designed to perform the function.

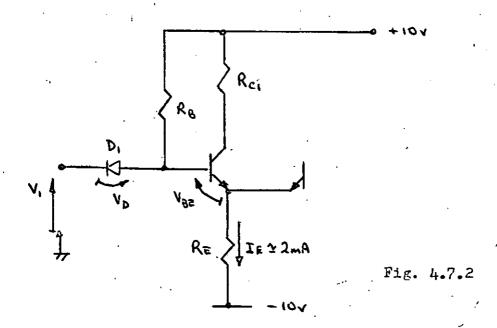

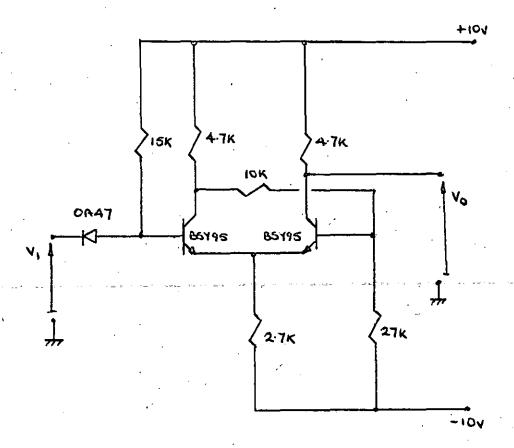

The basic circuit is shown in Fig. 4.3.1 and is extremely simple in design. The base resistor  $R_{\rm B}$ , provides the dc biasing and also the required feedback. The nominal values of  $R_{\rm B}$  and  $R_{\rm C}$ , as shown give a typical amplifier performance as shown below:-

Voltage Gain 150

Input Impedance  $1K\Omega$

Output Impedance 10KA

Quiescent dc output + 3 volts

Quiescent dc input +0.5 volts

When patched as an operational amplifier as shown in fig 4.3.2, the theoretical transfer function becomes:-

$$\frac{\Lambda^{J}}{\Lambda} (b) = \frac{\Xi(b)}{\Lambda}$$

However if a simple voltage amplifier is required, the gain is set by making  $\Xi(p)$  purely resistive or zero.

# Section 4.3.1

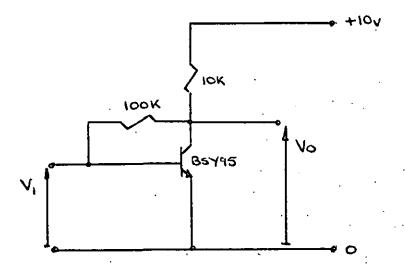

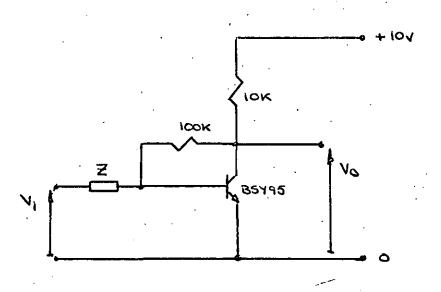

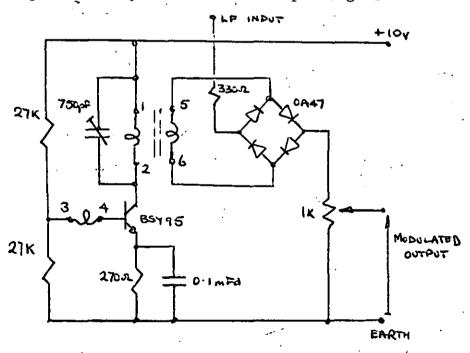

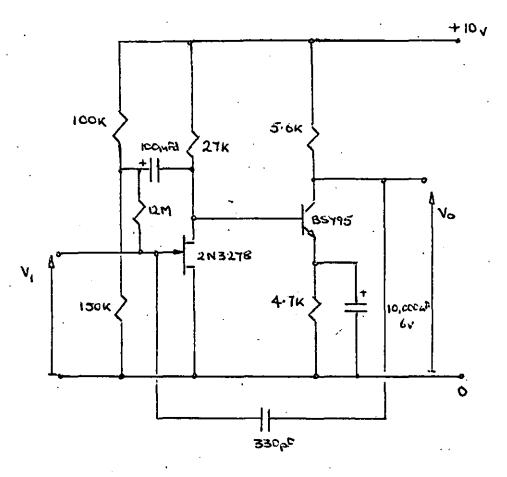

### The Exponential Amplifier

In the exponential amplifier, the impedance Z (p) is that of a forward biased silicon junction diode. The diode has an exponential characteristic which is given, theoretically by:-

$I = I_0(\exp(qV/nkT)-1)$  (See Appendix C)

In practice silicon dies obey this law over a limited operating range. However, if a small area junction device, such as the Mullard SX630, is used then the law is obeyed over an increased operating range.

The dc resistance of the device is given by:-

$$R_D = V/I = V I_O(\exp(qV/nkT)-1)$$

Hence the theoretical transfer function for the exponential amplifier becomes:-

$$V_o/V_1 = R_B/R_D = R_BI_o(exp(qV_1/nkT)-1) V_1$$

Hence  $V_o = R_B I_o (\exp(qV_1/nkT)-1)$  or  $V_o = A(\exp(BV_1)-1)$

Where  $A = R_B I_O$  and B = q/nkT:

The diode manufacturer's quote typical figures for  $I_o$  and

Fig. 4.3.3

3 Stage Exponential Amplifier

Fig. 4,3.4

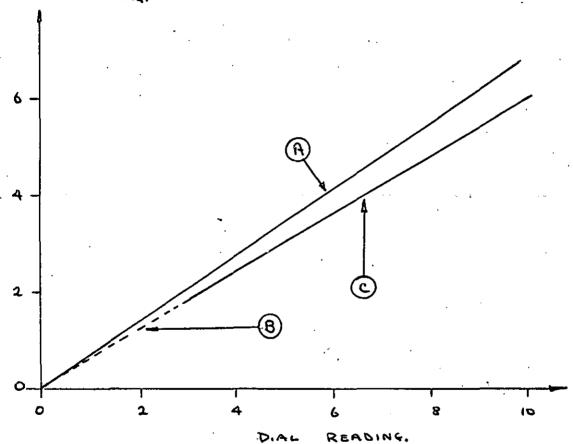

Exponential Amplifier Characteristics

as 10<sup>-10</sup> and 23 respectively. Also that the device will nkT obey the theoretical law over an input voltage range of 0.2 to 0.7 volts. Thus this automatically limits the range over which the amplifier can function.

With  $V_1$  = 0.2 volts, the quantity  $e^{BV_1}$  becomes approximately 100. Thus to accuracy better than 1% the -1 in the original expression can be ignored, thus giving a transfer function of:-

$$V_O = A e^{BV_1}$$

Where  $A = 10^{-5}$  and B = 23

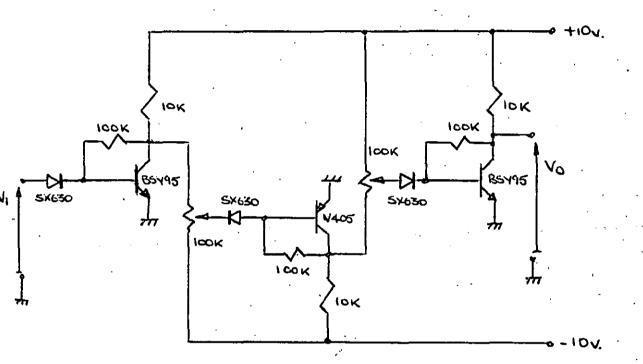

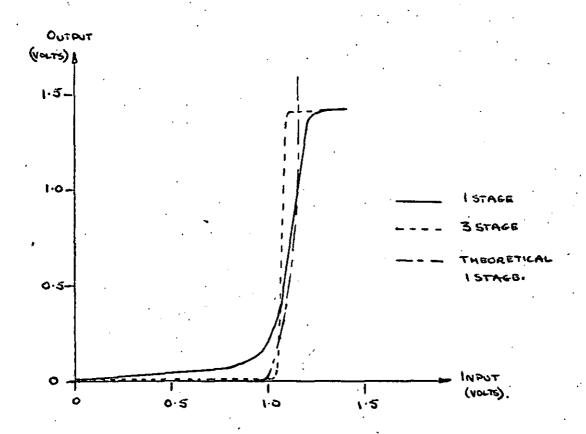

In practice it has been found that three stages of exponential amplification are required to give the desired accuracy.

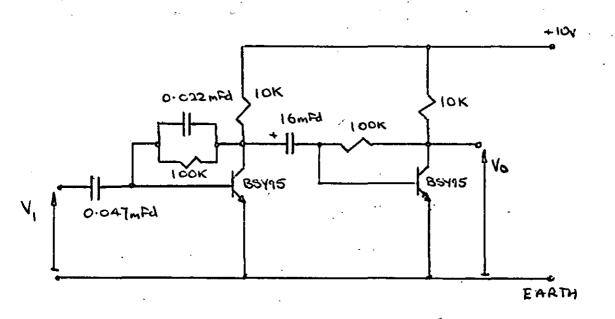

To achieve this two npm stages are interposed by a pnp stage. The coupling between stages is via a 100K potentiometer which serves to attenuate the signal to the required amplitude and also provide the required dc level on the output. The complete circuit of the three stage amplifier is shown in fig 4.3.3.

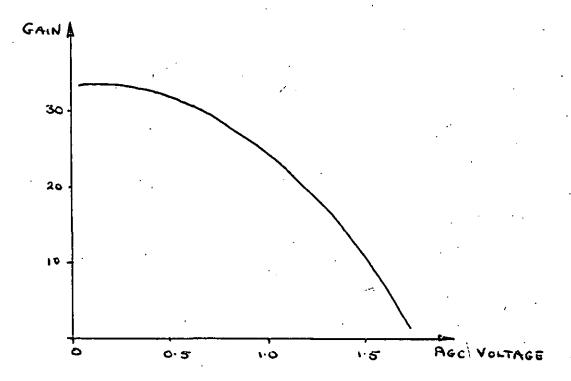

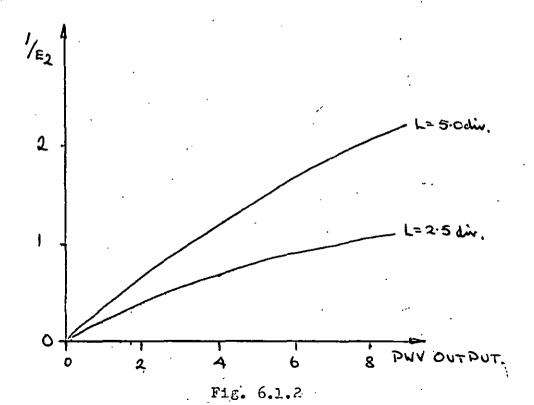

Typical input/output characteristics for a single stage and a 3 stage amplifier are shown in fig. 4.3.4. In addition the theoretical transfer characteristic for the single stage is included. The curves have been drawn with a static dc output of zero, only for the purposes of comparison.

Fig. 4.3.5

Differentiator Characteristics

## Section 4.3.2

## The Differentiator

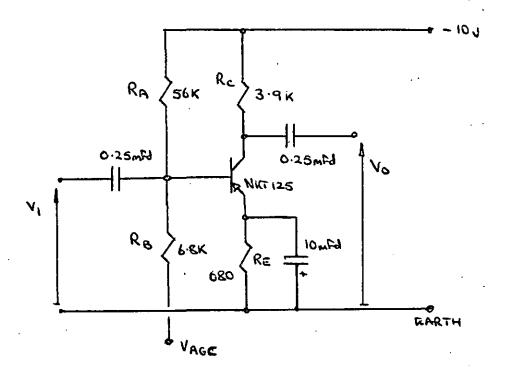

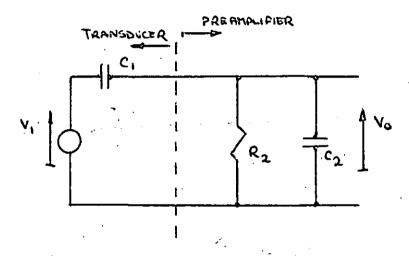

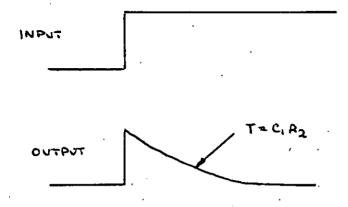

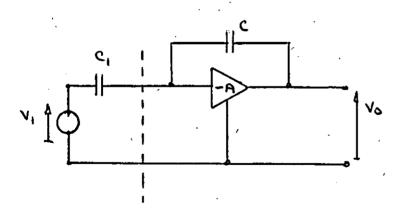

If the input impedance Z(p) is a capacitor, of value C, then the function the amplifier performs is that of differentiation. The theoretical transfer function will become:-

$$\frac{V_0}{V_1}(P) = \frac{R_B}{1/PC} = PC R_B$$

where  $\mathbf{p}$  is the Laplacian operator. Hence differentiation with a gain set to  $CR_{\mathbf{p}}$ .

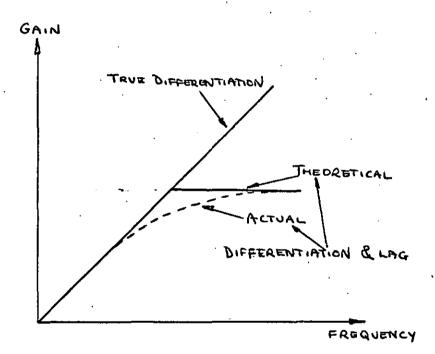

However when a typical analogue signal is differentiated in this manner it invariably becomes 'noisy' and the circuit tends to be unstable. This is because there is a linear relationship between gain and frequency in a differentiator, as shown in fig 4.3.5. Thus any high frequency noise present will be amplified many times and this has an adverse effect on the signal to noise ratio for the signal.

However if the function is modified, by the inclusion of a lag in the system, as shown in fig. 4.3.5, the gain above the breakpoint frequency is constant, and then any high frequency noise present will be amplified, but not to the same degree as in the pure differentiator.

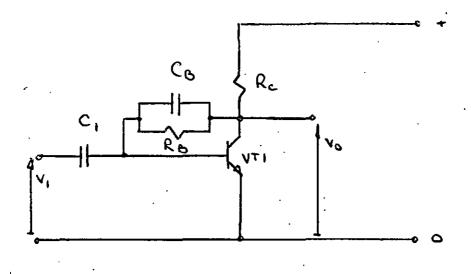

The signal to noise ratio of the signal is affected but not as badly as previously. The lag can easily be introduced by placing a capacitor  $C_B$  in parallel with the resistor  $R_B$ , as

Fig. 4.5.6

Differentiator & Lag Circuit Diagram

Fig. 4.3.7

Complete Circuit for Differentiator

shown in fig. 4.3.6. This arrangement has a theoretical transfer function of:-

$$V_o/V_1(\rho) = \rho CR_B/(1 + \rho C_B R_B)$$

.

The breakpoint frequency,  $f_1$ , is given by

$$f_1 = 1/2\pi \cdot C_B R_B$$

In the actual system it has been found that the 'high frequency' noise is at 100 c/s, and is thus from the power supplies. To remove this adequately a suitable cut-off frequency has been found to be 70 c/s, which, as a preferred value, makes  $C_{\rm R}$  = 0.022 mFd.

For efficient differentiation a maximum value of input capacitor, C, was found to be 0.047 mFd. This, however, did not give sufficient gain for the output signal to drive the trigger circuit directly, and thus a voltage amplifier was added. This amplifier is of the same design as the basic operational amplifier, and is ac coupled to the output of the differentiation stage.

The final circuit of the differentiator stage is shown in fig. 4.3.7.

Fig. 4.4.1

Basic Astable Pulse Generator

Fig. 4.4.2

Outputs from above Circuit

Fig. 4.4.3

Modified Astable Pulse Generator

### Section 4.4

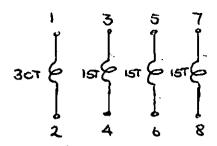

### Astable and Monostable Pulse Generator Design

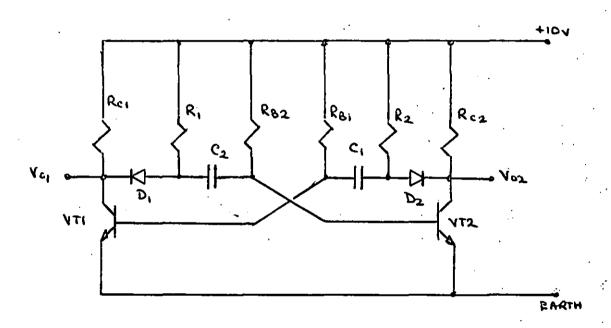

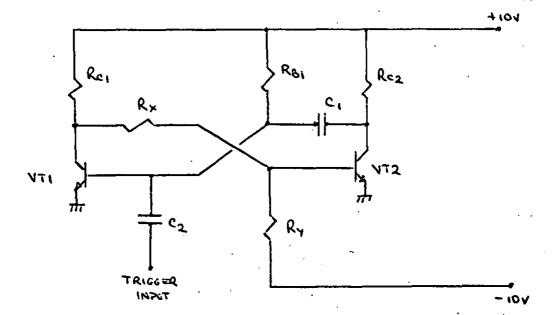

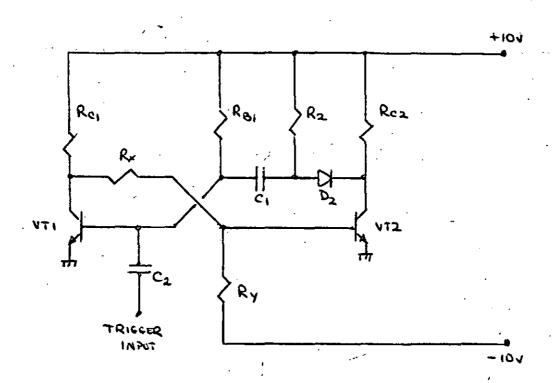

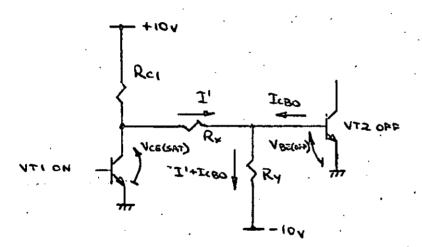

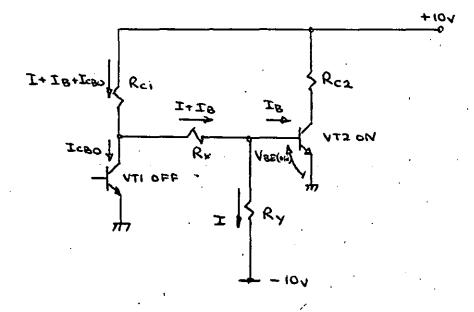

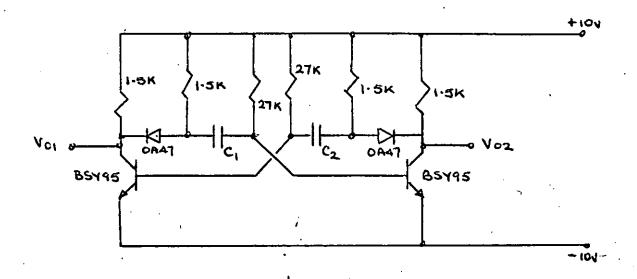

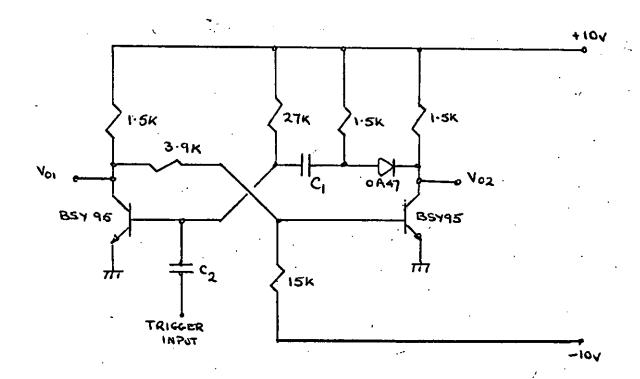

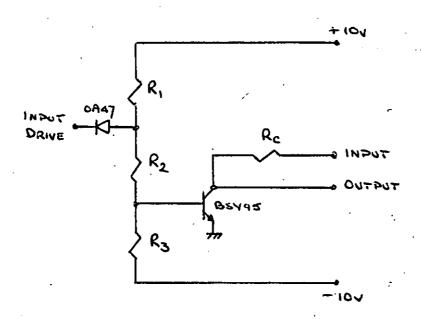

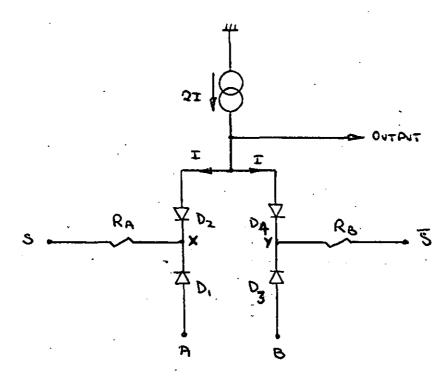

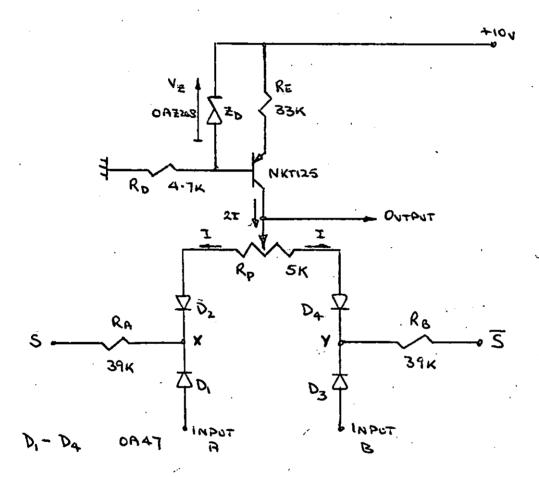

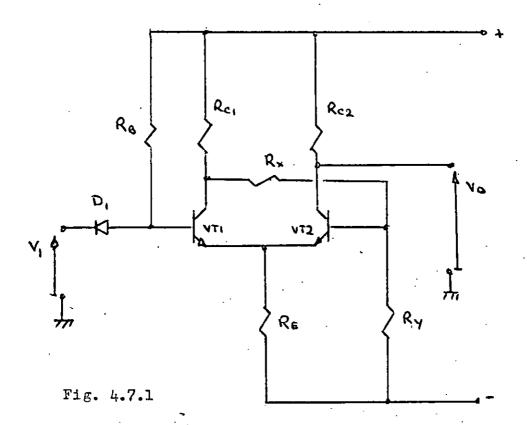

In both the computer and the simulator astable and monostable pulse generators are used. The circuitry is conventional, and of the collector/base coupled configuration, with RC timing circuits. The basic astable circuit is shown in fig. 4.4.1, either output is available and their polarities are shown in fig. 4.4.2.